FPGA的BRAM和LUT等資源都是有限的,在FPGA開發過程中,可能經常遇到BRAM或者LUT資源不夠用的情況。

一般建議BRAM和LUT資源的消耗不要超過80%,當然高端一點的FPGA芯片也可以放寬到90%,超過這個限制,可能就會出現時序違例較嚴重的情況,導致上板運行出現異常的情況。

今天分享一下BRAM資源使用優化策略,以Vivado的 Block Memory Generator為例 。

1、Distribute BRAM或URAM 替代BRAM

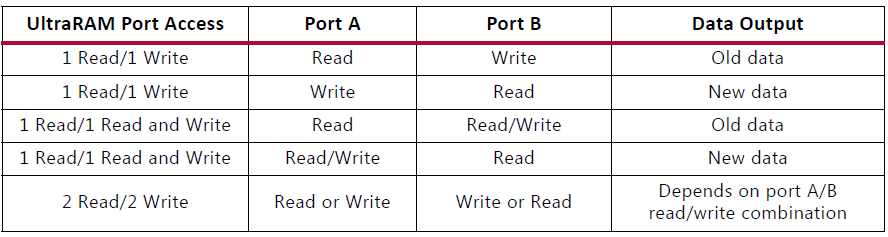

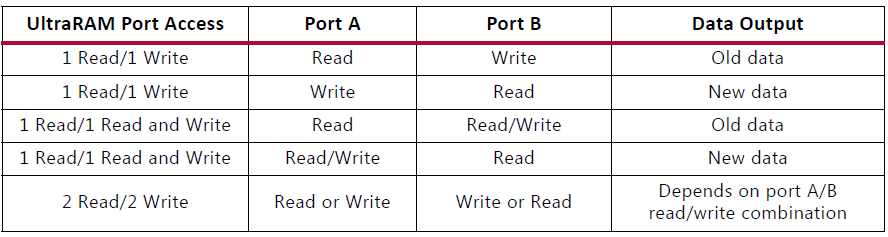

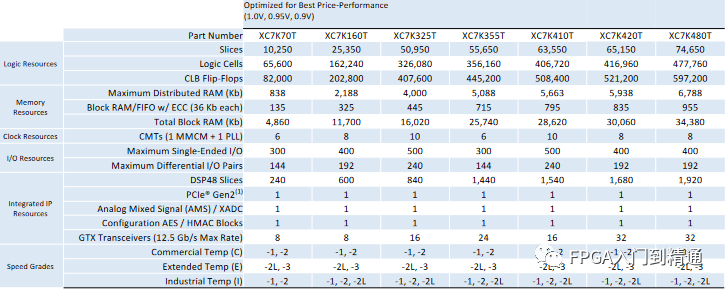

存儲深度和寬度較小,且LUT資源或URAM有富裕,可以用“Distribute BRAM”或“URAM”來替代。

這里需要注意使用的FPGA芯片型號,是否帶URAM資源。

- (* ram_style = "block" *)表示用Block RAM實現

- (* ram_style = "reg" *)表示用寄存器實現

- (* ram_style = "distributed" *)表示用分布式 RAM實現

- (* ram_style = "uram" *)表示用uram實現

這里給出代碼示例:

// FPGA 雙口 RAM

module dual_port_ram(

input clk,

input [7:0] data_in,

input [5:0] wr_addr,

input wr_en,

input [5:0] rd_addr,

output reg [7:0] data_out

);

// 聲明雙口 RAM 存儲器

(* ram_style = "block" *)reg [7:0] ram[63:0];

// 時鐘上升沿寫入

always @(posedge clk) begin

if (wr_en)

ram[wr_addr] <= data_in;

end

// 讀取;

always @(posedge clk) begin

data_out <= ram[rd_addr];

end

endmodule

2、雙口ROM替代單口ROM

如果工程中,有兩個以上的ROM或RAM使用的是相同的數據,可以使用雙口替代單口模式,資源消耗是一樣的,這樣就可以節省一個或多個ROM IP。

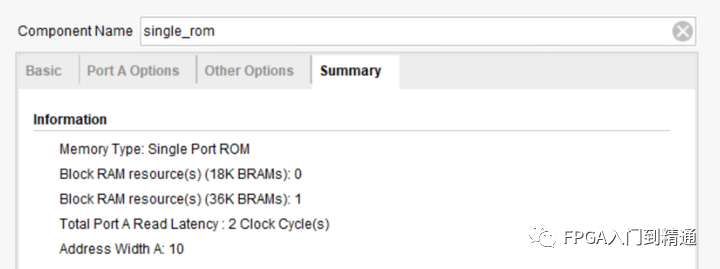

這里對比一下“數據寬度為32,存儲深度為1024”的單口和雙口模式下的資源消耗。

3、合理的數據寬度和深度設置

要想FPGA BRAM資源消耗優化,更關鍵的是優化FPGA工程的緩存大小設計,計算理論上緩存數據的位寬和最大深度,選擇出合適的參數。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636197 -

芯片

+關注

關注

463文章

54007瀏覽量

465889 -

ROM

+關注

關注

4文章

579瀏覽量

89064 -

資源

+關注

關注

0文章

59瀏覽量

18402 -

BRAM

+關注

關注

0文章

43瀏覽量

11655

發布評論請先 登錄

相關推薦

熱點推薦

【FPGA ZYNQ Ultrascale+ MPSOC教程】33.BRAM實現PS與PL交互

有時CPU需要與PL進行小批量的數據交換,可以通過BRAM模塊,也就是Block RAM實現此要求。本章通過Zynq的GP Master接口讀寫PL端的BRAM,實現與PL的交互。在本實驗中加入了自定義的FPGA程序,并利用AX

FPGA資源優化方法

各位大神,小弟最近在做一個項目,由于之前選用的FPGA資源不夠,現在需要將程序的資源占用率降下來。經過我的冥思苦想,也找不到好的方法,不知道各位大神平時工作中降低資源利用率的方法有哪些

發表于 04-04 00:32

【InTime試用體驗】使用簡易、策略選擇精確度高的一款時序優化軟件

解決FPGA時序優化問題的軟件。InTime 內嵌學習引擎,可以智能分析FPGA設計,為綜合和布局布線提供更優的策略組合。同時,根據對器件、設計和工具特點的了解,以及獨有的算法,InT

發表于 07-05 11:00

FPGA實現基于Vivado的BRAM IP核的使用

的使用。 ? ? BRAM是FPGA定制的RAM資源,有著較大的存儲空間,且在日常的工程中使用較為頻繁。BRAM以陣列的方式排布于FPGA的

使用FPGA調用RAM資源的詳細說明

FPGA可以調用分布式RAM和塊RAM兩種RAM,當我們編寫verilog代碼的時候如果合理的編寫就可以使我們想要的RAM被綜合成BRAM(Block RAM)或者DRAM(Distributed

發表于 12-30 16:27

?9次下載

FPGA布局及資源優化

DDR3。 2.FPGA架構設計問題 我們知道,FPGA片上分布著各種資源,如時鐘,serdes,RAM,LUT,IO等。在進行FPGA規劃時候,應當需要知道項目設計需求,以及需求各

URAM和BRAM有哪些區別

無論是7系列FPGA、UltraScale還是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就是我們所說的URAM。

URAM和BRAM有什么區別

無論是7系列FPGA、UltraScale還是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就是我們所說的URAM。

發表于 01-27 06:55

?12次下載

FPGA實現基于Vivado的BRAM IP核的使用

定制的RAM資源,有著較大的存儲空間,且在日常的工程中使用較為頻繁。BRAM以陣列的方式排布于FPGA的內部,是FPGA實現各種存儲功能的主要部分,是真正的雙讀/寫端口的同步的RAM。

基于FPGA設計的BRAM內部結構

再看末級觸發器對BRAM時序性能的影響,下圖依次展示了7系列FPGA、UltraScale+和Versal芯片在未使用和使用末級觸發器兩種情形下時鐘到輸出的延遲。

發表于 04-25 10:42

?1163次閱讀

HLS設計中的BRAM使用優勢

高層次綜合(HLS)是一種將高級編程語言(如C、C++或SystemC)轉換為硬件描述語言(HDL)的設計方法。在FPGA設計中,設計者可以靈活地利用FPGA內部的資源,如塊RAM(BRAM

FPGA的BRAM資源使用優化策略

FPGA的BRAM資源使用優化策略

評論