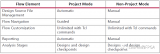

Vivado集成設計環境(IDE)交互式處理設計。工程模式下,既可以通過圖像界面下操作(GUI操作,鼠標操作),也可以通過運行Tcl腳本的方式在Vivado Tcl shell 中運行。 優勢: 工作模式

2020-11-09 17:15:47 5785

5785

文件來與所得結果進行對比驗證。 3.實驗步驟 3.1.在Vivado HLS GUI界面中創建項目 3.1.1.啟動Vivado HLS 2018.1 ? ? 3.1.2.創建一個新的

2020-12-21 16:27:21 4357

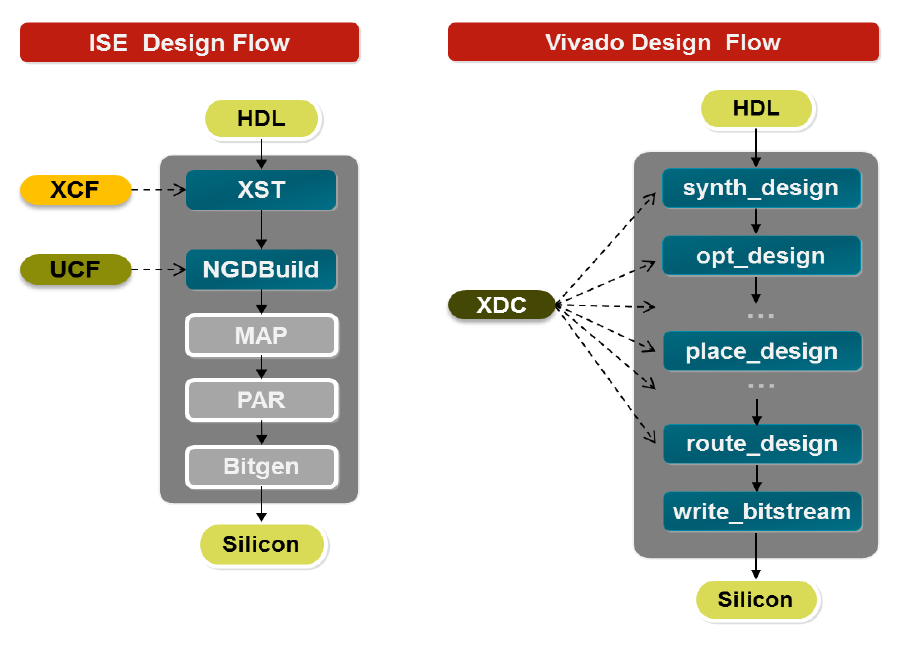

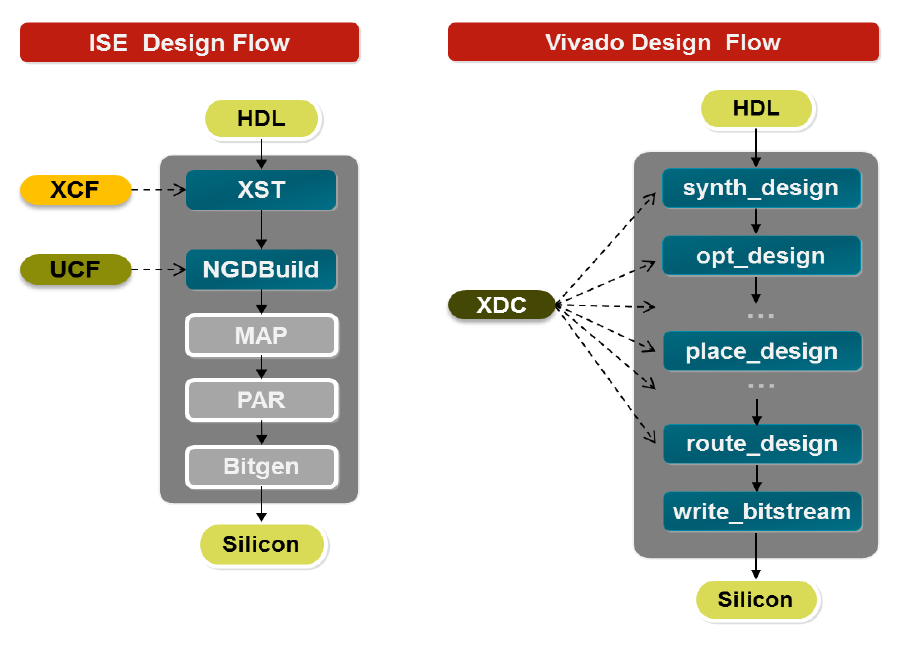

4357 Xilinx的新一代設計套件Vivado相比上一代產品ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。

2022-09-14 09:09:56 2515

2515 FPGA 的設計流程簡單來講,就是從源代碼到比特流文件的實現過程。大體上跟 IC 設計流程類似,可以分為前端設計和后端設計。

2023-04-23 09:08:49 3022

3022

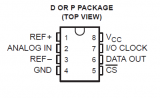

? 系統性的掌握技術開發以及相關要求,對個人就業以及職業發展都有著潛在的幫助,希望對大家有所幫助。本次帶來Vivado系列,TLC549驅動設計。話不多說,上貨。 TCL549驅動設計 在生活中

2023-07-27 09:25:05 2590

2590

許可證管理器以獲取有關確定系統許可的功能和設備的幫助。有關詳細信息,請參閱Tcl控制臺或消息。我嘗試了重新安裝和許可證,相同的結果....這是在webpack中禁用????約翰以上來自于谷歌翻譯以下

2018-12-12 10:55:17

/ 226第7章 Tcl在Vivado中的應用 / 2277.1 Vivado對Tcl的支持 / 2277.2 Vivado中Tcl命令的對象及屬性 / 2327.2.1 文件對象及屬性

2020-10-21 18:24:48

我在兩臺64位Windows機器上安裝了2013.1,并且兩者都崩潰了。 Vivado 2013.1窗口在崩潰之前會短暫出現。如果我從命令行運行,我會看到:****** Vivado v2013.1

2018-11-27 14:30:08

License(由VLM加載.xml文件),并在VLM中顯示。我在論壇中嘗試了很多解決方案: - 我重新安裝了Vivado三次, - 我用禁用防病毒軟件(Avast)運行模擬,我檢查了它的“病毒庫

2018-12-12 10:52:39

你好。當我試圖為我的ZYBO板合成zynq hw時,我得到了以下的licnese錯誤。我檢查了我的vivado許可證是否在許可證管理器中正確加載。請參閱隨附的文件了解詳細信息。我該怎么辦?警告

2018-12-25 11:03:50

在vivado的最后幾個反面,get_parameter general.maxThreads已在此機器上返回4 在2015.4,我現在得到2。我在GUI模式,沒有腳本,按下gui botttons

2018-12-13 10:32:20

你好,我們今天剛剛收到一個ZC706開發套件(帶有Zynq XC7Z045),我們非常驚訝,因為在歡迎信中寫道:“隨著Vivado 2015.4的發布,該產品已被凍結。它將不會在后來的Vivado軟件中運行”這應該是什么意思?我們正在使用最新的Vivado版本2016.1!謝謝,Cerilet

2019-10-10 08:24:14

Vivado Tcl零基礎入門與案例實戰-高亞軍編寫

2025-01-14 11:13:49

嗨,在我的Vivado實現tcl腳本中,以下行導致錯誤:設置SRC_PATH ./input.............#Input the netlistread_edif $ SRC_PATH

2018-10-18 14:26:39

1.實驗目的通過例程探索Vivado HLS設計流用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目用各種HLS指令綜合接口優化Vivado HLS設計來滿足各種約束用不用的指令來探索

2021-11-11 07:09:49

你好我使用免費的ISE Webpack許可證安裝了Vivado 2015.2。雖然我可以在許可證管理器中查看許可證,但Vivado軟件似乎在模擬時不會檢測到它。以下是顯示的兩個錯誤:1.錯誤

2020-04-07 13:29:03

set_param board.repoPaths行,或者在打開Vivado時從tcl控制臺添加)。 -board_files文件夾旁邊還有一個board_parts文件夾(在同一個board文件夾中

2018-12-28 10:52:41

;Run Behavioral Simulation之后,會出現如下圖界面,此時,在Tcl Console中并沒有出現仿真結果。

沒有出現仿真結果的原因是沒有給Vivado時間進行仿真,解決方法

2025-10-31 06:24:20

TakeVideos:快速使用的視頻連接口,關聯到DocNav,并篩選出Vivado使用的一些教學視頻;Release NotesGuide:在DocNav中打開Vivado release Notes

2019-07-18 15:40:33

TakeVideos:快速使用的視頻連接口,關聯到DocNav,并篩選出Vivado使用的一些教學視頻;Release NotesGuide:在DocNav中打開Vivado release Notes

2023-09-06 17:55:44

嗨,我需要為Vivado 2016.3運行tcl來運行多個測試平臺。如果我使用下一個:launch_simulationrun -allwait_on_run [current_run

2020-05-20 15:53:34

嗨,在網絡實施期間,當我將用戶ILA端口從3個端口擴展到11個端口時,會生成以下消息:[Vivado_Tcl 4-131] Power Optimization遇到異常:ERROR:[Common

2018-11-08 11:29:12

和源碼,減少硬盤空間占用。 1.打開Vivado工程,在Tcl Console中輸入reset_project命令(Type a Tcl command here處輸入reset_project后回車

2020-08-17 08:41:25

嗨,我正在使用Vivado和系統生成器2015.4,以及Matlab 2015b。我正在運行Windows 7.每當我嘗試使用.vhd文件或第三方文件在Sys Gen中進行模擬時,我會得到以下tcl

2020-04-13 09:28:58

文件,并點擊“確認”。4、點擊左側的View License Status按鈕,點擊Refresh按鈕進行更新。5、關機重啟電腦,重新運行vivado,然后仿真就可以啦。(新的license文件,在附件中)

2017-12-23 10:45:59

在Xilinx的Vivado開發流程中,出于設計源代碼保密的考慮,有時我們并不會交付源代碼,而是以網表的形式進行交付。初見面,一切如故先看一個簡單的example project,里面包含兩個

2022-07-18 16:01:04

。Xilinx公司從ISE工具的后期開始,在工具中引入了對tcl語言的支持。在目前廣泛使用的設計工具Vivado中,更是集成了tcl解釋器,實現了對tcl很好的支持,同時也大大提高了編譯及布局布線效率

2022-06-17 14:52:14

你好,我在Linux Mint 18.2 Sonya中安裝了沒有重大問題的SDSoC。我將一個在Windows中工作的C文件復制到Linux,創建了一個SDx項目,添加了文件,構建它沒有任何硬件功能

2018-12-26 11:26:29

先按照官方給的開源項目,e203_hbirdv2-masterfpgamcu200t目錄下的Makefile內容手動創建vivado工程。

在調用.tcl文件的過程中,每次進行到

2025-10-28 07:19:22

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

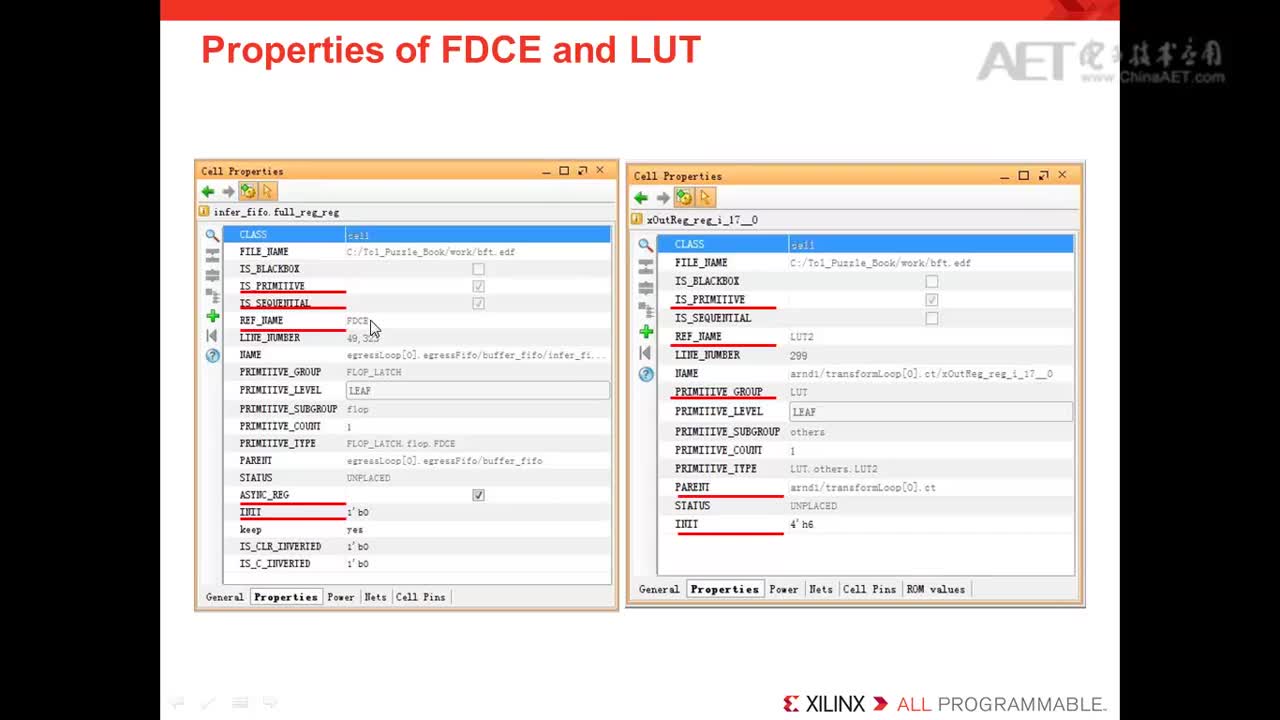

大家好,我是Vivado的新手。我想提取已實現設計的LUT名稱,但我沒有找到合適的tcl命令。以上來自于谷歌翻譯以下為原文Hi every body,I am new with Vivado. I

2018-11-02 11:09:53

我在Ubuntu 16.04上安裝了Vivado 2016.1,并在安裝時包含了SDK。當我執行文件 - >啟動SDK時,沒有任何反應。 Tcl控制臺顯示:信息:[Vivado 12-393

2018-12-20 11:11:23

在工程項目中常常使用xilinx的IP時常會遇到一些加密的verilog和vhdl,打開后是以Xlx開始的十六進制文件,某些IP中的tcl和ttcl也是用這種方式保存的十六進制文件。vivado中使用這些文件都沒有什么問題,就想知道這些文件是如何產生出來的?

2021-06-20 17:50:58

文檔中明確描述vivado2021.2版本對應VCS的版本是2020.12,由于license問題所以選擇vcs2018的版本;雖然目前與官方的版本不匹配,但是不影響正常使用;

使用tcl界面

2025-10-24 07:28:03

文件。首先打開之前復制的cfgmem.tcl文件,將第一行加'#'號注釋掉或直接刪掉,之后在開頭添加如下圖的三行代碼,將第一個紅框中的內容設為將要生成

2025-10-27 08:25:28

嗨,我想找到我可以在Vivado2014.4中制作我的mcs文件的地方!..我在菜單或其他地方找不到任何項目。但是,我在論壇中搜索并發現我可以通過tcl命令 - write_cfgmem來做到這一點

2020-06-04 14:19:26

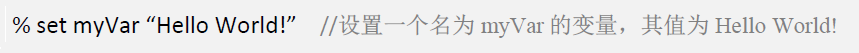

Command Language”的簡稱,是一種簡單高效可移植性好的腳本語言,目前已經廣泛應用在幾乎所有的EDA工具中。而在Xilinx最新的FPGA設計工具Vivado中,Tcl成為唯一支持的腳本

2020-06-07 13:59:52

你好:我沒有通過ZC702評估套件和Vivado 2013.2中的PMOD1上的SPI外設通過EMIO獲得預期的行為。我已閱讀AR#47511我必須在MHS文件中更改或添加一些代碼行,但我在項目目錄中找不到MHS文件。 Vivado不使用MHS文件嗎?我怎么解決這個問題?

2019-11-08 12:12:06

在我們的設計中,Vivado實現結果因運行而異。我們想要從“最佳”實現中鎖定兩個模塊的放置信息。然后將其保存以備將來運行。我們知道這可能與pblock和分層設計有關。但是,分層設計文檔并不十分

2018-10-18 14:36:14

/vivado_lib”在vivado的“Tcl Console”框里面輸入TCL庫編譯命令,只需靜靜等待編譯完成;c、將“D:/modeltech64_10.4/vivado_lib”里面

2018-10-16 19:43:20

vivado中synthesis通過,implement通過,但是在編譯simulation的時候報錯:[USF-XSim-62] 'compile' step failed with error

2017-07-05 10:46:33

:Vivado使用‘/’);

3) 在Tcl命令框中,輸入命令:source ./ Oscilloscope.tcl。輸入完畢按回車,運行Tcl;

4) 等待Tcl綜合、實現、生成比特流文件;

5) 在

2023-08-17 19:31:54

你好,我編寫了一個Tcl腳本來合成Vivado Design Suite 2014.4中的設計(適用于Zynq ZC 706)。設計中的庫未編譯。彈出錯誤,表示找不到特定的.vhd文件。我檢查了

2020-04-16 10:15:31

大家好,有誰知道如何更改Vivado TCL控制臺窗口中的字體/字體大小?我有一個2016.1的安裝,我將字體從Courier更改為Consolas并稍微縮小尺寸以增加線路上的信息密度,但我最近安裝

2019-04-22 15:11:29

Vivado HLS中創建一個新項目(針對Virtex 6)并嘗試在“C Synthesis”之后執行“Export RTL”時,“格式選擇”下拉菜單中沒有“Pcore for EDK”選項。此外

2018-12-28 10:33:38

嗨,大家好,我是vivado工具的新手,我需要為MIG或QSFP導出.xlsx報告文件我可以使用Tcl命令自動保存報告文件嗎?

2020-05-12 08:31:50

你好,有沒有辦法在Vivado 2016.1中關閉特定的DRC違規或警告?其次是AR#63997的方向,我試過:set_property嚴重性警告[get_drc_checks RTSTAT-2

2018-10-26 15:03:13

你好我正在嘗試在vivado HLS中創建一個IP,然后在vivado中使用它每次我運行Export RTL我收到了這個警告警告:[Common 17-204]您的XILINX環境變量未定義。您將

2020-04-03 08:48:23

所有: 我正在嘗試編寫一個TCL腳本來重命名帶有修訂號的.bit文件。我需要一種方法讓Vivado告訴我活動實現的名稱。例如,如果我的活動實現是impl_5,我需要知道這一點,以便找到正確的.bit

2018-11-12 14:23:34

今天推出Xilinx已發布的《Vivado使用誤區與進階》系列:用TCL定制Vivado設計實現流程。

上一篇《Tcl 在 Vivado 中的應用》介紹了 Tcl 的基本語法以及如何利 用 Tcl

2023-06-28 19:34:58

你好,嘗試使用kcu105 TRD設計中的.tcl在2018.2中進行ti構建設計,我遇到了這個錯誤。錯誤:[BD_TCL-109]此腳本是使用Vivado生成的,正在Vivado中運行。請在

2019-10-18 09:36:13

有沒有辦法改變比特流文件位于Vivado(2016.1)內的位置?我知道我可以在Tcl控制臺上輸入tcl命令“write_bitstream”(https://forums.xilinx.com

2020-05-12 09:23:20

rapidio參考設計中摘出的一段代碼,示例了這種用法: 那么在Vivado GUI中,該如何設置,可以使得代碼可以準確找到這個include的文件呢? 1. 在Non-Project Mode下

2017-11-10 14:49:02 10763

10763 。總體而言,Vivado 2017.1比Vivado2016.4給出了更好的效果。雖然在測試1中的結果有些相似,但是Vivado2017.1從測試2和3中獲得的最佳TNS總負余量和WS最差余量卻比Vivado2016.4要好得多。

2018-07-04 11:23:00 10852

10852

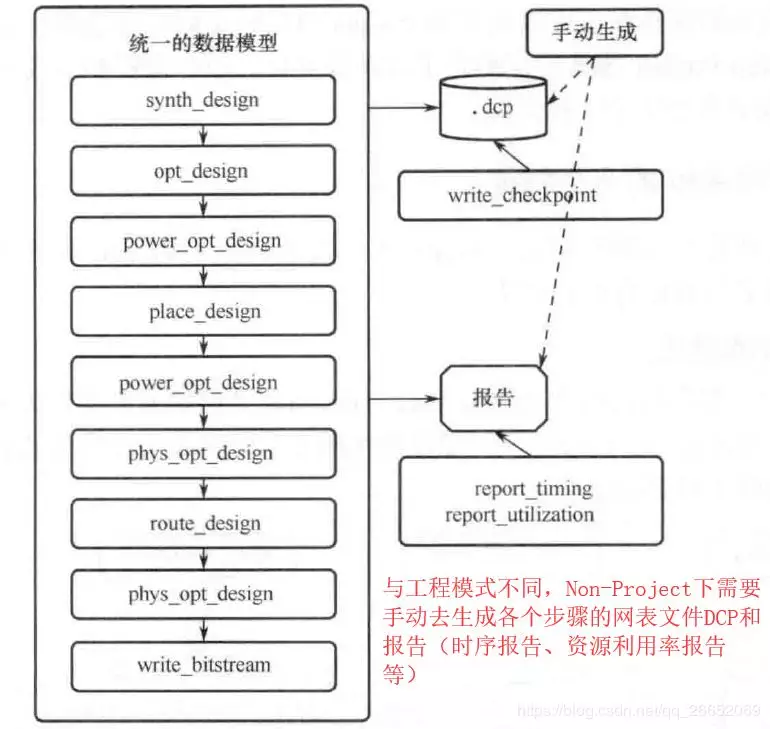

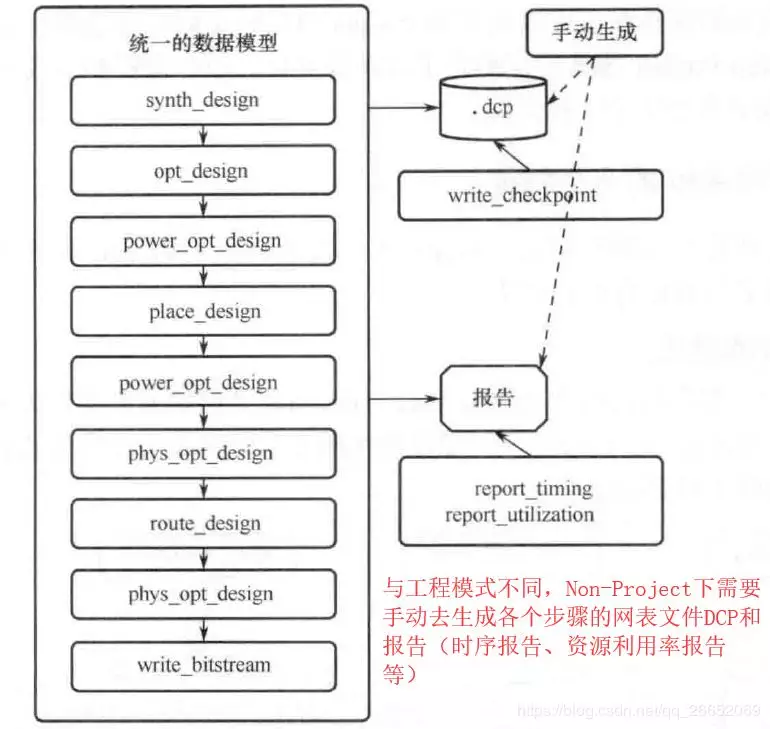

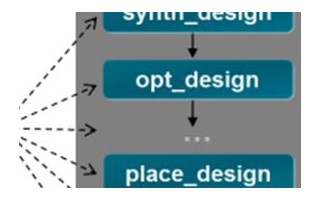

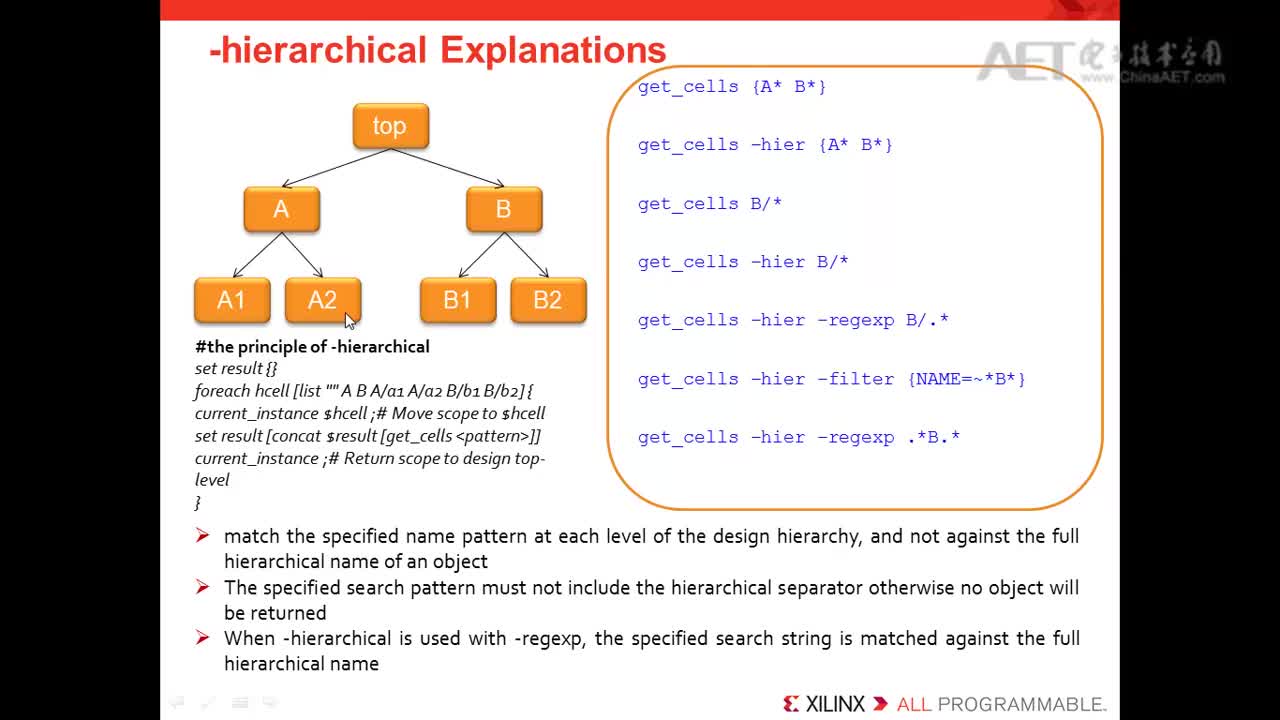

其實Tcl在Vivado中還有很多延展應用,接下來我們就來討論如何利用Tcl語言的靈活性和可擴展性,在Vivado中實現定制化的FPGA設計流程。 基本的FPGA設計實現流程 FPGA的設計流程簡單來講,就是從源代碼到比特流文件的實現過程。大體上跟IC設計流程類似,可以分為前端設計和后端設計。

2017-11-18 01:48:01 4100

4100

在ISE下,對綜合后的網表進行編輯幾乎是不可能的事情,但在Vivado下成為可能。Vivado對Tcl的支持,使得Tcl腳本在FPGA設計中有了用武之地。本文通過一個實例演示如何在Vivado下利用Tcl腳本對綜合后的網表進行編輯。

2017-11-18 03:16:01 8351

8351

在Vivado下,有兩種方式管理IP。一種是創建FPGA工程之后,在當前工程中選中IP Catalog,生成所需IP,這時相應的IP會被自動添加到當前工程中;另一種是利用Manage IP,創建獨立

2017-11-18 04:22:58 6145

6145 關于Tcl在Vivado中的應用文章從Tcl的基本語法和在Vivado中的應用展開,介紹了如何擴展甚至是定制FPGA設計實現流程后,引出了一個更細節的應用場景:如何利用Tcl在已完成布局布線的設計上

2017-11-18 18:26:46 5856

5856

TCL腳本語言 Tcl(Tool Command Language)是一種很通用的腳本語言,它幾乎在所有的平臺上都可以解釋運行,而且VIVADO也提供了TCL命令行。最近發現TCL腳本貌似比GUI下操作VIVADO效率高一些,方便一些。

2018-04-11 12:09:00 10954

10954 Vivado HLS 是 Xilinx 提供的一個工具,是 Vivado Design Suite 的一部分,能把基于 C 的設計 (C、C++ 或 SystemC)轉換成在 Xilinx 全可編程芯片上實現用的 RTL 設計文件 (VHDL/Verilog 或 SystemC)。

2018-06-05 10:31:00 7420

7420

工具命令語言(TCL)是集成在VIVADO環境中的腳本語言。TCL是半導體工業中用于應用程序編程接口的標準語言,并由SyoSype?設計約束(SDC)使用。

2018-08-09 08:00:00 38

38 本視頻將指您介紹如何使用Vivado設計套件中的交互式“IO Pin Planning”和“Device Exploration”功能。具體來說,IO規劃包括:在設計中創建,配置,分配和管理IO端口以及時鐘邏輯

對象。該視頻教程描述了在設計流程的不同階段如何執行IO規劃的步驟。

2018-11-20 06:36:00 5829

5829 該視頻快速概述了ISE和Vivado中可用的XADC向導中的界面,功能和功能。

對于希望實例化基本設計的數字設計人員來說,這是一個很好的工具。

2018-11-20 06:19:00 5308

5308 了解如何使用Tcl命令語言以批處理模式運行Vivado HLS并提高工作效率。

該視頻演示了如何從現有的Vivado HLS設計輕松創建新的Tcl批處理腳本。

2018-11-20 06:06:00 3634

3634 了解如何使用2014.1中引入的新激活許可為Vivado工具生成許可證。

另外,了解Vivado 2014.1中的許可更改如何影響您,以及如何在激活客戶端中使用新的Vivado License Manager

2018-11-22 07:10:00 3623

3623 了解如何使用Vivado在設備啟動時及其周??圍進行調試。

你也會學習

使用Vivado 2014.1中引入的Trigger at Startup功能來配置和預先安裝a

調試核心并觸發設備啟動時或周圍的事件......

2018-11-22 07:05:00 5047

5047 Constraint Set里(Vivado支持.tcl文件作為約束文件,添加時將文件類型切換為.tcl即可,如圖6所示)。

2019-01-15 16:48:47 6312

6312

工程模式的關鍵優勢在于可以通過在Vivado 中創建工程的方式管理整個設計流程,包括工程文件的位置、階段性關鍵報告的生成、重要數據的輸出和存儲等。

2019-07-24 17:30:38 5388

5388

實際上Tcl的功能可以很強大,用其編寫的程序也可以很復雜,但要在Vivado或大部分其它EDA工具中使用,則只需掌握其中最基本的幾個部分

2019-07-24 16:52:00 4121

4121

Vivado IDE約束管理器將任何已編輯的約束保存回XDC文件中的原始位置,但不會保存在Tcl腳本中。 任何新約束都保存在標記為目標的XDC文件的末尾。

2020-11-13 10:53:38 5530

5530

,還是從對使用者思路的要求,都是全新的;在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。 本文介紹了Tcl在V

2020-11-17 17:32:26 3306

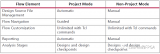

3306 Vivado有兩種工作模式:project模式和non-project模式。這兩種模式都可以借助VivadoIDE或Tcl命令來運行。相比之下,VivadoIDE給project模式提供了更多的好處,而Tcl命令使得non-project模式運行起來更簡單。

2020-10-21 10:58:07 4270

4270

這里帶大家一起體驗一下Vivado 的ECO流程,以vivado自帶的Example Design為例, 直接用TCL命令修改網表,在正常的寄存器路徑之間加一級LUT。

2020-11-29 11:04:53 5256

5256

使用Vivado Runs基礎結構時(例如,launch_runs Tcl命令),請將此命令添加到.tcl文件,并將該文件作為執行運行的write_bitstream步驟的預鉤添加

2021-02-20 06:02:57 9

9 本篇文章來自賽靈思高級工具產品應用工程師 Hong Han. 本篇博文將繼續介紹在Vitis中把Settings信息傳遞到底層的Vivado. 對于Vivado實現階段策略的指定

2021-08-13 14:35:56 4953

4953 符。 Vivado Synthesis Hangs/StopsVivado在綜合時,如果顯示一直在運轉,但不再輸出任何log信息時,檢查一下工程路徑是否包含了特殊字符“”。因為“”字符在Tcl腳本里是變量置換

2021-09-12 15:15:19 7447

7447 XDC約束可以用一個或多個XDC文件,也可以用Tcl腳本實現;XDC文件或Tcl腳本都要加入到工程的某個約束集(set)中;雖然一個約束集可以同時添加兩種類型約束,但是Tcl腳本不受Vivado工具管理,因此無法修改其中的約束;

2022-06-30 11:27:23 5420

5420 一個完整的vivado工程往往需要占用較多的磁盤資源,少說幾百M,多的甚至可能達到上G,為節省硬盤資源,可以使用Tcl命令對vivado工程進行備份,然后刪除不必要的工程文件,需要時再恢復即可。

2022-08-02 15:01:06 6814

6814 Xilinx的新一代設計套件Vivado相比上一代產品ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。

2022-09-19 16:20:51 2298

2298 vivado有project模式和non-project模式,project模式就是我們常用的方式,在vivado里面新建工程,通過GUI界面去操作;non-project模式就是純粹通過tcl來指定vivado的流程、參數。

2022-10-17 10:09:29 4603

4603 電子發燒友網站提供《在Vivado 2020.2中開始使用Arty Z7.zip》資料免費下載

2022-12-06 15:16:19 2

2 Vivado是Xilinx推出的可編程邏輯設備(FPGA)軟件開發工具套件,提供了許多TCL命令來簡化流程和自動化開發。本文將介紹在Vivado中常用的TCL命令,并對其進行詳細說明,并提供相應的操作示例。

2023-04-13 10:20:23 5476

5476 Xilinx的新一代設計套件Vivado相比上一代產品 ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言 XDC 以及腳本語言 Tcl 的引入則成為

2023-04-15 09:43:09 2185

2185 今天推出Xilinx已發布的《Vivado使用誤區與進階》系列:用TCL定制Vivado設計實現流程。

2023-05-05 09:44:46 2068

2068

關于 Tcl 在 Vivado中的應用文章從 Tcl 的基本語法和在 Vivado 中的 應用展開,繼上篇《用 Tcl 定制 Vivado 設計實現流程》介紹了如何擴展甚 至是定制 FPGA

2023-05-05 15:34:52 4104

4104

電子發燒友網站提供《Vivado設計套件Tcl命令參考指南.pdf》資料免費下載

2023-09-14 10:23:05 1

1 電子發燒友網站提供《Vivado設計套件用戶指南:使用Tcl腳本.pdf》資料免費下載

2023-09-14 14:59:39 1

1 電子發燒友網站提供《Vivado Design Suite用戶指南:使用Tcl腳本.pdf》資料免費下載

2023-09-13 15:26:43 2

2 后的約束在之前版本中已存在,那么Vivado會給出警告信息,顯示這些約束會覆蓋之前已有的約束;如果是新增約束,那么就會直接生效。

2024-10-24 15:08:40 1602

1602

電子發燒友App

電子發燒友App

評論