一、創建帶有MicroBlaze處理器的IP設計

使用Vivado進行MicroBlaze設計和使用ISE有很大的不同。(譯者加:所以你要仔細看下面的說明)

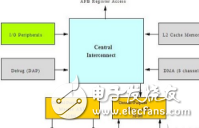

Vivado IDE使用IP綜合設計工具進行嵌入式開發。IP綜合工具是一個基于圖像界面的工具,能夠幫助你構建復雜的IP子系統。

Vivado IDE的IP目錄中提供了很多現成的IP核,提供使用。你也可以向這個目錄添加自定義的IP核。

開始IP綜合設計(步驟)

1、在工作流導向面板中的IP Integrator中,點擊Create Block Design。(表示你要開始構建帶有IP核的框圖了)

2、Add IP,找到MicroBlaze,添加到Block中。

(當然,也可以用tcl命令添加IP核:create_bd_cell -type ip -vlnv xilinx.com:ip:microblaze:9.3 microblaze_0)

3、雙擊MicroBlaze的Block,開始配置軟核。

三、MicroBlaze配置窗口(配置窗口說明)

MicroBlaze的配置向導提供如下功能:

---可一鍵配置的基于模板的配置對話框

---MicroBlaze主要參數的評估:相對面積,頻率,性能表現,評估是基于對話框中給定的參數。

---配置流程的向導

---所有配置選項的提示,用來理解各個選項的作用

---使用Adaanced按鈕,可以直接訪問tabbed接口的所有選項。

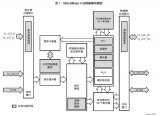

MicroBlaze配置向導提供如下向導頁:

---配置向導(Configuration Wizard):第一頁,提供模板選擇和一般設置。

---一般設置(General):執行單元的選擇,優化。

---異常(Exceptions):異常功能的使能。(如果在第一頁選中了該功能)

---調試(Debug):斷點和查看點的數量。(如果在第一頁選中了該功能)

---緩存(Cache):緩存設置。(如果在第一頁選中了該功能)

---內存管理單元(MMU):MMU設置。(如果在第一頁選中了該功能)

---總線(Buses):總線設置。最后一頁,總是顯示。

在配置向導的歡迎頁中,左邊顯示的是當前設置的頻率、面積和性能的相對評估值。

頻率:這個值是用當前架構的最大值進行歸一化取得相對值。表示當前設置能夠達到的頻率。(這個值可能會比實際的值超過30%,不要把這個估計值當做系統一定能達到的頻率的保證。)

面積:這個值表示LUT數量,用當前架構的最大值進行歸一化取得相對值。...(...5%...)

性能:當前設置下的相對性能估計。

BRAMs:(Vivado 2015.1中沒找見)

DSP48或者MULT18:(Vivado 2015.1中沒找見)

第一頁(Welcome Page)

使用配置向導最簡單的辦法便是,使用六個配置模板中的一個,每一個配置模板都是一個完整的配置方案。你可以使用模板作為自己配置的起點,再修改模板給定的設置。

每當你修改一個選項,左邊的評價參數便會實時更新。下面介紹這六個配置模板。

---最小面積(Minimum Area):軟核提供的最小架構。沒有緩存和調試。

---最強性能(Maximum Performance):可能的最大性能。擁有很大的緩存和調試,擁有所有的執行單元。

---最高頻率(Maximum Frequency):可能的最高頻率。小緩存,沒有調試,一部分執行單元。

---帶有MMU的Linux(Llinx with MMU):當運行帶有MMU的linux時,能夠獲得高性能的設置。內存管理使能,大的緩存和調試,所有的執行單元。

---低端的帶有MMU的Linux:...內存管理使能,小的緩存和調試。

---典型:在性能、面積、頻率中取了折中。適合脫機程序,低開銷內核。有緩存和調試功能。

一般設置

如果模板沒有選擇,也可以在頁面中,根據項目需求,進行選項配置。當你把鼠標放在選項上時,會出現一個提示,告訴你它有什么用。下面詳細介紹這些選項。

---Select implemention to optimize area(with lower instruction throughput):使能面積優化功能。如果選了這個,implementation就會優化面積,尤其是減少流水線數量,從5條減少到3條。(推薦:建議在資源比較緊張的架構,如Artix-7,使能這個選項。然而,如果對性能有敏感的要求,就不要選這個選項,因為一些指令需要額外的時鐘周期去執行。另外,對于MMU, Branch Target Cache, Instruction Cache Streams, Instruction Cache Victims, Data Cache Victims, ACE是不能進行面積優化的。)

---Enable MicroBlaze Debug Module Interface:使能調試功能。用Xilinx Microprocessor Debugger來下載、調試程序。(推薦:除非面積資源奇缺,否則不要禁止這個功能。)

---Use Instruction and Data Caches:當執行放在LMB之外的程序的時候,可以使用指令緩存來改善性能。指令緩存有如下特點:....當使用外部存儲時,激活這個選項可以明顯地改善性能,即使這個緩存很小。

---Enable Exceptions:當使用一個支持異常的操作系統時,需要激活這個選項。或者在一個單獨的程序中添加異常回調函數。

---Use Memory Management:當使用一個支持虛擬內存保護的操作系統時(如Linux),需要激活。(當你使能面積優化或者堆棧保護功能時,內存管理單元是不可見的,自動禁止)

---Enable Discrete Ports:使能軟核上的獨立端口。

第二頁(General)

1、指令(Instructions)

---使能桶型移位器(Enable Barrel Shifter):使能軟核中的筒形移位器硬件。激活這個參數,就可以使用如下指令(bsrl,bsra,...)使能這個可以提高應用的性能,但是會增大軟核的尺寸。如果激活,編譯器會自動使用筒形移位器指令。

---使能浮點單元(Enable Floating Point Unit):使能一個單精度浮點單元(FPU)。使用FPU可以明顯地提高應用的單精度浮點性能,同時也會增大軟核的尺寸。

---使能整形乘法器(Enable Integer Multiplier):使能一個整形乘法器硬件。若激活,則可以在給MUL32賦值時,使用mul和muli指令。當給MUL64賦值時,使用mulh,mulhu,mulhsu指令。這個參數可以設置為NONE,可以把MUL或者DSP48釋放,用作其他用途。這樣做對軟核的面積影響很小。當使用這個選項,編譯器自動使用mul指令。

---使能整形觸發器(Enable Integer Divider):使能一個整形除法器硬件。若激活,可以使用idiv,iduvu指令。使能這個選項可以提高應用中的除法性能,但是增大了軟核的尺寸。當使用這個選項,編譯器自動使用idiv指令。

---使能額外機器狀態寄存器指令(Enable Additional Machine Status Register Instructions):若激活,則可以讀寫MSR,使用msrset和msrclr命令。可以提高訪問MSR的性能。

---使能模式比較器(Enable Pattern Comparator):如激活,則可以使用模式匹配指令pcmpbf,pcmpeq,pcmpne。模式匹配字節查找指令(pattern comparator byte find, pcmpbf)返回找到的第一個字節的位置,提高字符串和模式匹配操作的效率。若使能,SDK庫會自動使用這個指令。pcmfeq和pcmpne指令根據兩個字是否相同,返回1或者0。這些指令會提高setting flags的效率,編譯器會自動使用它們。激活這個選項還可以count leading zeros指令,clz。clz指令能提高優先級編碼的效率。

---使能保留的加載/保存和交換指令(Enable Reserved Load/Store and Swap Instructions):lbur,lhur,lwr,sbr,shr,swr,swapb,和swaph。這些指令能夠以相對的字節序來讀寫數據,交換指令能交換字節或者半個字長。當用little-endian的MicroBlaze訪問big-endian的網絡時,可以提高效率。

---使能額外的流命令(Enable Additional Stream Instructions):當使用AXI4-Stream鏈接時,提供額外的功能。這包括動態訪問指令GETD和PUTD,這兩個指令用寄存器來選擇接口。(重要:一定要激活流異常功能,才能使用這些指令,而且知道選擇一個流鏈接)

2、優化

選擇Implementation來優化面積(當指令吞吐量很低時):這個選項和歡迎頁的選項功能相同。...

3、容錯

---使能容錯功能(Enable Fault Tolerance Support)

第三頁(異常)

1、數學異常(Math Exceptions)

---使能浮點單元異常

---使能整形除法異常

2、總線異常(Bus Exceptions)

---使能指令端AXI異常

---使能數據段AXI異常

3、其他異常(Other Exceptions)

---使能非法指令異常

---使能Unaligned數據異常

---產生非法指令異常,除了NULL指令

---使能流異常

---使能堆棧保護

第四頁(緩存)

第五頁(MMU)

第六頁(調試)

第七頁(總線)

1、本地內存總線接口(LMB)

2、AXI和ACE接口

3、流接口

4、其他接口

四、MicroBlaze處理器的交叉觸發特性

當使能basic debugging,交叉觸發功能有兩個信號提供:DBG_STOP和MB_Halted。

---當DBG_STOP輸入為1,MicroBlaze會在幾條指令后暫停。XMD檢測到MicroBlaze暫停了,并記錄暫停的位置。這個信號可以被任何外部的事件用來暫停軟核,例如當一個集成邏輯分析器(ILA)被觸發。

---MB_Halted輸出信號為1,當MicroBlaze暫停的時候,例如碰到一個斷點或者觀察點,執行了一條XMD停止指令之后,或者當DBG_STOP被置1。當通過XMD命令重新啟動軟核時,輸出清0。

這兩個引腳是隱藏的,除非在歡迎頁中使能顯示獨立端口(Show Discrete Ports)。

你也可以使用MB_Halted信號來觸發一個集成邏輯分析器,或者在多核系統中,暫停其他MicroBlaze軟核(連接到它們的DBG_STOP端)。

當啟動擴展調試功能時,交叉觸發功能可以和MDM一起使用。MDM在所有連接的處理器中,提供可編程的交叉觸發功能,包括外部觸發的輸入端和輸出端。可以查閱MicroBlaze Debug Module Product Guide手冊查看細節。

MicroBlaze最多支持8個交叉觸發動作。交叉觸發動作由相對應的MDM交叉觸發輸出產生,兩者通過調試總線連接。

可以有兩個地方設置擴展調試功能:一個是前面提到的調試配置頁,另一個是在運行MicroBlaze的Block Antomation時,選擇該功能。

另外,還要在MDM模塊的配置頁中,使能交叉觸發功能(Enable Cross Trigger)。MDM模塊可以最多配置4組外部觸發的輸入和輸出。

最后,運行Connection Automation,連接交叉觸發信號到ILA(ILA教程)。

...

五、自定義邏輯

Vivado的IP管理器允許用戶和第三方IP核開發者將自定義的IP核添加到Vivado的IP核目錄中。這樣用戶就能在Vivado中實例化第三方IP核了。

當IP開發者使用Vivado的IP管理器打包IP核時,IP的使用者對xilinx提供的IP核,還是第三方IP,亦或用戶定義的IP,都有一樣的使用體驗。

IP開發者可以使用IP管理器打包IP文件,并把數據放入ZIP文件。IP使用者接收這個ZIP文件,安裝到Vivado的IP目錄中,然后用戶就可以使用這個IP核了。

推薦:為了保證IP核的質量,建議IP開發者在用用戶的使用工作流中運行每一個IP核,確保每個IP核都是可用的。

六、完成連接(Completing Connections)

當你配置完了MicroBlaze處理器,就可以開始實例化其他IP核,繼續你的設計。

在Canvas(放置Block的面板)上,右擊,選擇Add IP。

你可以使用兩個內置的特性來完成子系統剩余部分的IP核設計:Block Automation和Conncetions Automation,幫助你放置一個基本的微處理器系統,并且/或者連接端口到外部I/O口。

Block Automation

當block design中實例化了一個ZYNQ7處理系統或者MicroBlaze處理器時,Block Automation功能就可以使用。

1、點擊Run Block Automation,幫助你完成一個簡單的MicroBlaze系統。

Run Block Automation對話框提供了一個微處理器系統必需的基本特性。

2、單擊OK。

Using Connection Automation

當IP集成工具發現canvas上的IP實例化之間,存在可能的連接時,它會打開Connection Automation功能。

例如,我另外添加了兩個IP核,GPIO和Uartlite。IP集成工具會決定一下連接:

---處理器的ext_reset_in引腳必須連接到一個復位源,復位源可以是內部的復位源,或者是外部輸入引腳。

---時鐘模塊的CLK_IN_1_D引腳必須連接到一個內部時鐘源,或者外部輸入引腳。

---AXI GPIO的s_axi必須接到一個主機的AXI接口上。

---AXI GPIO的核心gpio必須接到外部的IO引腳。

---Uartlite的s_axi必須接到一個主機的AXI接口上。

---Uartlite的uart必須接到外部引腳上。

Using Board Automation

當使用像KC705這種刁刁的板子的時候,Vivado提供了Board Automation(像我這種撐死只有Nexys4的屌絲,只能......怒略一記)

Manual Connections in an IP Integrator Design

(譯者注:一般連線方式,可以手動連接,類似于AD畫板子軟件里的那種)

Manual Creating and Connecting to I/O Ports

你可以在IP工具中創建外部IO端口。你可以選擇信號或者接口到外部的IO端口,通過選擇一個引腳,總線或者接口連接。

具體辦法是,在模塊的引腳接口處,右擊。在彈出的菜單中,選擇:

---Make External.可以用多選操作(Ctrl+Click)選擇多個端口。這個命令的作用是連接模塊上的引腳到外部引腳。

startgroup

create_bd_intf_port -mode Master -vlnv xilinx.com:interface:gpio_rtl:1.0 GPIO

connect_bd_intf_net [get_bd_intf_pins axi_gpio_0/GPIO] [get_bd_intf_ports GPIO]

endgroup

(這是該操作的tcl命令,第一句話是創建端口,第二句話是連接)

---Create Port.對非信號接口使用該命令,如clock,reset,或者uart_txd.創建的時候,可以設定很多參數,比如輸出/輸出,位寬,類型等等。如果是時鐘,需要指定它的頻率。

startgroup

create_bd_port -dir I -type clk aa

set_property CONFIG.FREQ_HZ 100000000 [get_bd_ports aa]

endgroup

(這是該操作的tcl命令,第一句話是創建端口,第二句話是設置參數)

---Create Interface Port。對同一個功能的一組信號接口創建此類端口。例如,S_AXI是一些Xilinx IP的接口端口。這個接口還可以指定接口的類型和模式(主機還是從機)。

Memory Mapping in Address Editor

產生地址映射的方法如下:

1、單擊Address Editor。

2、單擊左邊的Auto Assign Address按鈕。(按鈕在左側)

如果你從IP框圖產生RTL代碼時沒有第一次生成地址,會彈出一個提示框,提供一個自動分配地址的工具。

你也可以在Offset Address和Range兩類輸入值,來設置地址。只有當IP框圖中包含一個總線主機的IP核(例如ZYNQ7)時,Address Editor才會打開。

Running Design Rule Checks

Vivado實時進行設計規則檢查。然而,錯誤總是會發生。例如,時鐘引腳上的頻率也許沒有設置正確。

如果要運行一個全面的檢查,可以單擊Validate Design。

Integrating a Block Design in the Top-Level Design

完成了上面的步驟后,還有兩個步驟需要做:

---產生輸出文件

---創建HDL封裝

在項目的源文件窗口創建文件。文件類型取決于項目新建時是verilog還是vhdl。具體方法如下:

1、在Block Design面板下,展開Design Source,選擇Generate Output Products。

2、在左側的工作流面板中的IP工具下,單擊Generate Block Design.

你可以在一個高層次設計中集成一個IP block。這樣做的方法是,在高層次的HDL文件中,實例化這個Block設計。

為了實例化一個更高的層次,在Block Design面板中的Design Sources中,右鍵design,選擇創建HDL封裝。

Vivado提供了兩種創建HDL封裝的方法:

---Vivado新建并自動更新封裝,這是默認選項。

---創建一個用戶可修改的腳本,這個腳本可以修改和保存。如果你選擇了這個,那你每次如果修改了block design中的端口,都需要修改手動更新封裝。

到這里,你已經為你的IP設計做好了HDL封裝,可以進行后面的步驟了。

MicroBlaze處理器約束

IP工具已經在產生輸出文件時,為IP核創建了約束文件;然而,你必須為自定義的IP或者更高層次的代碼設置約束。

一組約束,是XDC文件中的包含了設計約束的集合。有兩種約束:

---物理約束。定義了引腳放置,以及元胞(BRAM, LUT, Flip Flop)的絕對或者相對位置,還有器件的配置。

---時序約束。遵循SDC業界標準,定義了設計的頻率要求。如果沒有時序約束,Vivado僅僅會優化線寬和布線擁堵。(如果沒有時序約束,Vivado的implementation就無法提高設計的性能。Vivado不支持UCF格式的約束)

關于時序約束,下面多說兩句:

你有幾種使用約束集合的方法:

---一個約束集合中有多個約束文件

---多個約束集合,然而在分開的文件夾中。

---一個主約束文件,設計中的改變存于一個新的約束文件夾中。

---...

按功能,分開約束文件,有利于你從宏觀更清楚地把握約束策略,有利于應對時序和實現過程中的變化。

約束水太深,又太重要,詳情查看官方文檔。Vivado Design Suite User Guide: Using Constraints

當你完成了設計,也約束完了,現在可以進行合成、實現、生成bit流了。

然后,就可以導入硬件到SDK了。具體方法是:

File->Export->Export Hardware for SDK,彈出對話框,提供一些選擇選項。你可以導出硬件定義和比特流,并打開SDK。然后,就可以開始編寫軟件了。或者,你也可以從SDK把elf文件導入到Vivado。

電子發燒友App

電子發燒友App

評論