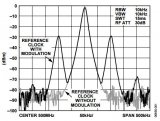

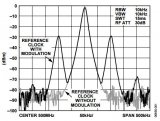

鎖相環 (PLL) 和壓控振蕩器 (VCO) 輸出特定頻率的RF信號,理想情況下此信號應當是輸出中的唯一信號。但事實上,輸出中存在干擾雜散信號和相位噪聲。本文討論最麻煩的雜散信號之一——整數邊界雜散,它如何仿真與消除,你真的搞清楚了?

2023-05-22 11:10:35 10626

10626

直接數據頻率合成器(DDS)因能產生頻率捷變且殘留相位噪聲性能卓越而著稱。另外,多數用戶都很清楚DDS輸出頻譜中存在的雜散噪聲,比如相位截斷雜散以及與相位-幅度轉換過程相關的雜散等。此類雜散是實際

2023-09-04 16:29:09 1183

1183

在整個PCBA生產制造過程中, PCB 設計是至關重要的一部分,今天主要是關于 PCB 雜散電容、影響PCB 雜散電容的因素,PCB 雜散電容計算,PCB雜散電容怎么消除。

2023-09-11 09:41:20 2916

2916

與EVAL-AD7960FMCZ評估板及其控制器板SDP-H1上的任何信號頻率都不相關。找出雜散源的另一種方法是清理測試臺,也許是測試臺上的某些物體產生了外部干擾。當關掉臺架上的日光燈后,雜散消失。此外還發

2019-02-14 14:18:45

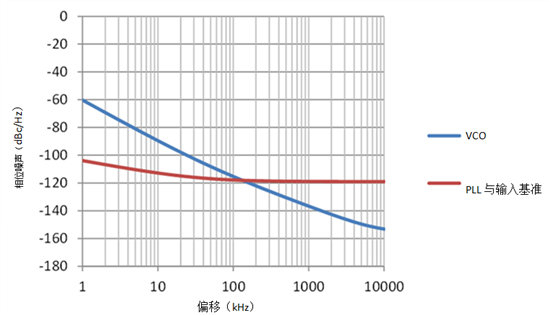

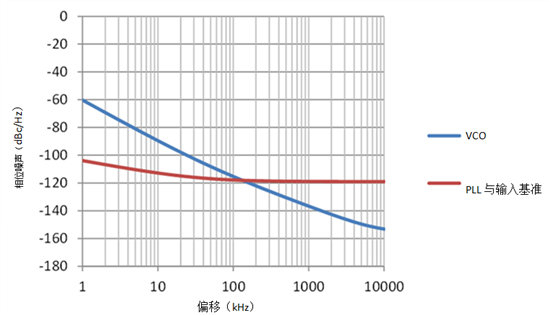

達到高鑒相頻率,低相噪的目的,甚至會超過小數分頻的鎖相環。另外也需要考慮由于采用了雜散補償電路,所以該電路會增加環內的相位噪聲。 從雜散性能上看,在較小的信道間隔(1MHz)上,小數分頻的鎖相環的雜散

2019-01-16 12:27:07

考慮由于采用了雜散補償電路,所以該電路會增加環內的相位噪聲。從雜散性能上看,在較小的信道間隔(1MHz)上,小數分頻的鎖相環的雜散性能也會比整數分頻的鎖相環好。在中等的信道間隔(10kHz,1MHz)上

2017-04-27 15:58:16

出現一個與基帶信號相關的雜散點幅度-50dBm左右,影響了射頻輸出的Sfdr。具體現象:

輸出2.2ghz點頻時,雜散點在2.6GHz

輸出2.3ghz點頻時,雜散在2.5ghz

輸出2.4ghz點頻

2023-12-04 07:39:16

用AD9288做GPS中頻采樣,當輸入一個中頻15MHz -10dBm的電頻干擾時,62MHz采樣時鐘,對62000采樣數據做FFT處理,發現幅度譜在干擾頻率附近有很多雜散,如何解決? 求大神幫忙!用AD9218效果一樣

2019-01-21 16:03:00

1GHz分頻為500MHz;該500MHz與單音輸出頻率(比如230MHz)混頻后產生了較大雜散(混出270MHz)。 請問:如何才能能降低該雜散?有沒有方法讓AD9912內部不產生sysclk的2分頻信號或降低該分頻信號帶來的干擾?

2019-03-08 15:14:23

不行。此時還沒有試輸出310MHz或者300MHz~350MHz的其它頻率。

收集資料及理解:在ADI管網搜索到的AN-1396應用里面的介紹,以及結合網上描述DDS輸出相位截斷雜散對相位噪聲

2024-12-19 07:12:59

前段時間做了一個關于AD9958的板子,輸出頻率在14MHz到22MHz,從其PDF資料上的相位噪聲曲線看,15MHz在10KHz以內的雜散非常好,而實際上做出來近端幾百Hz的雜散最差的只有80左右

2019-02-22 08:27:59

我使用ADF4351,其輸出在中心頻率偏移184k附近有雜散輸出,通過減小環路帶寬,減小充電電流等,雜散有一定的降低, 此時帶來靠近中心頻率出的噪聲升高,通過對比不同的板卡,都存在類似的現象,環路

2018-10-12 09:24:23

在使用DAC39J82過程中我們發現DAC芯片在輸出是0—500M頻率信號時,在120MHZ以下沒有沒有雜散問題。在150M,200M,300M 頻率下也沒有雜散問題。但在140M有雜散,雜散出

2024-11-22 06:07:12

DC/DC開關電源的開關頻率雜散有什么有效的解決方法沒有?在其后加多級LDO都不能很好的解決。尋找一種能夠通過電感或電容的解決方案。開關頻率在幾百KHz左右的。

2024-01-08 07:25:39

IOUPDATE來更新。寫法如下:第一個脈沖寫16384,第二個寫32768,第三個為49152,第四個為0,即進行周期性相位累加。這樣的操作會導致頻譜整體偏移,偏移量為1/4脈沖頻率,即25K,因為每次步進的相位

2018-08-30 11:49:24

在測試評估版時,不同頻率下整數邊界雜散差別很大。

下表是100M鑒相頻率下,偏離1M的雜散抑制:

頻率320133013401350136013701380139014001

雜散

2024-11-13 07:43:14

我的參考頻率為80MHz,鑒相頻率為160MHz,現在雜散為80 的整數倍,是否為整數邊界雜散?如何降低整數邊界雜散?如何計算哪些點的整數邊界雜散高?哪些點的整數邊界雜散低?

2024-11-11 08:02:42

LMX2595輸出頻率7.5-15GHz范圍內偏移載波50Hz的地方有固定雜散,幅度在58dBc左右;不管是整數模式還是小數模式都有;

但是7.5GHZ以下則沒有這個雜散,但是它的2次諧波有這個雜散;我想問一下有誰遇到這個問題嗎?

2024-12-12 06:14:12

,還望詳述)來達到盡量減小此雜散的作用,最好能到-50dBc以下。因為我最終是想將此款芯片用在寬頻帶輸出上,所以對于某個特定頻點通過改變鑒相頻率來達到遠離Fpfd整數倍的目的之法并不適用,如本例中若取

2018-09-04 11:35:47

每隔3KHz存在雜散,無法通過降低信號功率,改變時鐘數據相位來改善

更改參考時鐘為60MHz,雜散間隔變為15K

更改參考時鐘為20MHz是,雜散消失

請問各位大神這個問題應該怎么考慮,謝謝

另外當去掉DAC輸出輔助之后用示波器測試波形如下,這種現象是信號發生反射了嗎?

2023-12-07 07:09:55

直接數據頻率合成器(DDS)因能產生頻率捷變且殘留相位噪聲性能卓越而著稱。另外,多數用戶都很清楚DDS輸出頻譜中存在的雜散噪聲,比如相位截斷雜散以及與相位-幅度轉換過程相關的雜散等。此類雜散是實際

2023-12-15 07:38:37

假設您已經通過迭代信息傳遞相位邊限和回路帶寬在鎖相環(PLL)上花費了一些時間。但遺憾地是,還是無法在相位噪聲、雜散和鎖定時間之間達成良好的平衡。感到泄氣?想要放棄?等一下!你是否試過伽馬優化參數?

2019-07-31 07:26:15

David Brandon簡介直接數據頻率合成器(DDS)因能產生頻率捷變且殘留相位噪聲性能卓越而著稱。另外,多數用戶都很清楚DDS輸出頻譜中存在的雜散噪聲,比如相位截斷雜散以及與相位-幅度轉換

2018-11-01 11:24:06

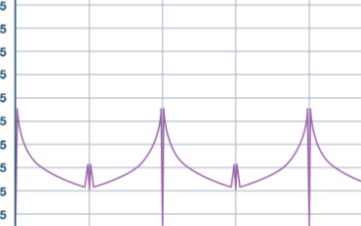

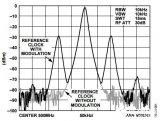

消除它們。但這種方法可減少整數邊界雜散及其產生的其它雜散。 圖3中的“雜散消失”路徑展示了使用該可編程倍頻器的效果。100kHz頻率下的整數邊界雜散大約減少了9dB,同時還大大減少了50kHz和10kHz

2018-09-06 15:11:00

經常容易搞錯AM,FM或PM,他們很難區分呢?時鐘相位噪聲圖中的雜散信號為什么會影響時鐘的總抖動?

2021-03-05 08:06:14

傳導和輻射雜散的FCC限值是什么情況,沒看懂,求指點。另外,2G和3G的雜散測試,除了測試頻率范圍不同外,還有哪些不同,提前謝謝大神!!!!!!!

2013-03-10 21:38:03

小弟正在調試一款X波段(9.6-10.8GHz)的鎖相環,采用的是內部集成VCO的HMC778LP6CE芯片。在調試中,我發現在距中心頻率50Hz整數倍的頻率處有很多雜散,請問各位大神這些雜散

2014-07-21 15:47:54

要求的不同,有多種處理此類問題信號的方法。謹慎的頻率規劃和濾波雖然能夠有助于大幅度減少雜散脈沖的數量,但是它們總是會有。因此,系統設計師必需在混頻器輸出端上準確地測量雜散電平,以確定怎樣用最佳的方式應對它們,這一點是很重要。

2019-07-23 08:17:34

值、管地電位波動、管道附近的土壤電位梯度和管道中的電流值四種方法判斷是否存在雜散電流干擾。表1 我國直流干擾程度判斷標準 管地電位正向偏移值(mV) 直流干擾程度

2020-12-01 16:22:35

直接數據頻率合成器(DDS)因能產生頻率捷變且殘留相位噪聲性能卓越而著稱。另外,多數用戶都很清楚DDS輸出頻譜中存在的雜散噪聲,比如相位截斷雜散以及與相位-幅度轉換過程相關的雜散等。此類雜散是實際

2018-08-27 11:34:36

兩個增益和相位圖像雜散及一個失調雜散(圖5)。可在2/3 × 奈奎斯特頻率時看到失調雜散,但在這種情況下,失調雜散并非SFDR的主要貢獻因素。SFDR限制增益和相位雜散可在(2/3 × 奈奎斯特頻率

2018-11-01 11:31:37

ADF4351輸出,相噪遠不及器件參考值理想。而且在離中心頻率最近處的雜散出現在偏離中心頻率5KHz的地方。從頻譜來分析,我估計如果能減小或者消除該雜散,則相噪應該可以明顯變好。電源我采用了兩顆

2018-09-29 15:40:47

ADF4355,采用100MHz OCXO作為參考,輸出2280MHz,鑒相頻率100MHz,近端出現70Hz左右(及其倍數)的雜散,抑制度在47dBc左右,CP電流設置0.3mA,調整Bleed

2018-08-22 10:40:08

您好,請問我在做ADF4356鎖相環時發現在PFD諧波處有較強雜散,高達-75dBc,可以看成就是整數邊界雜散,但是雜散距離中心頻率已經有了15M左右,環路帶寬40KHz,請問一下這是什么原因導致

2019-02-15 13:26:51

各位好我在看模擬對話的時候,看到邊帶雜散和開關雜散不太明白,請問大家這其中的含義以及它將導致什么后果?謝謝大家了!!!

2019-01-09 09:29:01

我在看ADC供電部分的時候,看到邊帶雜散和開關雜散這兩詞不知道它的含義。請問下大家它們的含義以及它們將會對電路造成什么影響?

謝謝大家了!!!!!

2024-12-31 06:32:31

此范圍會有利于鎖定時間和10kHz相位噪聲,但是會降低雜散和1MHz偏移的相位噪聲。因此,選擇環路帶寬的一種較好的方法是先選擇最優抖動帶寬(BWJIT),然后增加帶寬提高鎖定時間或低頻偏相位噪聲,或者降低帶寬提高高頻偏相位噪聲或雜散。

2018-08-29 16:02:55

了,最好能抑制再高些。 常用的抑制鑒相頻率雜散的方法是環路濾波器的多級設計,如3級。在鑒相頻率固定、3級環路濾波器固定且濾波器帶寬已經10KHz不能再低的條件下,還有哪些方法可以改善上面提到的這些雜散呢

2018-11-07 09:03:01

EVAL-AD4003FMCZ。結論針對系統應用中高分辨率、精密ADC的雜散問題,本文探討了判斷其根本原因的方法。文中介紹了在五種不同應用情況下消除或降低雜散的特定設計解決方案。本文還探討了相關的雜散計算方法

2018-10-19 10:38:17

提出了一種基于改進型三重調節算法的高分辯率率,低雜散的頻率合成方法,采DDS AD9850研制實現了在92.1-120.499MHZ即保證信號高分辯率又能夠改善其雜散指標的頻率合成器。

2009-02-27 09:22:42 21

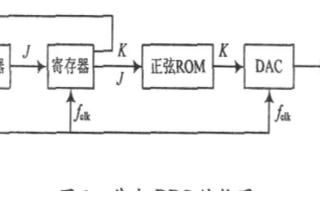

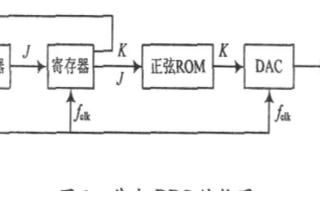

21 直接數字頻率合成(DDS)技術推動了頻率合成領域的高速發展,但固有的雜散特性極大的限制了其應用發展。在分析DDS工作原理及雜散噪聲來源的基礎上,介紹了幾種雜散抑制的方法,

2010-07-31 10:36:19 32

32 雜散特性是制約DDS(直接數字頻率合成)技術進一步應用和發展的重要因素,其相位舍位、幅度量化和DAC(數模轉換器)的非理想特性等是影響DDS輸出頻譜質量的主要雜散源。文中對

2010-10-20 16:34:46 38

38 雜散特性限制著直接數字頻率合成(DDS)技術的應用和發展,其中相位舍位、幅度量化和DAC的非理想特性等是影響DDS輸出頻譜質量的主要雜散源。文中主要研究相位舍位對DDS輸出頻

2010-10-20 16:35:31 28

28 在研究基本相位擾動法的基礎上,提出了一種新的二階相位擾動法,該方法可使雜散分量的抑制達到每相位位18 dB。因此在同樣雜散精度的要求下,使用該方法的設計可以減少ROM尋址的位

2011-08-19 10:45:45 2950

2950

直接數字頻率合成器(DDS) 相位截斷誤差序列是DDS 輸出信號誤差的主要來源,很有必要對DDS 相位截斷誤差序列的譜進行研究。文獻[1 ]提出了DDS 相位截斷雜散譜的精確分析方法,該文對DDS

2011-08-29 16:41:52 21

21 系統地研究了快速跳頻PLL 中雜散來源,給出了環路雜散模型,定義了雜散抑制比。定性分析了MF2SK2FH 通信系統檢測誤碼率Pe 與雜散抑制比之間的關系,并通過計算機輔助分析,定量計算出誤

2011-09-01 16:30:45 46

46 雜散抑制是PLL 頻率合成器的幾個關鍵指標之一。在實際設計中,雜散的輸出種類比較多,產生的原因也各不一樣,但是它們中的大多數并不常見。首先從雜散的基本概念出發,詳細地介紹了

2011-09-01 16:34:56 69

69 針對頻率源的相噪會惡化采樣數據的信噪比,雜散會降低接收機靈敏度,提出了一種低相噪低雜散的設計方法。該方法利用Hittite公司的新推出的集成VCO的鎖相環芯片HMC830進行設計,供電

2011-10-25 17:29:13 188

188 直接數據頻率合成器(DDS)因能產生頻率捷變且殘留相位噪聲性能卓越而著稱。另外,多數用戶都很清楚DDS輸出頻譜中存在的雜散噪聲,比如相位截斷雜散以及與相位-幅度轉換過程相關的

2012-02-02 10:41:21 44

44 LMX2531 系列產品被廣泛應用于無線通訊基站系統,相比較整數分頻,采用小數分頻可以獲得更好的相位噪聲性能,但是小數分頻會導致雜散問題,特別是整數邊界雜散尤為突出。本文介紹一種在盡可能保證相位噪聲性能的基礎上,改善整數邊界雜散達10dB。

2013-04-27 15:51:04 3492

3492 新大管道雜散電流干擾影響研究新大管道雜散電流干擾影響研究

2015-11-16 14:43:22 0

0 為了能既方便又明白地表示一個信號在不同頻率下的幅值和相位,可以采用成為頻譜圖的表示方法。在傅里葉分析中,把各個分量的幅度|Fn|或 Cn 隨著頻率nω1的變化稱為信號的幅度譜。而把各個分量的相位 φn 隨角頻率 nω1 變化稱為信號的相位譜。

2016-09-18 18:17:58 176630

176630

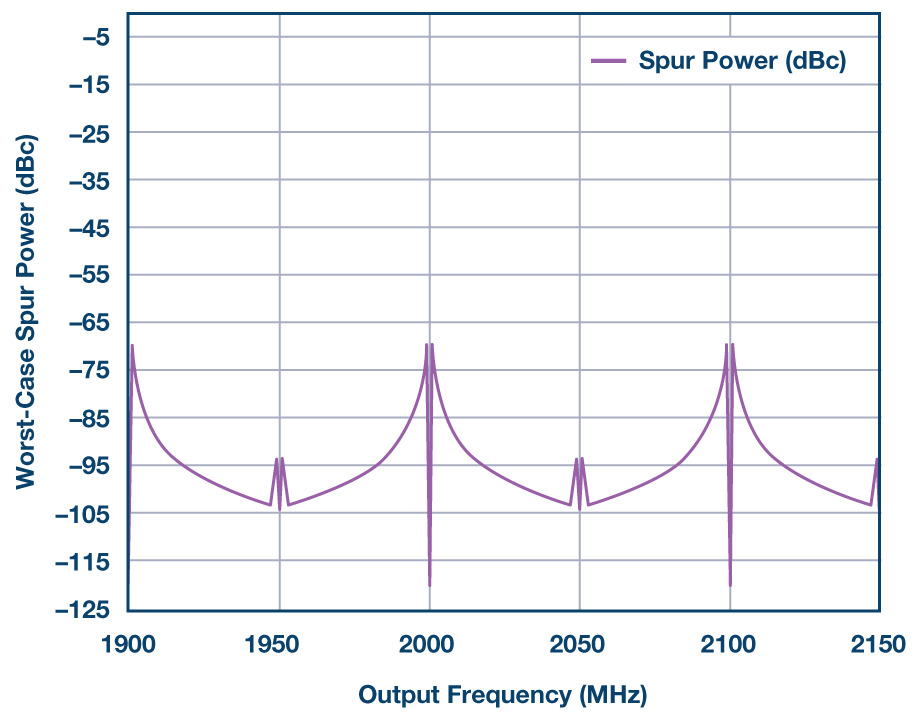

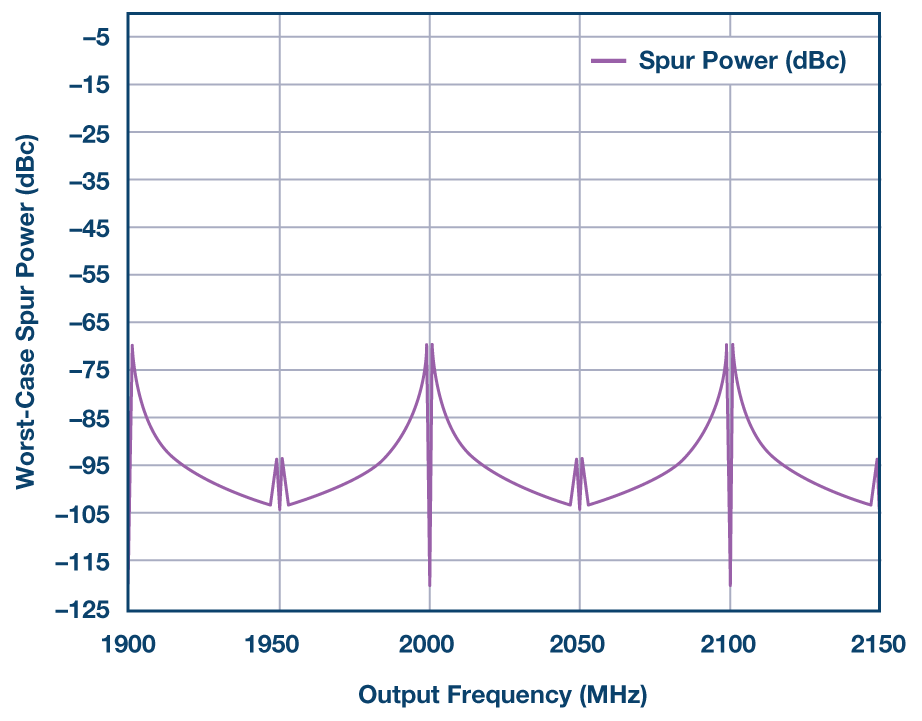

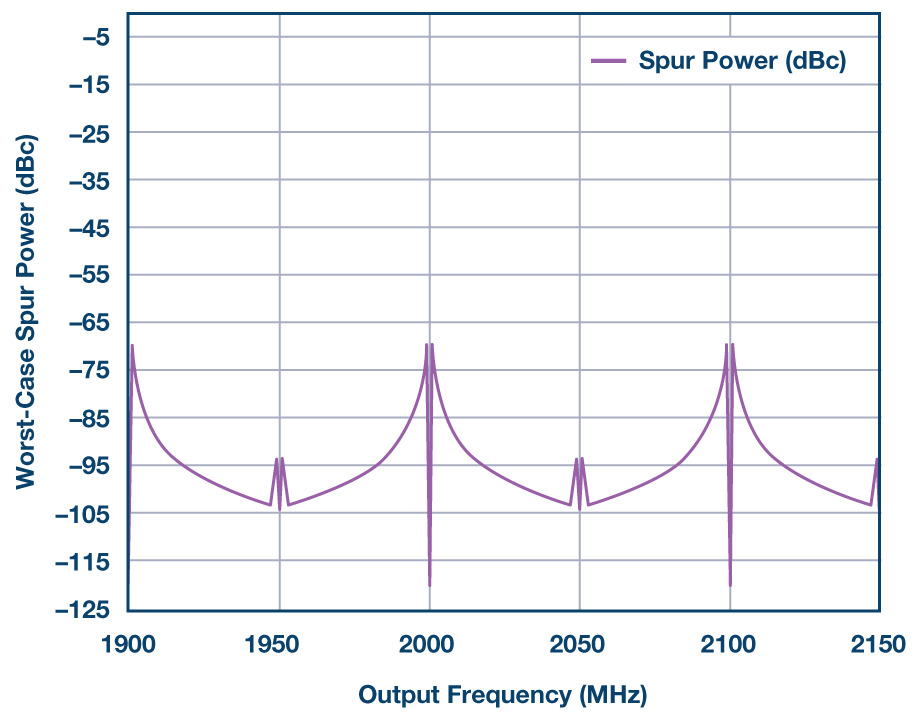

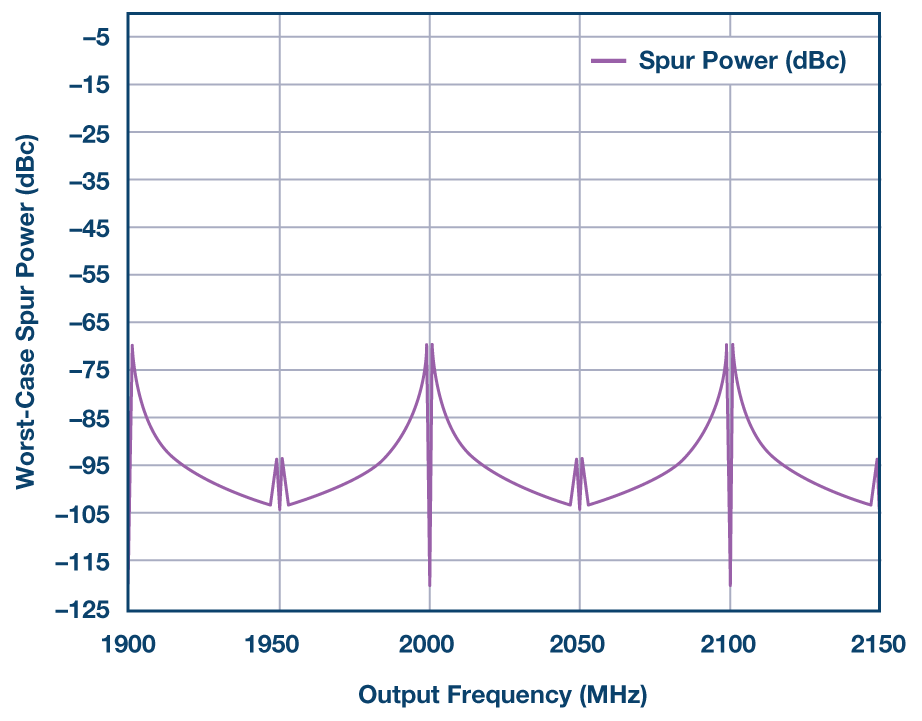

您曾設計過具有分數頻率合成器的鎖相環(PLL)嗎?這種合成器在整數通道上看起來很棒,但在只稍微偏離這些整數通道的頻率點上雜散就會變得高很多,是吧?如果是這樣的話,您就已經遇到過整數邊界雜散現象了 該現象發生在載波的偏移距離等于到最近整數通道的距離時。

2017-04-08 03:56:11 5057

5057

直接數據頻率合成器(DDS)因能產生頻率捷變且殘留相位噪聲性能卓越而著稱。另外,多數用戶都很清楚DDS輸出頻譜中存在的雜散噪聲,比如相位截斷雜散以及與相位-幅度轉換過程相關的雜散等。此類雜散是實際DDS設計中的有限相位和幅度分辨率造成的結果。

2018-07-10 06:50:00 15073

15073

現代直接數字頻率合成器(DDS)通常利用累加器和數字頻率調諧字(FTW)在累加器輸出端產生周期性的N位數字斜坡(見圖1)。此數字斜坡可依據公式1定義DDS的輸出頻率(fO),其中fS為DDS采樣速率

2017-09-12 18:59:00 9

9 現代直接數字頻率合成器(DDS)通常利用累加器和數字頻率調諧字(FTW)在累加器輸出端產生周期性的N位數字斜坡(見圖1)。 此數字斜坡可依據公式1定義DDS的輸出頻率(fO),其中fS為DDS采樣

2017-11-10 15:49:23 0

0 提取母排雜散電感具有抗噪聲能力強、計算結果對波形形狀不敏感等優點,然而在簡單的積分運算中積分時限的選取對計算結果有較大的影響。提出一種優化的積分形式的母排雜散電感的提取方法,在傳統積分法的基礎上考慮雜散電

2018-01-23 15:09:27 15

15 ,結合對母排中電流流通路徑的分析,建立了不同母排結構與雜散電感大小之間的關系,提出了一種基于改善電流流通通道的低感母排結構優化方法。利用該方法對現有的一臺有源電力濾波器母排進行了優化設計,采用雙脈沖法實驗對優化

2018-03-07 16:25:15 4

4 鎖相環 (PLL) 和壓控振蕩器 (VCO) 輸出特定頻率的RF信號,理想情況下此信號應當是輸出中的唯一信號。但事實上,輸出中存在干擾雜散信號和相位噪聲。本文討論最麻煩的雜散信號之一——整數邊界雜散——的仿真與消除。

2019-04-12 08:32:00 13125

13125

在第二部分中,我們將側重于詳細考察與PLL相關的兩個關鍵技術規格:相位噪聲和參考雜散。導致相位噪聲和參考雜散的原因是什么,如何將其影響降至最低?討論將涉及測量技術以及這些誤差對系統性能的影響。我們還將考慮輸出漏電流,舉例說明其在開環調制方案中的重要意義。

2019-04-04 08:10:00 25342

25342

通過演示簡要介紹鎖相環(PLL)中可實現的領先相位噪聲和雜散性能。

2019-05-21 06:23:00 6527

6527 直接數據頻率合成器(DDS)因能產生頻率捷變且殘留相位噪聲性能卓越而著稱。另外,多數用戶都很清楚DDS輸出頻譜中存在的雜散噪聲,比如相位截斷雜散以及與相位-幅度轉換過程相關的雜散等。此類雜散是實際DDS設計中的 有限相位和幅度分辨率造成的結果。

2019-11-14 17:10:08 6715

6715

由于跳頻技術在軍事上的廣泛應用,因此對于其核心直接數字式頻率合成器的研究成為人們關注的熱點。直接數字式頻率合成器的基本原理是利用輸入信號本身相位差的不同給出不同的電壓幅度,最終濾波平滑輸出需要的頻率。設計一個直接數字式頻率合成器最大的問題就是雜散抑制。這是評價頻率合成器設計是否優良的重要指標。

2020-08-05 14:34:22 12747

12747

鎖相環 (PLL) 和壓控振蕩器 (VCO) 輸出特定頻率的RF信號,理想情況下此信號應當是輸出中的唯一信號。但事實上,輸出中存在干擾雜散信號和相位噪聲。本文討論最麻煩的雜散信號之一——整數邊界雜散——的仿真與消除。

2020-09-09 10:09:56 4998

4998

AN-1396: 如何預測直接數字頻率合成器(DDS)輸出頻譜中主相位截斷雜散的頻率和幅度

2021-03-21 00:44:05 2

2 換流回路中的雜散電感會引起波形震蕩,EMI或者電壓過沖等問題。因此在電路設計的時候需要特別留意。本文給出了電路雜散電感的測量方法以及模塊數據手冊中雜散電感的定義方法。 圖1為半橋電路的原理電路以及

2021-10-13 15:36:13 5840

5840

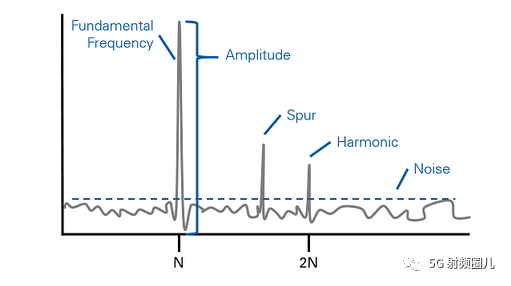

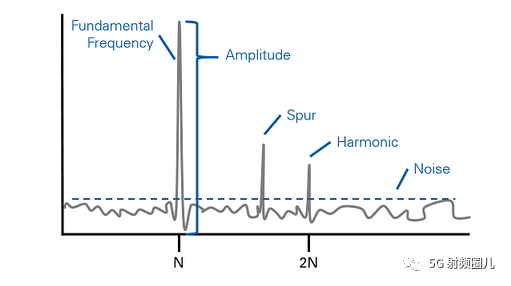

對無線電管理工作來說,雜散發射是產生干擾的重要原因 . 在無線電發射設備檢測過程中,雜散測試是一個重要的必測項目。雜散是指在工作帶寬外某個頻點或某些頻率上的發射,其發射電平可降低但不影響相應的信息傳遞。包括:諧波發射、寄生發射、互調產物、以及變頻產物,但帶外發射除外。

2022-09-16 15:49:55 5437

5437 發現抖動、相位噪聲、鎖定時間或雜散問題?請檢查鎖相環的環路濾波器帶寬

2022-11-02 08:16:24 15

15 電力變壓器鐵芯雜散損耗為鐵芯負載損耗中的特例,故單獨討論降低它的方法。電力變壓器鐵芯雜散損耗包括結構件(鐵芯夾件、屏蔽環等)的損耗;穿過導體地方(套管座)損耗;平行導體(通過大電流的引線)的損耗和油箱損耗。降低鐵芯雜散損耗的方法主要有以下幾種方法。

2022-11-09 09:34:59 4910

4910 鎖相環(PLL)和壓控振蕩器(VCO)以特定頻率輸出RF信號,理想情況下,該信號將是輸出端存在的唯一信號。實際上,輸出端存在不需要的雜散信號和相位噪聲。本文討論如何仿真和消除一種更麻煩的雜散信號——整數邊界雜散。

2023-01-08 15:40:42 3309

3309

作為最重要的設計參數之一,選擇環路帶寬涉及到抖動、相位噪聲、鎖定時間或雜散之間的平衡。適合抖動的最優環路帶寬BWJIT也是數據轉換器時鐘等許多時鐘應用的最佳選擇。如果BWJIT并非最佳選擇,首先要做的仍是尋找最優環路帶寬。

2023-04-12 10:32:17 3831

3831

雜散干擾主要是由于接收機的靈敏度不高造成的。 發射機輸出信號通常為大功率信號,在產生大功率信號的過程中會在發射信號的頻帶之外產生較高的雜散。 如果雜散落入某個系統接收頻段內的幅度較高,則會導致接收

2023-05-08 16:18:38 3278

3278

直接數據頻率合成器(DDS)因能產生頻率捷變且殘留相位噪聲性能卓越而著稱。另外,多數用戶都很清楚DDS輸出頻譜中存在的雜散噪聲,比如相位截斷雜散以及與相位-幅度轉換過程相關的雜散等。此類雜散是實際

2023-08-21 18:20:01 1430

1430

一站式PCBA智造廠家今天為大家講講如何減少PCB雜散電容的影響?減少PCB雜散電容的PCB設計方法。當提到PCBA上的電子電路時,經常使用的術語是雜散電容。PCB上的導體、無源器件的預制電路板

2023-08-24 08:56:32 1436

1436 電子發燒友網站提供《基于HMC830的低相噪低雜散頻率源的設計.pdf》資料免費下載

2023-10-25 14:20:38 7

7 什么是無雜散動態范圍 (SFDR)?為什么SFDR很重要? 無雜散動態范圍(SFDR)是指模擬信號中最大的無雜散動態范圍。它是在硬件設備中測量的。它是指能夠測量的模擬信號的最大幅度范圍,其中沒有雜散

2023-10-31 09:34:29 10715

10715 電子發燒友網站提供《用于計算特定相位截斷雜散的頻率和幅度的方法.pdf》資料免費下載

2023-11-28 11:32:12 0

0 變頻器控制引起的電機軸電壓雜散? 變頻器(簡稱VFD)是通過調整輸入電源頻率和電壓來控制電機轉速的裝置。它在工業控制應用中得到廣泛應用,可以提高能效和精度,并減少能源消耗。然而,變頻器控制引起的電機

2024-02-01 14:08:21 1619

1619 說到射頻的難點不得不提雜散,雜散也是射頻被稱為“玄學”的來源。雜散也是學習射頻必經的一個難點。本篇文章就來講一下雜散。

2024-11-05 09:59:34 6929

6929

電子發燒友網為你提供()無雜散、50 MHz 至 2.1 GHz 單通道小數 N 分頻頻率合成器相關產品參數、數據手冊,更有無雜散、50 MHz 至 2.1 GHz 單通道小數 N 分頻頻率合成器

2025-05-23 18:30:22

什么是晶振的雜散電容?晶振的雜散電容,也叫做寄生電容,是指電路中非人為設計、由物理結構自然產生的、有害的隱藏電容。它為什么重要?(影響)雜散電容之所以關鍵,是因為它會直接影響晶振的振蕩頻率精度。核心

2025-11-13 18:13:41 225

225

電子發燒友App

電子發燒友App

評論