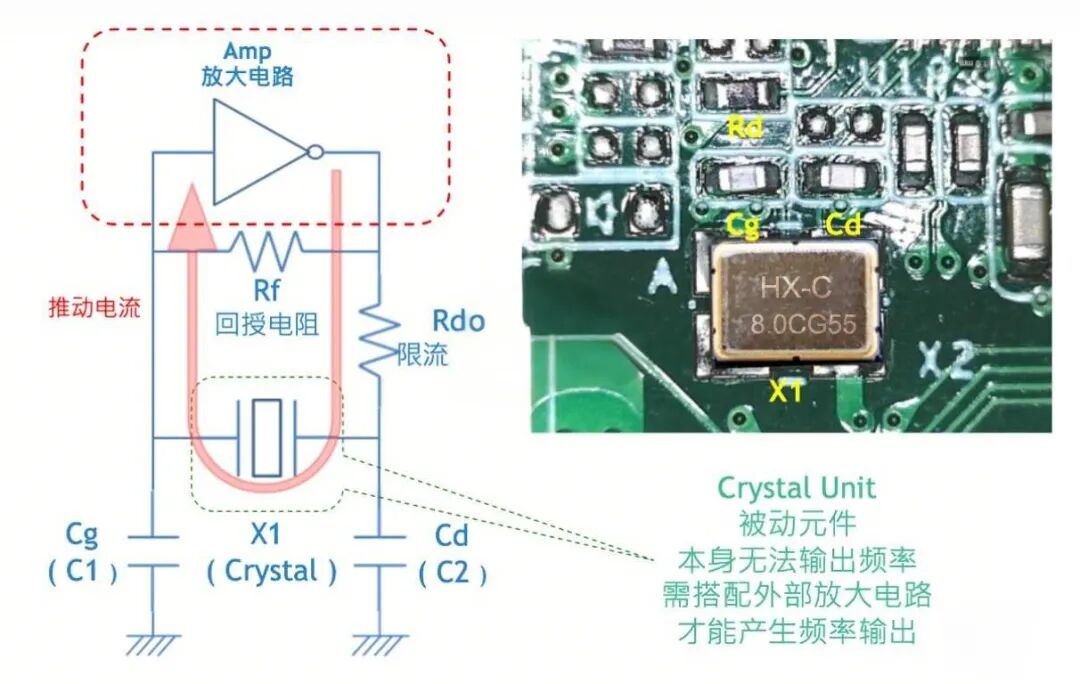

什么是晶振的雜散電容?

晶振的雜散電容,也叫做寄生電容,是指電路中非人為設計、由物理結構自然產生的、有害的隱藏電容。

它為什么重要?(影響)

雜散電容之所以關鍵,是因為它會直接影響晶振的振蕩頻率精度。

核心關系在于“負載電容”的計算公式:

C_Load = (C1 * C2) / (C1 + C2) + C_stray

C_Load:晶振正常工作需要的總負載電容(例如 12.5pF 或 9pF)。

C1, C2:你在電路板上為晶振焊接的兩個外部匹配電容。

C_stray:總的雜散電容。

如何應對?

如何應對雜散電容?

既然無法消除,工程師們通過以下方法來管理和補償它:

在設計中估算:這是最關鍵的一步。根據PCB板材和布局經驗,雜散電容通常被估算在2pF 到 5pF之間。在計算C1和C2的值時,需要從目標負載電容中減去這個估算值。

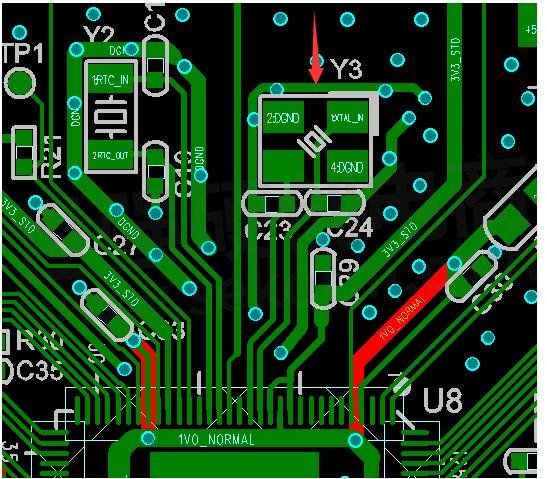

優化PCB布局:

縮短走線:盡可能縮短晶振到芯片引腳的走線長度,這是最有效的方法。

避免平行走線:晶振的兩條走線應避免長距離平行布線。

使用接地護環:在晶振走線周圍布置接地線,可以固定并屏蔽雜散電容。

測試與微調:在樣品階段,通過測量實際輸出頻率,可以輕微調整C1和C2的容值來補償雜散電容帶來的頻率偏差。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

晶振

+關注

關注

35文章

3587瀏覽量

73611 -

寄生電容

+關注

關注

1文章

302瀏覽量

20323 -

雜散電容

+關注

關注

0文章

18瀏覽量

1580

發布評論請先 登錄

相關推薦

熱點推薦

PCB雜散電容大小計算方法 PCB雜散電容怎么消除

在整個PCBA生產制造過程中, PCB 設計是至關重要的一部分,今天主要是關于 PCB 雜散電容、影響PCB 雜散

發表于 09-11 09:41

?3024次閱讀

高速TIA如何減小雜散電容Cstrayne ?

對于高速TIA的PCB來說,最大的挑戰就是如何減小雜散電容Cstray了** 。這是為什么呢?假如帶寬很高,增益很高,那么Cf可能需要設置在如0.5pF,而普通貼片電阻的雜

什么是晶振的雜散電容?

什么是晶振的雜散電容?

評論