CanTrcv模塊在上電后的初始狀態(tài)配置,一般配置初始狀態(tài)為SLEEP狀態(tài)。而后,CanTrcv模塊的狀態(tài)通過其他模塊調(diào)用CanTrcv_SetOpMode來切換。

2022-10-31 10:58:09 3673

3673 霍爾傳感器是在與磁場接觸時(shí)在其輸出端產(chǎn)生電信號(hào)的傳感器。傳感器輸出端電信號(hào)的模擬值是磁場強(qiáng)度的函數(shù)。如今,霍爾傳感器無處不在,它們出于不同的原因被用于從手機(jī)到開關(guān)的各種設(shè)備中,用于測量汽車和其他

2022-11-16 17:16:06 3470

3470

我使用的是ISE 14.5。我正在嘗試將ngc文件添加到項(xiàng)目中。此ngc是使用兩個(gè)Xilinx內(nèi)核DPRAM和RAM的自定義設(shè)計(jì)生成的。當(dāng)我將生成的ngc包含到項(xiàng)目中時(shí),會(huì)報(bào)告以下錯(cuò)誤。請幫我

2020-03-13 09:35:50

用STM32做開發(fā),一般在什么類型的項(xiàng)目中會(huì)用到傅立葉變換呢?

2017-09-18 19:32:13

我在附加軟件的 CubeMX 項(xiàng)目中包含了 CMSIS-DSP 庫。使用庫設(shè)置而不是源。但是,當(dāng)我嘗試從 arm_math.h 調(diào)用函數(shù)時(shí),編譯器會(huì)拋出一個(gè)錯(cuò)誤,指出無法找到該函數(shù)調(diào)用。有任何想法嗎?我怎樣才能包括 CMSIS-DSP。我正在使用 GCC 編譯器和 STMCubeIDE

2023-02-01 08:05:23

如果采用dna加密,讀取每塊fpga的id,在允許的范圍內(nèi)就輸出使能信號(hào)驅(qū)動(dòng)算法模塊,就是在開發(fā)時(shí)將客戶提供的id預(yù)先存入ram,重新綜合成ngc文件給用戶。這種方法有幾個(gè)問題想請教各位

2012-05-02 17:54:53

FPGA問題求助:請問怎樣工程一中調(diào)用其他工程(工程二)已經(jīng)實(shí)現(xiàn)好的功能,工程二的的模塊是實(shí)列化的形式,分為頂層模塊和功能模塊 是直接就將工程二的頂層文件模塊和功能模塊完全拷到工程一的目錄下,通過

2015-07-16 21:22:04

需要注意的就是,從項(xiàng)目中刪除項(xiàng)并不會(huì)在磁盤中刪除相應(yīng)文件。創(chuàng)建可執(zhí)行程序、安裝包、DLL以及壓縮文件 在項(xiàng)目中,可以把VI程序創(chuàng)建成可以運(yùn)行的軟件產(chǎn)品。要完成這個(gè)操作,可以在創(chuàng)建可執(zhí)行文件設(shè)定

2019-05-24 07:40:04

我從Xilinx Vivado 2015.2生成了一個(gè)FIFOIP。但我無法在Xilinx ISE 14.7中看到合成設(shè)計(jì)所需的.NGC文件。如何生成設(shè)計(jì)的.NGC文件?需要Alsowhich文件才能在生成的IP的ModelSim中運(yùn)行模擬。

2020-04-24 09:40:03

XY圖中的數(shù)據(jù)怎樣保存下來并在其他時(shí)候讀出并顯示出來

2012-10-10 10:34:31

在工程項(xiàng)目中常常使用xilinx的IP時(shí)常會(huì)遇到一些加密的verilog和vhdl,打開后是以Xlx開始的十六進(jìn)制文件,某些IP中的tcl和ttcl也是用這種方式保存的十六進(jìn)制文件。vivado中使用這些文件都沒有什么問題,就想知道這些文件是如何產(chǎn)生出來的?

2021-06-20 17:50:58

)通過外部 IDE (如VC++)創(chuàng)建DLL 項(xiàng)目并編譯生成.dll文件。 d)在 LabVIEW 項(xiàng)目中使用 DLL 中的函數(shù)。 以下章節(jié)將通過實(shí)例對(duì)這兩種情況詳細(xì)進(jìn)行敘述。希望通過本書的學(xué)習(xí),能夠是大家掌握dll調(diào)用,并在實(shí)踐中練習(xí)使用dll調(diào)用。

2011-10-27 11:20:40

使用 osThreadFlagsSet 函數(shù)為其他任務(wù)設(shè)置標(biāo)志。在調(diào)試時(shí)我注意到 osThreadFlagsSet 函數(shù)返回不同的值。在一個(gè)項(xiàng)目中,rflags 變量的值等于 1: 在其他 rflags

2022-12-09 06:55:44

就是把HDL語言/原理圖轉(zhuǎn)換為綜合網(wǎng)表的過程。2. 什么是綜合網(wǎng)表?綜合網(wǎng)表就是綜合的結(jié)果啦。綜合網(wǎng)表的業(yè)界標(biāo)準(zhǔn)是EDIF格式。文件后綴通常為.edn, .edf, .edif。EDIF網(wǎng)表是可以用

2018-08-08 10:31:27

中使用加密文件。 Verilog HDL 和 VHDL 的加密密鑰相同。您可以使用與非加密模塊相同的方法將參數(shù)傳遞給加密模塊的實(shí)例化。 只有使用第三方工具的文件加密需要公共加密密鑰。使用英特爾

2022-02-23 12:27:05

單片機(jī)加密方法在最近一個(gè)項(xiàng)目中,急急忙忙把功能完成就給了客戶,完全沒有安全意識(shí),現(xiàn)在用燒錄器把Flash里的程序一讀,我就慌了,完全沒有加密,隨隨便便就把程序讀出來了,那我干了一個(gè)月的活,被人家花

2021-07-01 08:23:00

組件。我需要按塊從相機(jī)發(fā)送照片,所以我需要將每個(gè)塊都以二進(jìn)制格式放置。在 ESP-IDF 項(xiàng)目中使用 BSON 有什么想法嗎?

2023-03-01 06:30:38

我在proj_lab10e的項(xiàng)目中了添加CAN.h文件,然后在hal.h中編寫了InitECana函數(shù),在再main函數(shù)中調(diào)用,編譯時(shí)出現(xiàn)error #10234-D: unresolved

2020-07-22 09:50:55

如何把libview集成到其他web工程項(xiàng)目?libview提供了自己的web服務(wù),但是希望把libview的視圖集成到web工程項(xiàng)目,是否可行請各位指教?如果不能直接集成,libview是否可以

2022-07-18 12:54:15

如題,如何將自己做的項(xiàng)目中的所有子vi打包成庫類,方便以后用到的時(shí)候調(diào)用?因?yàn)楝F(xiàn)在做了挺多的項(xiàng)目,其中有很多都是用的寫好的功能的子vi,每次寫新的項(xiàng)目的時(shí)候都要重新復(fù)制到新的項(xiàng)目中有些麻煩,而且

2017-11-23 16:33:37

如何從MLA到我的項(xiàng)目中獲得代碼。我可以看到MIWI的功能,但如何在我的項(xiàng)目中使用它們呢?

2020-05-07 12:01:36

將哪些文件復(fù)制到項(xiàng)目中。在詢問之前,我試圖將xxx.vhd和.ngc文件復(fù)制到我的項(xiàng)目中dds編譯器模塊實(shí)例。但是在合成步驟。 ise告訴我第385行找不到模塊/原語'dds_compiler_v4_0'....請幫我解決這個(gè)問題

2020-04-01 09:40:21

組件。我需要按塊從相機(jī)發(fā)送照片,所以我需要將每個(gè)塊都以二進(jìn)制格式放置。在 ESP-IDF 項(xiàng)目中使用 BSON 有什么想法嗎?

2023-04-14 06:59:28

你好,我想在我的項(xiàng)目中使用停止模式。有什么例子嗎?我想讓我的外圍模塊在初始化時(shí)停止模式。如果用戶將喚醒按鈕,模塊醒來并開始廣告。模塊進(jìn)入停止模式,再然后preconfiguredtimeout已過期。

2019-09-25 14:58:24

嗨,我有兩個(gè)獨(dú)立的工作項(xiàng)目,并希望將它們合并在一起。我將一個(gè)項(xiàng)目的頂級(jí)聲明為其他項(xiàng)目中的一個(gè)組件并實(shí)例化它或者只是在其他項(xiàng)目中實(shí)例化一個(gè)實(shí)體。我將一個(gè)項(xiàng)目的完整文件夾作為源添加到其他vivado處理

2020-05-19 08:39:40

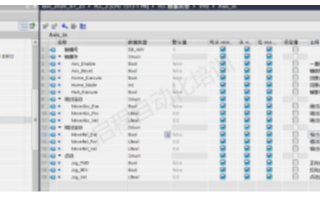

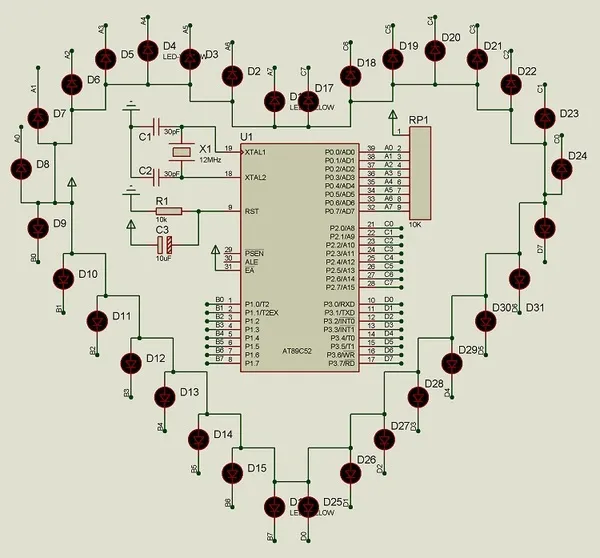

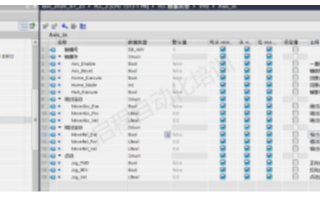

的設(shè)計(jì)應(yīng)用到項(xiàng)目中,如圖:

我主要是用SHARP系列的,369,489

想要這樣的設(shè)計(jì)圖應(yīng)用到項(xiàng)目中要怎樣,去做呢?

是否只能用VDSP++去加到項(xiàng)目,CCES可以否?

要怎樣設(shè)置配置工程?

想要一個(gè)詳細(xì)的過程?

有什么指導(dǎo)文檔?

2023-11-30 08:01:05

。但我不會(huì)在項(xiàng)目中使用MISO PIN,我不想為SPI的MISO指派任何PIN。當(dāng)我嘗試不分配時(shí),在編譯操作后,編譯器自動(dòng)分配。我能做什么?PSOC4 SCB模塊(VER 3.10)沒有SPI的雙向選擇。你能告訴我,我能做什么使用SPI模塊只有3個(gè)引腳(MOSI,SS,SCK)?提前感謝

2019-10-21 11:31:34

嗨,allI有ISE構(gòu)建的.NGC文件...我想在我的VIVADO 13.4設(shè)計(jì)中使用這個(gè)文件...我做了第一個(gè)僅用于合成的VIVADO項(xiàng)目...... NGC組件在這個(gè)項(xiàng)目中被黑盒子...我做了

2019-03-22 07:46:30

的.c文件,以便從應(yīng)用程序中的函數(shù)中獲取信息。如果你把你的和聲目錄與一個(gè)特定的項(xiàng)目聯(lián)系在一起,那就很好了。在開發(fā)多個(gè)系統(tǒng)時(shí),它并不理想。我更希望有一種方法將.c文件復(fù)制到我的項(xiàng)目中,并修改它,但是它是在

2019-04-28 10:57:05

芯片都預(yù)存一個(gè)8字節(jié)密碼,STM32讀取一個(gè)加密芯片生成的隨機(jī)數(shù),然后與8位密碼做一個(gè)DES運(yùn)算,把這個(gè)結(jié)果發(fā)給加密芯片比較。加密芯片用同樣的隨機(jī)數(shù)和密碼做DES運(yùn)算,結(jié)果是和STM32算出來是一樣

2016-09-09 10:39:31

SpinalTemplateSbt 項(xiàng)目作為例子,演示如何用IDEA調(diào)用Docker運(yùn)行Spinal HDL。用IDEA打開SpinalTemplateSbt項(xiàng)目,在Run菜單點(diǎn)擊Edit

2022-07-04 15:29:19

是否可以調(diào)用內(nèi)置函數(shù) (API) 來使用 AES 和 128 位密鑰加密緩沖區(qū)?

我目前正在我的ESP8266項(xiàng)目中使用 Atmel 的 AES-128 實(shí)現(xiàn),但我敢打賭ESP8266芯片的某個(gè)地方已經(jīng)有實(shí)現(xiàn)了嗎?

2024-07-12 13:41:43

我已經(jīng)為一個(gè)應(yīng)用程序運(yùn)行了 STM32CubeIDE C 項(xiàng)目。我計(jì)劃為專有通信集成一個(gè) GIT 子模塊(CPP 代碼)。是否可以將 CPP 模塊添加到現(xiàn)有的 C 項(xiàng)目中并運(yùn)行?

2022-12-06 06:24:37

使用active_hdl 12.0 仿真xilinx IP。按照文檔,在vivado中編譯好了用于active_hdl 12.0的IP庫,并在active_hdl軟件中完成添加。同時(shí)將vivado

2022-09-25 22:46:59

我的項(xiàng)目使用移植到我的 STM32L496 板的 SBSFU 模板。我需要從用戶應(yīng)用程序調(diào)用加密庫。UM2262 在 6.2.3 和 6.2.4 節(jié)中提到了加密中間件支持,但它是模糊的。是否有其他文檔可以更好地解釋,或者可能是從用戶應(yīng)用程序調(diào)用加密庫的具體示例?

2022-12-26 06:48:42

將生成加密的bit文件直接下載到FPGA可否實(shí)現(xiàn)子模塊加密?將ID驗(yàn)證與子模塊一起綜合成ngc文件,再給工程用,ngc能否被破解?

2012-04-18 10:45:22

潛水很久了,一直忙著做項(xiàng)目,把項(xiàng)目中的一些好的應(yīng)用與大家分享一下

2013-11-03 19:41:52

請教!!用win8系統(tǒng)寫的labview程序,打包后能在其他系統(tǒng)上使用嗎?

2015-09-28 17:13:30

請教下cadence和pads的PCB封裝怎么導(dǎo)出AD可用格式。或者說是把cadence和PADS的一個(gè)項(xiàng)目中使用到的PCB封裝導(dǎo)出AD可用庫?

2019-08-16 02:04:32

請問原子,我在其他型號(hào)的stm32上用位帶操作,為什么不好用呢,編譯時(shí)沒有錯(cuò)誤和警告啊?

2019-03-06 23:25:59

嗨,如何在Vivado項(xiàng)目中實(shí)例化hdl系統(tǒng)生成器輸出的多個(gè)實(shí)例?在vivado項(xiàng)目中很容易實(shí)例化一個(gè)hdl系統(tǒng)生成器輸出。當(dāng)我想將另一個(gè)實(shí)例實(shí)例化到同一個(gè)項(xiàng)目時(shí),我在合成狀態(tài)下面臨一些錯(cuò)誤。最好的祝福

2020-07-31 10:38:59

項(xiàng)目中,如圖:我主要是用SHARP系列的,369,489想要這樣的設(shè)計(jì)圖應(yīng)用到項(xiàng)目中要怎樣,去做呢?是否只能用VDSP++去加到項(xiàng)目,CCES可以否?要怎樣設(shè)置配置工程?想要一個(gè)詳細(xì)的過程?有什么指導(dǎo)文檔?

2018-10-19 09:27:31

你好,我是新來論壇的,希望我為我的問題選擇了正確的一個(gè)。如果主持人覺得這個(gè)問題最好在其他地方解決,請隨時(shí)移動(dòng)線程。我目前正在為PIC24FJ256GA106與MPLab X 3.26和XC16 1

2020-04-15 10:40:42

簡述了I2C總線的特點(diǎn);介紹了開發(fā)FPGA時(shí)I2C總線模塊的設(shè)計(jì)思想;給出并解釋了用Verilog HDL實(shí)現(xiàn)部分I2C總線功能的程序,以及I2C總線主從模式下的仿真時(shí)序圖。

2009-10-19 10:49:16 104

104 摘 要:通過設(shè)計(jì)實(shí)例詳細(xì)介紹了用Verilog HDL語言開發(fā)FPGA/CPLD的方法,并通過與其他各種輸入方式的比較,顯示出使用Verilog HDL語言的優(yōu)越性。

2009-06-20 11:51:28 2331

2331

摘要: 簡述了I2C總線的特點(diǎn);介紹了開發(fā)FPGA時(shí)I2C總線模塊的設(shè)計(jì)思想;給出并解釋了用Verilog HDL實(shí)現(xiàn)部分I2C總線功能的程序,以及I2C總線主從模式下的仿真時(shí)序圖

2009-06-20 13:17:08 7137

7137

Verilog HDL程序基本結(jié)構(gòu)與程序入門

Verilog HDL程序基本結(jié)構(gòu)

Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計(jì)的語言。用Verilog HDL描述的

2010-02-08 11:43:30 2564

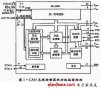

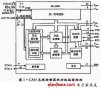

2564 在此利用Verilog HDL設(shè)計(jì)了一款CAN總線控制器,首先根據(jù)協(xié)議把整個(gè)CAN總線控制器劃分為接口邏輯管理、寄存器邏輯和CAN核心模塊3個(gè)模塊,然后用Verilog HDL硬件描述語言設(shè)計(jì)了各個(gè)功能模塊

2012-07-31 14:25:24 8908

8908

本文簡單介紹在使用Verilog HDL語言時(shí)文件的調(diào)用問題之include使用方法介紹及舉例說明,詳見本文...

2013-01-24 14:40:42 7391

7391

一直說要研究官方的例子XAP792,也確實(shí)在斷斷續(xù)續(xù)地學(xué)習(xí)著,現(xiàn)在硬件基本搞明白了,在公司也已經(jīng)做出了測試畫面。在搭建硬件平臺(tái)的時(shí)候碰到了一些問題,本文要探討的是這些問題當(dāng)中比較重要的一個(gè):如何在XPS中調(diào)用HDL語言編寫的模塊。

2017-02-09 09:31:07 2295

2295

導(dǎo)語:Method Swizzling是Objective-C中運(yùn)行時(shí)中討論較多的內(nèi)容,本文主要介紹使用Method Swizzling遇到的問題和項(xiàng)目中使用的Swizzling方案。 一

2017-09-22 19:35:20 0

0 本文檔介紹的主要內(nèi)容是數(shù)字萬用表的程序和標(biāo)準(zhǔn)模塊程序格式的詳細(xì)資料免費(fèi)下載

2018-06-08 08:00:00 28

28 HDL別墅智能解決方案能為業(yè)主帶來全方位的智能生活體驗(yàn),在該項(xiàng)目中,別墅內(nèi)日常生活所需的電氣設(shè)施都接入到HDL智能控制系統(tǒng)中,HDL為其提供照明、遮陽、供暖、空調(diào)及安防等方面的智能控制。

2018-08-16 16:08:07 666

666 本文檔的主要內(nèi)容詳細(xì)介紹的是常用模塊的Verilog HDL設(shè)計(jì)詳細(xì)資料免費(fèi)下載。

2018-10-16 11:12:54 20

20 關(guān)鍵詞:DGX , NGC , GPU , MATLAB , 深度學(xué)習(xí) 利用來自 NGC 的 MATLAB 容器加快深度學(xué)習(xí)速度 MathWorks 今天宣布為 DGX 系統(tǒng)和其他支持 NGC 平臺(tái)

2018-11-01 00:22:01 617

617 華爾街日報(bào)的最新研究顯示,通過首次代幣發(fā)行(ICO)籌集資金的加密貨幣項(xiàng)目中,超過15%的項(xiàng)目都有重大風(fēng)險(xiǎn),應(yīng)該暫停投資。該調(diào)查分析了2017年和2018年推出的3,300種加密貨幣產(chǎn)品和ICO項(xiàng)目的白皮書,其中513種可能存在剽竊行為、歪曲項(xiàng)目創(chuàng)始人身份,或承諾不切實(shí)際的回報(bào)的現(xiàn)象。

2018-12-29 11:02:44 642

642 本文檔的主要內(nèi)容詳細(xì)介紹的是Verilog HDL教程之Verilog HDL的命令格式資料說明。

2019-01-09 08:00:00 32

32 用Arduino和其他一些支持模塊,制作了這個(gè)懸停板。當(dāng)檢測到前方有障礙物時(shí)自動(dòng)停止,危險(xiǎn)LED(紅色LED)亮起,用來搬運(yùn)物品效果杠杠滴!

2019-05-22 06:37:00 2172

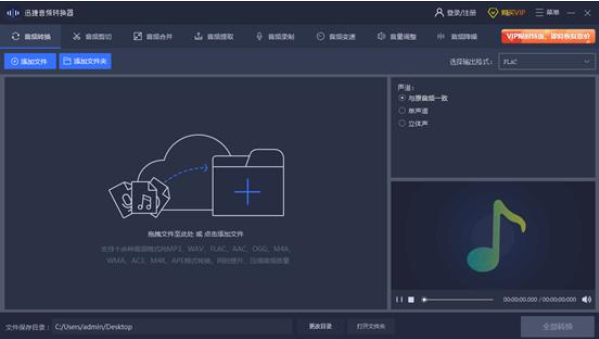

2172 比如我很喜歡某個(gè)視頻的音樂,想單獨(dú)保存為mp3或其他的音頻格式并放到本地電腦上,就會(huì)用到超級(jí)轉(zhuǎn)換秀。這種情況,還適用于把那些加密的視頻轉(zhuǎn)換為mp3~比如下載的qsv、qlv、kux格式的加密視頻。

2019-06-14 15:55:42 3266

3266 當(dāng)涉及到加密項(xiàng)目的去中心化時(shí),似乎會(huì)有不同的舒適度。

2020-02-06 14:06:54 712

712 MP3的音頻格式在我們的日常生活中會(huì)經(jīng)常用到,那如何把其他格式的音頻文件批量轉(zhuǎn)為MP3?下面小麗將通過使用音頻轉(zhuǎn)換的功能,向大家介紹一款實(shí)用的迅捷音頻轉(zhuǎn)換器軟件。

2020-06-27 14:49:00 4781

4781

1、 關(guān)于如何在VHDL模塊調(diào)用一個(gè)Verilog模塊 在VHDL模塊聲明一個(gè)要與調(diào)用的Verilog模塊相同名稱的元件(component),元件的名稱和端口模式應(yīng)與Verilog模塊的名稱和輸入

2021-04-30 14:06:04 11930

11930

程序一但封裝好之后,方便以后調(diào)用 如果項(xiàng)目中有更多的伺服軸,那么把數(shù)組加長,然后多調(diào)用幾次就可以了。

2021-07-05 14:57:12 4453

4453

先給大佬們交代一下這個(gè)項(xiàng)目中我了解的關(guān)于spi的內(nèi)容、本人碰到的問題的起因經(jīng)過以及現(xiàn)在卡住的問題: 這個(gè)項(xiàng)目中用到了一個(gè)單片機(jī)和一個(gè)cpu,單片機(jī)用來檢測按鍵、用串口通信接收幾個(gè)傳感器數(shù)據(jù)

2021-12-22 19:37:02 10

10 在本文中,我們將向您展示如何簡單地將 SD 卡模塊與 PIC 微控制器連接并在其中存儲(chǔ)數(shù)據(jù)。

2022-08-03 16:47:21 2195

2195

電子發(fā)燒友網(wǎng)站提供《Quantum項(xiàng)目中替換樹莓派.zip》資料免費(fèi)下載

2022-10-28 09:43:04 2

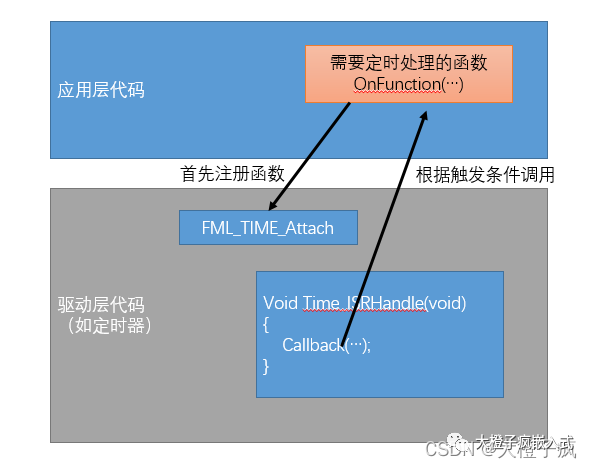

2 函數(shù)調(diào)用很好理解,即使剛學(xué)沒多久的朋友也知道函數(shù)調(diào)用是怎么實(shí)現(xiàn)的,即調(diào)用一個(gè)已經(jīng)封裝好的函數(shù),實(shí)現(xiàn)某個(gè)特定的功能。 把一個(gè)或者多個(gè)功能通過函數(shù)的方式封裝起來,對(duì)外只提供一個(gè)簡單的函數(shù)接口,然后在其他地方調(diào)用即可

2023-02-15 14:48:03 1645

1645

在工程項(xiàng)目中,不管是小到模塊級(jí)驗(yàn)證,還是大到系統(tǒng)級(jí)驗(yàn)證,都有一項(xiàng)不可缺少的feature,那就是中斷。

2023-04-11 09:52:13 1501

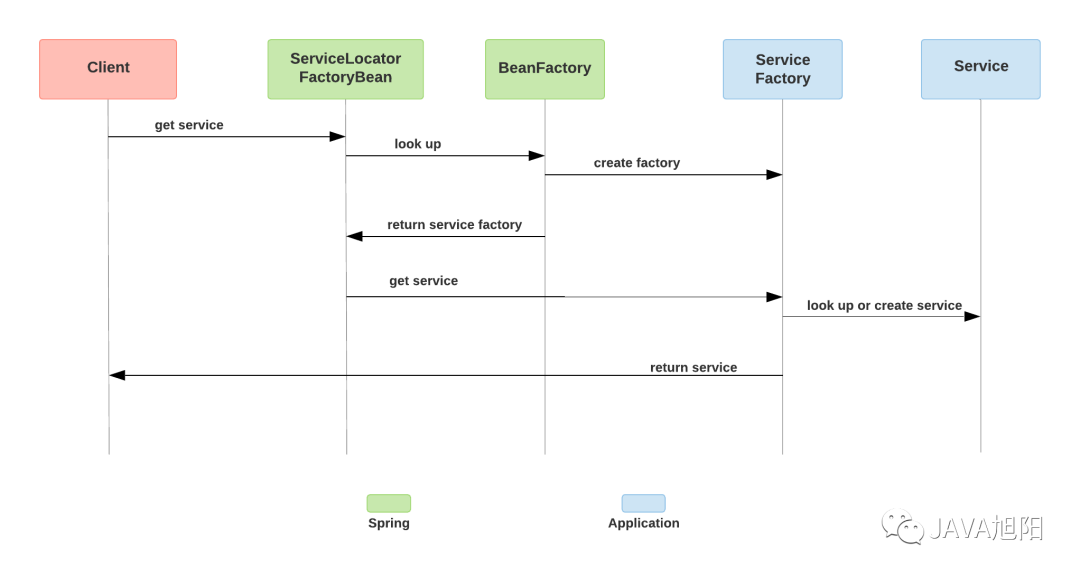

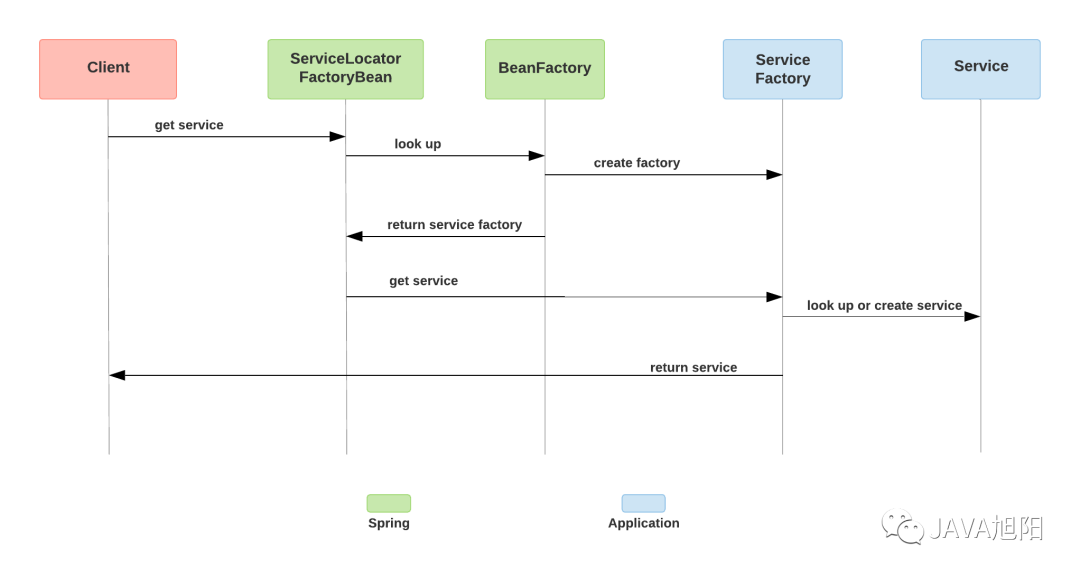

1501 不知道大家在項(xiàng)目中有沒有遇到過這樣的場景,根據(jù)傳入的類型,調(diào)用接口不同的實(shí)現(xiàn)類或者說服務(wù),比如根據(jù)文件的類型使用 CSV解析器或者JSON解析器,在調(diào)用的客戶端一般都是用`if else`去做判斷

2023-05-11 10:39:24 887

887

電子發(fā)燒友網(wǎng)站提供《如何輕松的將電源集成到項(xiàng)目中.zip》資料免費(fèi)下載

2023-07-12 10:00:58 0

0 大家應(yīng)該都經(jīng)常聽到光模塊加密或者寫碼的說法,特別是一些大廠的網(wǎng)絡(luò)設(shè)備,都要求用自己原裝模塊,否則就會(huì)怎樣怎樣的,那么到底什么是寫碼加密?各個(gè)第三方模塊廠商,又是如何應(yīng)對(duì)設(shè)備廠商寫碼加密的?是否可以破解?破解不了會(huì)怎么樣?

2023-08-09 09:44:20 3733

3733

(1)PLC可以用于控制綠化項(xiàng)目中的灌溉系統(tǒng)。通過傳感器監(jiān)測土壤濕度、氣象條件等參數(shù),PLC可以自動(dòng)調(diào)節(jié)灌溉設(shè)備的運(yùn)行,確保植物得到適量的水分,提高灌溉效率和節(jié)約水資源。 (2)PLC可以用于控制

2023-08-14 08:35:02 903

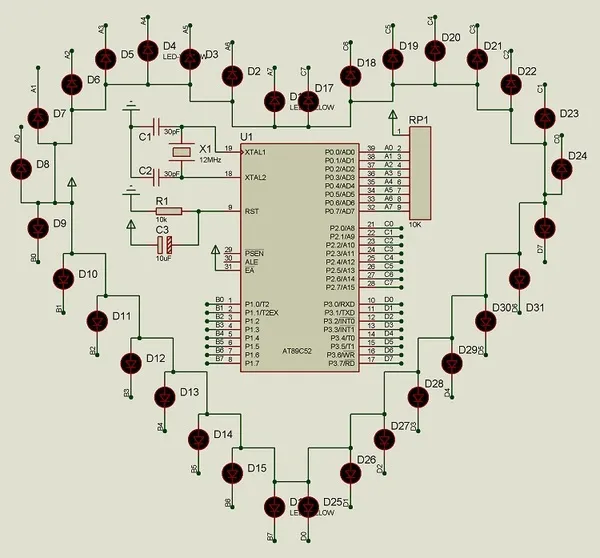

903 單片機(jī)項(xiàng)目中LED的重要性

2023-09-18 16:19:14 1503

1503

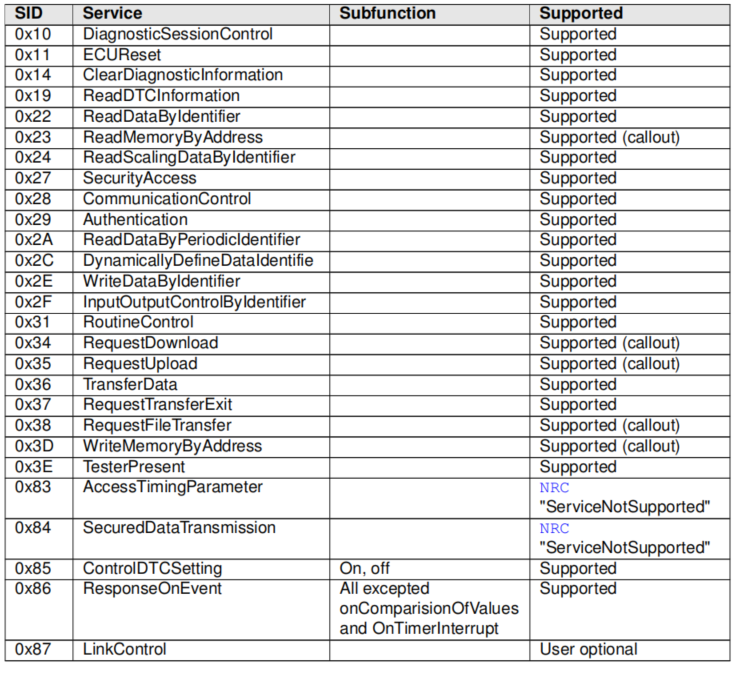

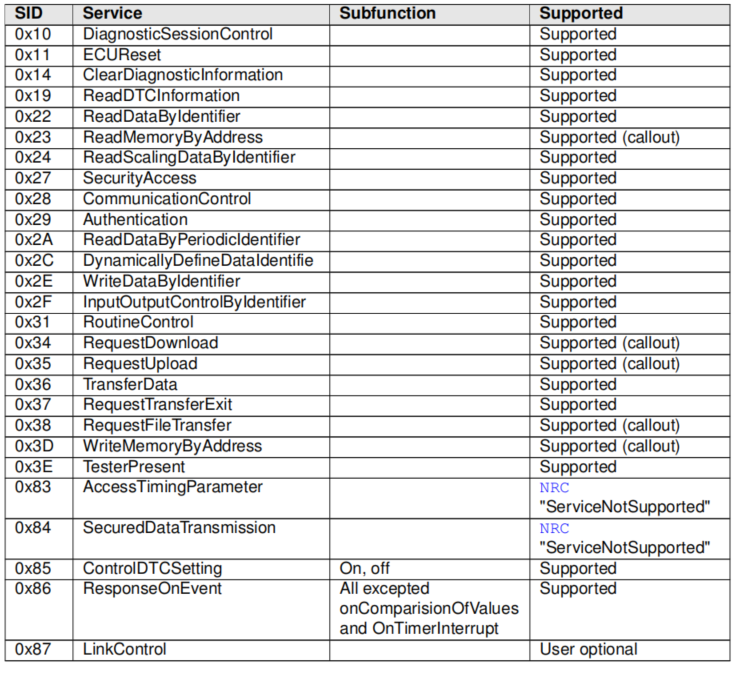

DSP概述 當(dāng)接收到來自DSD子模塊的調(diào)用請求時(shí),DSP總是執(zhí)行以下基本的處理步驟: ● 分析接收到的診斷請求消息 ● 檢查格式以及是否支持?jǐn)y帶的子功能 ● 在DEM、SW-Cs或其他BSW模塊上

2023-10-04 11:35:00 2364

2364

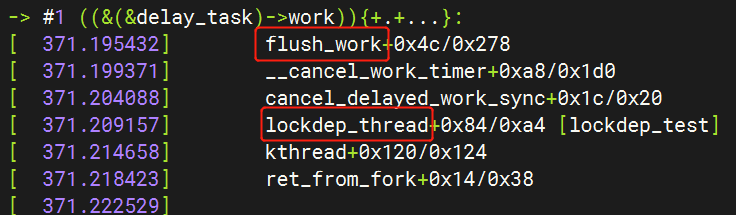

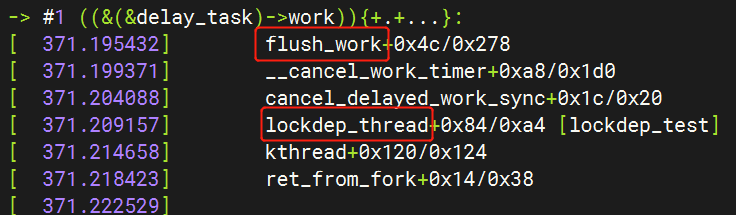

實(shí)際項(xiàng)目中的死鎖 下面的例子要復(fù)雜一些,這是從實(shí)際項(xiàng)目中抽取出來的死鎖,更具有代表性。 # include # include # include # include # include

2023-09-27 15:24:13 1531

1531

做任何模塊前,要確定輸入輸出端口有哪些,有一個(gè)整體的概念;方便以后模塊調(diào)用;

2023-10-10 14:10:56 1457

1457

PLC在許多新能源項(xiàng)目中都可以應(yīng)用。以下是一些常見的新能源項(xiàng)目,可以利用PLC實(shí)現(xiàn)自動(dòng)化控制和監(jiān)測。

2023-12-28 18:18:39 2805

2805 。 1.2 為什么要調(diào)用其他模塊? 在復(fù)雜的設(shè)計(jì)中,我們通常需要實(shí)現(xiàn)各種不同的功能,并且這些功能往往可以通過不同的模塊來實(shí)現(xiàn)。通過調(diào)用其他模塊,我們可以將問題分解為更小的子問題,并且可以更方便地實(shí)現(xiàn)和維護(hù)我們的設(shè)計(jì)。 1.3 調(diào)用模塊的基本語法

2024-02-22 15:56:25 8556

8556 與微軟Azure相似,中國企業(yè)可以借助AWS全球Bedrock服務(wù),調(diào)用部署在其他區(qū)域的Claude 3模型進(jìn)行運(yùn)算。另外,自模型發(fā)布以來,已收到廣泛的中企合作請求。

2024-04-03 10:14:08 1545

1545 函數(shù)的處理結(jié)果包含兩個(gè)數(shù)據(jù),如何把兩個(gè)數(shù)據(jù)返回給調(diào)用函數(shù)? 第一種,把兩個(gè)數(shù)據(jù)封裝成一個(gè)結(jié)構(gòu)體,函數(shù)返回結(jié)構(gòu)體。 調(diào)用函數(shù)的地方同樣用結(jié)構(gòu)體去接收函數(shù)的返回值。 第二種,把返回值保存在形參中。 既然

2025-01-08 10:15:45 745

745

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論