1、關(guān)于如何在VHDL模塊調(diào)用一個(gè)Verilog模塊

在VHDL模塊聲明一個(gè)要與調(diào)用的Verilog模塊相同名稱(chēng)的元件(component),元件的名稱(chēng)和端口模式應(yīng)與Verilog模塊的名稱(chēng)和輸入/輸出模式相同。注意Verilog區(qū)分大小寫(xiě),VHDL不區(qū)分,所以模塊名字一定要完全一致,不能搞混。

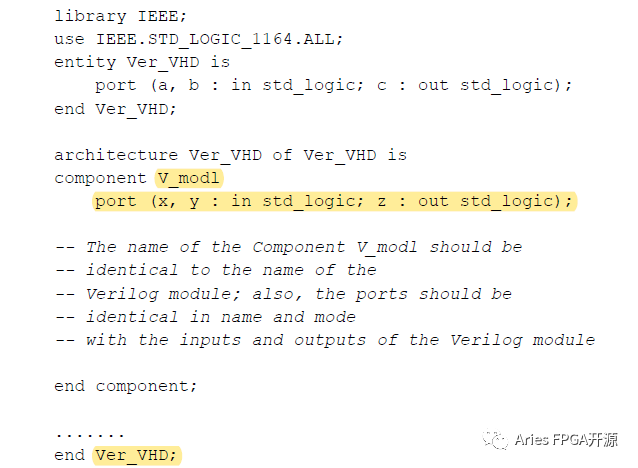

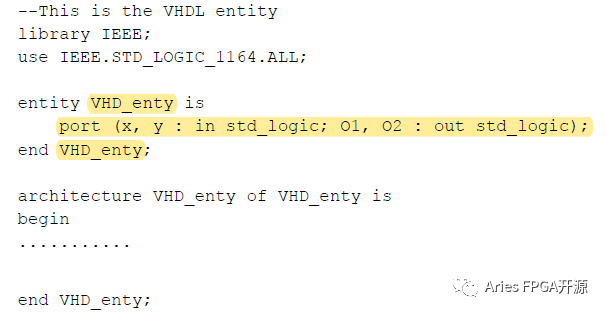

舉個(gè)例子:下面是一個(gè)VHDL模塊,在里面聲明了一個(gè)元件(component)

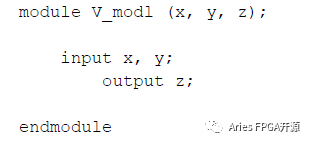

看Verilog模塊再

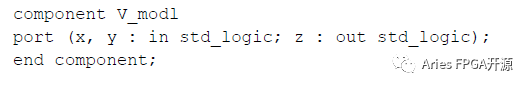

VHDL的模塊就是通過(guò)聲明一個(gè)元件(component)來(lái)調(diào)用這個(gè)Verilog模塊,將元件聲明提出來(lái)講,如下圖:

對(duì)比這個(gè)Verilog模塊和VHDL中聲明的元件不難發(fā)現(xiàn),模塊名/端口/輸入輸出模式完全一樣,這和VHDL自己調(diào)用用VHDL的元件(component)基本一樣。

2、關(guān)于如何在Verilog中調(diào)用VHDL模塊

在Verilog中,通過(guò)在Verilog模塊中輸入其名稱(chēng)(標(biāo)識(shí)符)及端口來(lái)調(diào)用VHDL實(shí)體。模塊的參數(shù)應(yīng)該與實(shí)體的類(lèi)型和端口的方向匹配,可以映射到Verilog模塊的VHDL端口為:in,out和inout;在某些模擬器中,不允許使用緩沖區(qū)。Verilog模塊只能使整個(gè)VHDL實(shí)體可見(jiàn)。

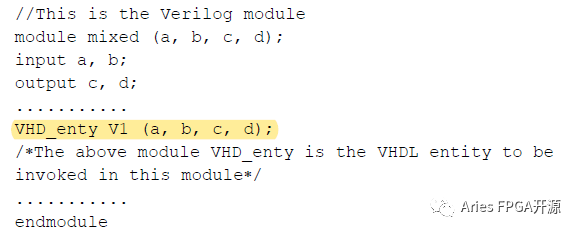

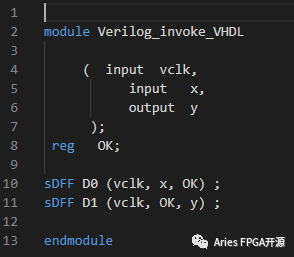

舉個(gè)例子:下圖是一個(gè)Verilog模塊調(diào)用了VHDL模塊(高亮處)

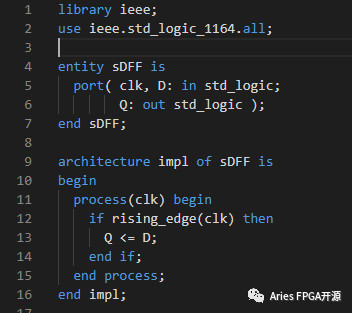

下圖是一個(gè)VHDL模塊

Simulator(模擬器,注:這個(gè)是英文原版使用的詞語(yǔ),我的理解就是一些EDA)首先在Verilog模塊中查找,以查看是否有任何名為VHD_enty的Verilog模塊。如果找不到,模擬器將在VHDL實(shí)體中查找。當(dāng)模擬器找到名稱(chēng)為VHD_enty的實(shí)體時(shí),它將該實(shí)體綁定到Verilog模塊。在代碼中,輸入a被傳遞到輸入端口x;輸入b傳遞給輸入y。VHDL實(shí)體計(jì)算輸出O1和O2;這兩個(gè)輸出分別傳遞到Verilog輸出c和d。調(diào)用VHDL模塊與調(diào)用功能或任務(wù)非常相似。

例子舉完了,下面驗(yàn)證一下

驗(yàn)證:在Verilog中調(diào)用VHDL模塊實(shí)體(VHDL調(diào)用Verilog考慮到比較簡(jiǎn)單,大家用的更多是Verilog,就不舉例子了)

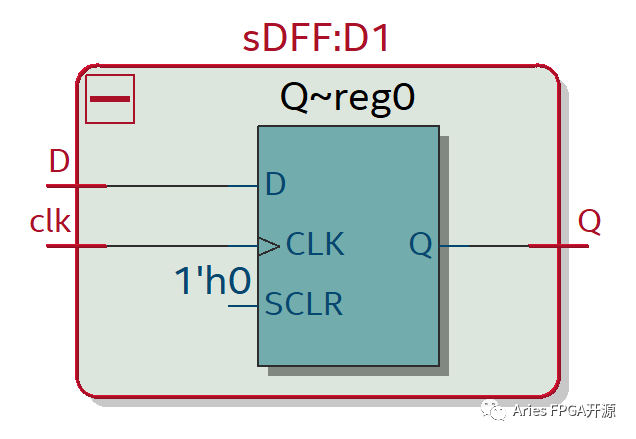

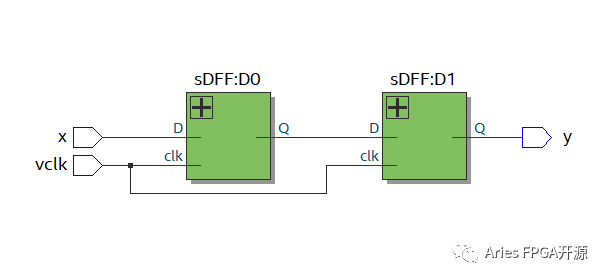

驗(yàn)證內(nèi)容:使用Verilog調(diào)用兩個(gè)VHDL寫(xiě)的D觸發(fā)器模塊實(shí)現(xiàn)打兩拍。

這個(gè)代碼是一個(gè)用VHDL語(yǔ)言寫(xiě)的D觸發(fā)器模塊,在FIFO中也寫(xiě)過(guò)。

這個(gè)代碼是Verilog寫(xiě)的,在內(nèi)部調(diào)用兩個(gè)由VHDL寫(xiě)的D觸發(fā)器,實(shí)現(xiàn)兩級(jí)D觸發(fā)器。

上圖是VHDL寫(xiě)的D觸發(fā)器綜合出的原理圖,注意對(duì)應(yīng)的端口。

上圖是Verilog代碼綜合出來(lái)的原理圖,從代碼上看,定義了vclk、x、y三個(gè)端口,連接VHDL寫(xiě)的兩個(gè)D觸發(fā)器,基本的調(diào)用過(guò)程就是這樣。

總結(jié):兩者的互相調(diào)用過(guò)程都不復(fù)雜,舉個(gè)基礎(chǔ)的例子只是為了大家熟悉這個(gè)過(guò)程。在實(shí)際中難免會(huì)遇到有互相調(diào)用的地方。

編輯:jq

-

FPGA

+關(guān)注

關(guān)注

1662文章

22483瀏覽量

638554 -

vhdl

+關(guān)注

關(guān)注

30文章

822瀏覽量

131836 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2065瀏覽量

63515

原文標(biāo)題:關(guān)于VHDL和Verilog模塊互相調(diào)用的問(wèn)題

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Verilog HDL語(yǔ)法學(xué)習(xí)筆記

高層次綜合在FPGA設(shè)計(jì)中的價(jià)值與局限

使用Vivado ILA進(jìn)行復(fù)雜時(shí)序分析的完整流程

基于FPGA VHDL的FSK調(diào)制與解調(diào)設(shè)計(jì)

FPGA 入門(mén)必看:Verilog 與 VHDL 編程基礎(chǔ)解析!

Jumia API 調(diào)用:覆蓋非洲市場(chǎng)的實(shí)操指南

請(qǐng)問(wèn)verilog文件開(kāi)頭部分的@00080000是什么意思?

使用NucleiStudio生成tb仿真需要的.verilog文件

Python調(diào)用API教程

如何利用Verilog HDL在FPGA上實(shí)現(xiàn)SRAM的讀寫(xiě)測(cè)試

DSP芯片與800G光模塊的核心關(guān)系:Transmit Retimed DSP、LPO與LRO方案的探討

圖解環(huán)路設(shè)計(jì)及控制技術(shù)探討

為什么我選擇VHDL入門(mén)

verilog模塊的調(diào)用、任務(wù)和函數(shù)

在Vivado調(diào)用MIG產(chǎn)生DDR3的問(wèn)題解析

探討VHDL和Verilog模塊互相調(diào)用的問(wèn)題

探討VHDL和Verilog模塊互相調(diào)用的問(wèn)題

評(píng)論