聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

仿真器

+關注

關注

14文章

1051瀏覽量

87261 -

RTL

+關注

關注

1文章

394瀏覽量

62647 -

全加器

+關注

關注

10文章

62瀏覽量

29112 -

半加器

+關注

關注

1文章

29瀏覽量

9127

發布評論請先 登錄

相關推薦

熱點推薦

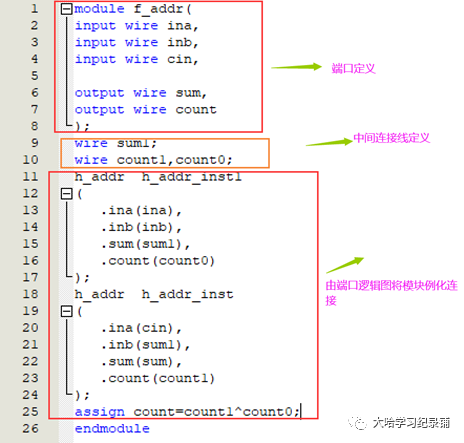

FPGA入門——1位全加器設計 精選資料分享

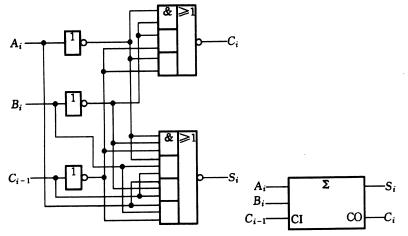

FPGA入門——1位全加器設計一、原理圖輸入1.1 創建工程1.2 原理圖輸入1.3 將設計項目設置成可調用的元件1.4 半加器仿真1.5 設計全加器頂層文件二、Verilog編程En

發表于 07-26 07:01

基于Quartus II軟件完成一個1位全加器的設計

FPGA 設計入門(嵌入式系統應用開發)一、實驗要求二、實驗步驟1. 新建工程2. 原理圖設計3. 將設計項目設置成可調用的元件4. 半加器仿真5. 設計全加器頂層文件6. 將設計項目

發表于 12-17 06:19

什么是8位全加器和8為帶超前進位的全加器?

超前進位的8位全加器:總結前言隨著人工智能的不斷發展,機器學習這門技術也越來越重要,很多人都開啟了學習機器學習,本文就介紹了機器學習的基礎內容。以下是本篇文章正文內容,使用門級原語語句設計8位全加器和8為帶超前進位的全加器,并寫

發表于 02-09 07:49

全加器是什么?全加器和半加器的區別?

加器是能夠計算低位進位的二進制加法電路。與半加器相比,全加器不只考慮本位計算結果是否有進位,也考慮上一位對本位的進位,可以把多個一位全加器級聯后做成多位全加器。

發表于 07-25 11:15

?7.7w次閱讀

全加器的真值表

全加器英語名稱為full-adder,是用門電路實現兩個二進制數相加并求出和的組合線路,稱為一位全加器。一位全加器可以處理低位進位,并輸出本位加法進位,多個一位全加器進行級聯可以得到多

Verilog數字系統設計——復雜組合邏輯實驗2(8位全加器和8為帶超前進位的全加器)

Verilog數字系統設計四復雜組合邏輯實驗2文章目錄Verilog數字系統設計四前言一、什么是8位全加器和8為帶超前進位的全加器?二、編程1.要求:2.門級原語實現8位

發表于 12-05 19:06

?4次下載

仿真測試2:全加器(模塊調用)

仿真測試2:全加器(模塊調用)

評論