Altera宣布業(yè)界首款支持FPGA的OpenCL工具,進(jìn)一步加速了FPGA在異構(gòu)系統(tǒng)中的應(yīng)用;OpenCL軟件開發(fā)套件支持開發(fā)人員充分發(fā)揮FPGA的性能和效能優(yōu)勢(shì)。

2012-11-06 14:26:05 1861

1861 Altera的SoC FPGA已經(jīng)發(fā)售,將如何繼續(xù)追趕并超越賽靈思呢?Altera的SoC開發(fā)調(diào)試工具有什么不同呢?ARM+FPGA的未來如何?詳見本文分析。

2013-01-05 10:13:47 3670

3670 發(fā)布的ARM? Development Studio 5 (DS-5?) Altera?版工具包軟件,這是業(yè)界唯一的FPGA自適應(yīng)調(diào)試軟件,支持設(shè)計(jì)人員同時(shí)查看器件的處理器和FPGA部分。

2013-04-23 10:40:55 2735

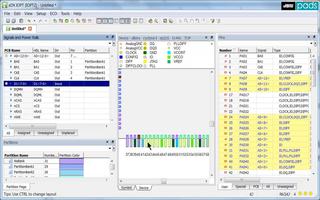

2735 InTime。 前言 高層次的設(shè)計(jì)可以讓設(shè)計(jì)以更簡(jiǎn)潔的方法捕捉,從而讓錯(cuò)誤更少,調(diào)試更輕松。然而,這種方法最受詬病的是對(duì)性能的犧牲。在復(fù)雜的 FPGA 設(shè)計(jì)上實(shí)現(xiàn)高性能,往往需要手動(dòng)優(yōu)化 RTL 代碼,這也意味著從 C 轉(zhuǎn)化得到 RTL 基本不可能。其實(shí),使用 FPGA 工具設(shè)置來優(yōu)化設(shè)計(jì)可以最

2020-12-20 11:46:46 2389

2389

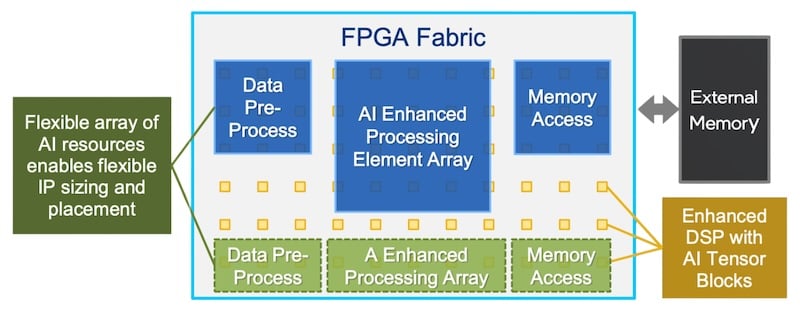

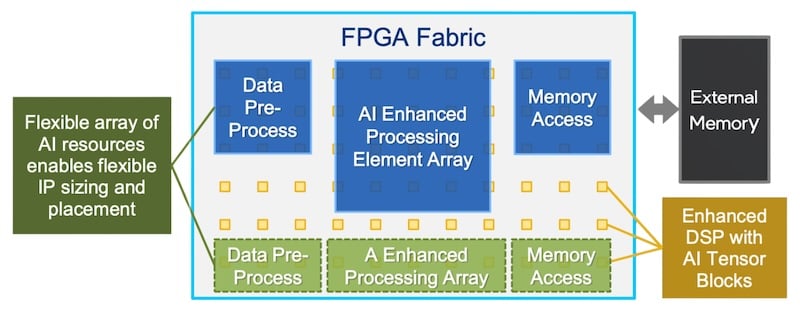

SoC FPGA Quartus Prime設(shè)計(jì)軟件更新 FPGA生命周期支持擴(kuò)展 全新Agilex 5 SoC FPGA 隨著中檔Agilex 5的發(fā)布,Altera聲稱這是第一個(gè)在

2024-05-07 15:03:26 9515

9515

SOC是不是就是ARM+FPGA?未來要做一個(gè)FPGA的電機(jī)控制器,看了一下ALTERA的網(wǎng)站看的有點(diǎn)暈懇請(qǐng)各位前輩能給一些參考設(shè)計(jì)。

2017-02-14 10:09:04

我經(jīng)過一年多的實(shí)踐總結(jié)出Altera SOC FPGA起動(dòng)步驟,對(duì)大家在以后實(shí)踐中會(huì)有幫助。 第1步:起動(dòng)固化在內(nèi)部的廠家ROM程序,根據(jù)起動(dòng)引腳的配置,選擇從哪里起動(dòng)(QSPI,SD,NAND

2016-02-04 00:05:19

供電時(shí)所需的所有電源軌設(shè)計(jì)已經(jīng)過優(yōu)化,可支持 5V 輸入極高密度的 PCB 設(shè)計(jì)可節(jié)省電路板面積開關(guān)穩(wěn)壓器和 LDO 的最優(yōu)組合可提供最佳的電源分配樹支持 DDR3 存儲(chǔ)器件該設(shè)計(jì)已經(jīng)過測(cè)試,可用于為 Arria V FPGA 加電

2018-09-12 09:08:24

分立式 IC,由單個(gè) 5V 輸入供電。主要特色提供為 Altera? Arria? V GX FPGA 供電時(shí)所需的所有電源軌設(shè)計(jì)已經(jīng)過優(yōu)化,可支持 5V 輸入板載電源定序低成本分立式解決方案小尺寸

2018-12-04 11:33:24

`描述此參考設(shè)計(jì)提供為 Altera Cyclone V SoC FPGA 供電時(shí)所需的所有電源軌。此設(shè)計(jì)使用 LMZ3 系列模塊產(chǎn)生用于為 FPGA 供電的電源軌。`

2015-05-11 16:49:30

供電時(shí)所需的所有電源軌。此設(shè)計(jì)還顯示了正確的加電順序。特性 提供為 Altera Cyclone V SoC 供電時(shí)所需的所有電源軌設(shè)計(jì)已經(jīng)過優(yōu)化,可支持 12V 輸入集成 LMZ3 系列電源模塊,簡(jiǎn)便

2022-09-26 07:58:34

時(shí)所需的所有電源軌。此設(shè)計(jì)還顯示了正確的加電順序。主要特色提供為 Altera Cyclone V SoC 供電時(shí)所需的所有電源軌設(shè)計(jì)已經(jīng)過優(yōu)化,可支持 12V 輸入集成 LMZ3 系列電源模塊,簡(jiǎn)便

2018-09-06 09:07:37

時(shí)所需的所有電源軌。此設(shè)計(jì)還顯示了正確的加電順序。特性提供為 Altera Cyclone V SoC 供電時(shí)所需的所有電源軌設(shè)計(jì)已經(jīng)過優(yōu)化,可支持 12V 輸入集成 LMZ3 系列電源模塊,簡(jiǎn)便易用

2015-05-11 16:45:44

存儲(chǔ)器工具包,可幫助您測(cè)試FPGA設(shè)備中IP的實(shí)現(xiàn)。

有關(guān)Altera支持的最大速度,請(qǐng)參閱外部存儲(chǔ)器接口規(guī)格估計(jì)器頁(yè)面FPGA。

2023-09-26 07:38:12

影響,Altera也不例外。Altera在28nm制程節(jié)點(diǎn)上開發(fā)FPGA新系列產(chǎn)品,以及支持軟件的成本,要遠(yuǎn)遠(yuǎn)高于65nm開發(fā)時(shí)所投入的2.5億美元。只有很少的終全文下載

2010-04-22 11:30:41

有任何其他的優(yōu)化編譯流程的竅門,請(qǐng)與我們分享。讓我們一起建設(shè)更加美好的 FPGA 用戶社區(qū)!了解更多 InTime 的信息,或者直接申請(qǐng)免費(fèi)試用。關(guān)注Plunify公眾號(hào),關(guān)注FPGA設(shè)計(jì)優(yōu)化。所有產(chǎn)品的信息和相關(guān)使用申請(qǐng)亦在公眾號(hào)主頁(yè)的菜單中,我們期待與您的交流。?

2018-06-11 16:11:07

上一篇系列文章“INtime可與Windows在同個(gè)PC運(yùn)行的實(shí)時(shí)操作系統(tǒng)(上)”中我們介紹INtime實(shí)時(shí)操作系統(tǒng)的基本特性與功能。本篇文章將著重介紹INtime RTOS內(nèi)部的關(guān)鍵處理機(jī)制及其

2021-07-02 06:41:14

InTime 利用大數(shù)據(jù)分析和人工智能,建立時(shí)序數(shù)據(jù)庫(kù),無需修改源代碼即可優(yōu)化設(shè)計(jì),為工程師推薦最佳工具參數(shù)組合。了解更多>>

2017-04-18 14:53:40

發(fā)現(xiàn)Altera官網(wǎng)上一個(gè)不錯(cuò)的視頻,講SoC FPGA嵌入式軟件的,都是干貨分享啊!系列視頻一共有5個(gè)視頻,視頻上傳了幾遍都上傳不了,大家還是去他們網(wǎng)站看吧:http://www.alteraforum.com.cn/showtopic-6634.aspx

2019-09-25 09:01:49

Altera公司意欲通過更先進(jìn)的制程工藝和更緊密的產(chǎn)業(yè)合作,正逐步強(qiáng)化FPGA協(xié)同處理器,大幅提升SoC FPGA的整體性能,為搶攻嵌入式系統(tǒng)市場(chǎng)版圖創(chuàng)造更大的差異化優(yōu)勢(shì)。隨著SoC FPGA在

2019-08-26 07:15:50

引言 隨著技術(shù)的進(jìn)一步發(fā)展,SoC設(shè)計(jì)面臨著一些諸如如何進(jìn)行軟硬件協(xié)同設(shè)計(jì),如何縮短電子產(chǎn)品開發(fā)周期的難題。為了解決SoC設(shè)計(jì)中遇到的難題,設(shè)計(jì)方法必須進(jìn)一步優(yōu)化。因此,人們提出了基于FPGA

2019-07-12 07:25:22

。

優(yōu)化時(shí)序

下一步是使用名為InTime 的設(shè)計(jì)探索工具(https://www.plunify.com/en/free-evaluation/)。(同樣,可以自己編寫腳本來嘗試

2024-08-16 19:56:07

Qt配置Altera SoC FPGA Kit 編譯器: GCC(Altera SoC) /home/terasic

2018-07-03 08:41:02

` 對(duì)于CPLD、FPGA和SoC設(shè)計(jì),Altera Quartus? II軟件在性能和效能上是業(yè)界首屈一指的軟件。 Quartus II軟件v13.1支持您在一天內(nèi)完成更多的設(shè)計(jì)迭代,提供工具幫助

2013-11-13 15:34:26

本帖最后由 峩、那么可笑 于 2014-12-11 16:22 編輯

[Altera]選取合適的SoC FPGA專業(yè)指南(中英版)更多精彩內(nèi)容:http://www.3532n.com/soft/5/2 ... 530.html?1418285557

2014-12-11 16:21:21

,未優(yōu)化前功耗1.718,優(yōu)化后為1.726,咨詢了Intime技術(shù)支持,他說Intime主要是對(duì)時(shí)序的優(yōu)化效果要更明顯,于是,我將設(shè)計(jì)的工作頻率提高,時(shí)序不滿足,再使用Intime進(jìn)行Speed

2017-06-30 15:28:28

設(shè)計(jì)的云平臺(tái)。用戶能透過這個(gè)平臺(tái),以隨選式快速地得到服務(wù)器資源和軟件工具。Plunify在2013年正式發(fā)布旗艦產(chǎn)品 – InTime。InTime是一款針對(duì)FPGA綜合與布局布線問題的專家軟件。它

2017-07-05 11:00:48

\include\soc_cv_av2、指定硬件平臺(tái)修改D:\intelFPGA\17.1\embedded\ip\altera\hps\altera_hps\hwlib\include下的hwlib.h文件,在第

2020-02-16 18:38:28

,FPGA就是“可反復(fù)編程的邏輯器件”。如圖1.1所示,這是一顆Altera公司的CycloneV Soc FPGA器件,從外觀上看,貌似和一般的CPU芯片沒有太大差別。圖1.1 Altera公司

2017-09-19 21:52:57

FPGA,特別是Zynq系列或Altera等效SOC + FPGA,設(shè)計(jì)PCB板,批量生產(chǎn)產(chǎn)品并通過嚴(yán)格的EMI資格認(rèn)證。在什么階段,公司可能需要將Xilinx稱為Altera技術(shù)支持?可能需要

2019-04-15 10:08:36

是Tensorflow。這似乎有些難以置信,畢竟我們已經(jīng)開發(fā)了賽靈思Vivado的插件Plunify Cloud以及設(shè)計(jì)優(yōu)化軟件InTime (微信公眾號(hào):Plunify_FPGA)難道不應(yīng)該選擇一個(gè)可以

2017-12-11 15:54:58

。Plunify 的 CEO 黃瀚華說:“盡管從硬件工程師的角度來說,應(yīng)該盡可能多地使用 DSP。但使用限制 DSP 數(shù)量的設(shè)置其實(shí)可以顯著提升結(jié)果。”基于這個(gè)算法,Plunify 推出了優(yōu)化軟件

2018-06-26 15:19:23

Hi,以前在學(xué)校的時(shí)候就經(jīng)常遇見時(shí)序收斂的問題,尤其是改RTL好麻煩啊。工作以后和朋友們一起做了個(gè)時(shí)序優(yōu)化的軟件,叫InTime,希望可以幫助有相同問題的朋友。^_^我們搞了免費(fèi)試用的活動(dòng),有興趣

2017-05-11 10:55:17

亞馬遜云端上進(jìn)行編譯,測(cè)試甚至優(yōu)化FPGA項(xiàng)目或DCP。PlunifyCloud 讓用戶可以輕易地使用可延展地計(jì)算資源,目前只支持亞馬遜云服務(wù),因?yàn)?b class="flag-6" style="color: red">軟件的許可證也是亞馬遜提供的(和使用F1實(shí)例一樣

2017-11-22 10:51:18

10 SoC (片內(nèi)系統(tǒng)) 開發(fā)板。這些開發(fā)板由 Altera 進(jìn)行了測(cè)試和驗(yàn)證,并舉例說明了布局、信號(hào)完整性和電源管理方面的最佳設(shè)計(jì)方法。圖 1:Arria 10 GX FPGA 開發(fā)套件板圖 2

2018-10-29 17:01:56

本系列教程的宗旨是在力求全面介紹Altera及其QuartusII軟件原理的基礎(chǔ)上,對(duì)何如使用Altera FPGA進(jìn)行基礎(chǔ)設(shè)計(jì)、時(shí)序分析、驗(yàn)證、優(yōu)化四大方面進(jìn)行講解通向FPGA之路---七天玩轉(zhuǎn)

2012-12-04 14:36:51

《Altera FPGA/CPLD設(shè)計(jì)(高級(jí)篇)》結(jié)合作者多年工作經(jīng)驗(yàn),深入地討論了Altera FPGA/CPLD的設(shè)計(jì)、優(yōu)化技巧。在討論FPGA/CPLD設(shè)計(jì)指導(dǎo)原則的基礎(chǔ)上,介紹了Altera器件的高級(jí)應(yīng)用;引領(lǐng)讀者

2009-02-12 09:19:12 4807

4807 altera fpga/cpld設(shè)計(jì) 基礎(chǔ)篇結(jié)合作者多年工作經(jīng)驗(yàn),系統(tǒng)地介紹了FPGA/CPLD的基本設(shè)計(jì)方法。在介紹FPGA/CPLD概念的基礎(chǔ)上,介紹了Altera主流FPGA/CPLD的結(jié)構(gòu)與特點(diǎn),并通過豐富的實(shí)例講解

2009-07-10 17:35:45 58

58 Altera FPGA開發(fā)軟件安裝指南

2009-07-21 17:19:14 0

0 基于FPGA的可層疊組合式SoC原型系統(tǒng)設(shè)計(jì)

在復(fù)雜片上系統(tǒng)SoC的設(shè)計(jì)過程中,驗(yàn)證仿真是影響項(xiàng)目進(jìn)度的關(guān)鍵因素。隨著芯片生產(chǎn)和制造工藝的提高,SoC設(shè)計(jì)的規(guī)模、復(fù)雜

2010-01-08 11:18:42 1204

1204

Altera公司(Nasdaq: ALTR)今天宣布可以提供FPGA業(yè)界的第一個(gè)虛擬目標(biāo)平臺(tái),支持面向Altera最新發(fā)布的SoC FPGA器件立即開始器件專用嵌入式軟件的開發(fā)。在Synopsys有限公司成熟的虛擬原型開發(fā)解

2011-10-13 09:15:28 938

938 Altera公司(NASDAQ: ALTR)今天發(fā)布FPGA和SoC FPGA的開放計(jì)算語言(OpenCL?)標(biāo)準(zhǔn)開發(fā)計(jì)劃。OpenCL標(biāo)準(zhǔn)是基于C語言的開放標(biāo)準(zhǔn),適用于并行編程。Altera的OpenCL計(jì)劃結(jié)合了FPGA的并行能力以及OpenCL標(biāo)準(zhǔn)

2011-11-16 16:12:08 1035

1035 本資料是關(guān)于Altera FPGA的選型及開發(fā),內(nèi)容大綱是:Altera的 FPGA體系結(jié)構(gòu)簡(jiǎn)介;Altera的 FPGA選型策略;嵌入式邏輯分析工具SignalTAPII的使用;基于CPLD的FPGA配制方法。

2012-08-15 14:48:34 104

104 Altera公司SoC FPGA產(chǎn)品簡(jiǎn)介高級(jí)信息摘要(英文資料) 圖 硬件處理系統(tǒng)

2012-09-05 13:57:38 28

28 本文是關(guān)于Altera公司SoC FPGA 的用戶手冊(cè)(英文版) 。文中主要介紹了什么是SoC FPGA、SoC FPGA相關(guān)知識(shí)介紹、為什么要使用SoC FPGA以及SoC FPGA都應(yīng)用到哪些方面。

2012-09-05 14:03:08 153

153 電子發(fā)燒友網(wǎng)訊:Altera公司2012年11月28號(hào)宣布,Altera Cyclone V FPGA 和Altera SoC FPGA虛擬目標(biāo)開發(fā)工具獲得EDN中國(guó) 《可編程器件》 和 《開發(fā)工具與軟件應(yīng)用設(shè)計(jì)》 類的2012最佳產(chǎn)品獎(jiǎng)。ED

2012-11-29 16:59:37 1635

1635 電子發(fā)燒友網(wǎng)訊:2012年12月13號(hào),北京——Altera公司今天宣布,首次正式發(fā)售其28 nm SoC器件。通過寬帶互聯(lián)干線鏈接,Altera SoC FPGA緊密集成了雙核ARM? Cortex?-A9 MPCore?處理器、存儲(chǔ)器控

2012-12-13 10:33:17 2470

2470 近日,芯片設(shè)計(jì)先驅(qū)廠商Plunify與合作伙伴推出創(chuàng)新云計(jì)算平臺(tái),整合亞馬遜云計(jì)算能力、Altera和賽靈思FPGA、EDA軟件平臺(tái),可為中小型企業(yè)按需設(shè)計(jì)、并行自動(dòng)化分析,大大縮短設(shè)計(jì)時(shí)間。

2013-03-08 10:42:21 1441

1441 Altera公司 (NASDAQ: ALTR)今天宣布推出Quartus? II軟件13.0版,這一軟件實(shí)現(xiàn)了性能最好的FPGA和SoC,提高了設(shè)計(jì)人員的效能。28 nm FPGA和SoC用戶的編譯

2013-05-07 14:30:30 4183

4183 Altera于6月11日在北京宣布,全球同步推出10代FPGA和SoC。先行發(fā)布的包括高端Stratix10和中端Arria10系列。目標(biāo)是替代傳統(tǒng)的ASSP和ASIC。

2013-06-13 14:26:14 2714

2714 、Lauterbach、Embest、FujiSoft、iWave、Superlink、DIOIZ、MDS、BMR、ESA India、Micetek等,他們支持創(chuàng)新的Altera SoC平臺(tái)。出席人

2013-07-11 18:19:17 979

979 SoC——您的用戶可定制芯片系統(tǒng)

· 面向OpenCL的Altera SDK——新版SDK為當(dāng)今的開發(fā)人員開辟了FPGA新世界

2013-08-06 12:34:04 798

798 和SoC的HMC優(yōu)勢(shì)。這一展示表明了Altera的10代系列產(chǎn)品對(duì)HMC產(chǎn)品的支持進(jìn)行了早期驗(yàn)證,能夠及時(shí)將產(chǎn)品推向市場(chǎng),包括Stratix 10以及Arria 10 FPGA和SoC。

2013-09-05 17:49:29 1282

1282 Cyclone V SoC達(dá)到了925 MHz,汽車級(jí)達(dá)到了700 MHz,工業(yè)級(jí)Arria V SoC達(dá)到了1.05 GHz,在FPGA業(yè)界,這些器件成為性能最高的SoC。Altera SoC為嵌入式開發(fā)人員提供了最可靠的體系結(jié)構(gòu)、效能最高的開發(fā)工具以及密度最全的系列產(chǎn)品。

2013-09-26 17:48:23 2765

2765 現(xiàn)在,您可以采用 Altera SoC 器件來設(shè)計(jì)定制器件,這是我們流行的28 nm Cyclone V 和 Arria V 系列中的型號(hào)。我們的 SoC 器件將幫助您滿足多變的市場(chǎng)需求和接口標(biāo)準(zhǔn)。

2013-10-10 15:51:34 137

137 10月22號(hào),北京——Altera公司 (Nasdaq: ALTR)今天發(fā)布四款新參考設(shè)計(jì),這些設(shè)計(jì)采用了通過收購(gòu)Enpirion?而獲得的電源技術(shù)。參考設(shè)計(jì)為FPGA用戶和電路板開發(fā)人員提供了全包

2013-10-22 16:12:15 1409

1409 2013年11月25日 –貿(mào)澤電子(Mouser Electronics)即日起開始供應(yīng)最新的Terasic Technologies FPGA開發(fā)套件,支持Altera的Cyclone V片上系統(tǒng)

2013-11-26 11:11:02 1386

1386 2013年12月3號(hào),北京——Altera公司(Nasdaq: ALTR)今天發(fā)布了Arria 10版Quartus II軟件,這是業(yè)界第一款支持20 nm FPGA和SoC的開發(fā)工具。基于TSMC

2013-12-03 10:48:47 2106

2106 Altera的14 nm Stratix 10 FPGA和SoC以及ARM DS-5 Altera版SoC工具包贏得兩項(xiàng)2014設(shè)計(jì)創(chuàng)意獎(jiǎng)

2014-02-10 09:50:15 2739

2739 Altera公司與Wind River?風(fēng)河公司今天宣布,雙方建立戰(zhàn)略合作關(guān)系,為Altera的SoC FPGA器件開發(fā)并部署工具和解決方案。 風(fēng)河公司業(yè)界領(lǐng)先的操作系統(tǒng)和開發(fā)工具支持Altera基于多核ARM?處理器的SoC平臺(tái)。

2014-02-10 17:38:40 2798

2798 2014年8月5號(hào),北京——Altera公司(Nasdaq: ALTR)今年早些時(shí)候宣布了早期客戶基準(zhǔn)測(cè)試結(jié)果獲得成功,在此基礎(chǔ)上,今天發(fā)布面向Stratix? 10 FPGA和SoC的早期試用設(shè)計(jì)軟件,這是業(yè)界第一款針對(duì)14-nm FPGA的設(shè)計(jì)軟件。

2014-08-07 13:24:10 1042

1042 2014年8月19號(hào),北京——Altera公司(Nasdaq: ALTR)今天發(fā)布Quartus? II軟件Arria? 10版v14.0——業(yè)界最先進(jìn)的20 nm FPGA和SoC設(shè)計(jì)環(huán)境。

2014-08-19 15:53:24 2935

2935 2014年,12月16號(hào),北京——Altera公司(Nasdaq: ALTR)今天發(fā)布其Quartus? II軟件v14.1,擴(kuò)展支持Arria? 10 FPGA和SoC——FPGA業(yè)界唯一具有硬核浮點(diǎn)DSP模塊的器件,也是業(yè)界唯一集成了ARM處理器的20 nm SoC FPGA。

2014-12-16 13:48:53 1709

1709 2015年1月6號(hào),北京——Altera公司(NASDAQ: ALTR)今天宣布,奧迪的高級(jí)輔助駕駛系統(tǒng)(ADAS)選用其SoC現(xiàn)場(chǎng)可編程門陣列(FPGA),實(shí)現(xiàn)量產(chǎn)。

2015-01-06 10:31:35 1455

1455 Altera全球SoC FPGA開發(fā)者論壇活動(dòng)在深圳成功舉行,Altera合作伙伴、FPGA開發(fā)者和工程師匯聚一堂,共同關(guān)注使用基于ARM的SoC FPGA中的精細(xì)粒度異構(gòu)計(jì)算技術(shù),在滿足下一代嵌入式計(jì)算應(yīng)用需求中,如何解決系統(tǒng)設(shè)計(jì)的難題。

2015-11-13 17:38:16 2234

2234 Altera軟件和IP市場(chǎng)總監(jiān)Alex Grbic說,“我們很高興Plunify能成為我們的合作伙伴。與Plunify這樣的公司合作使我們可以向客戶提供更多相互支持的解決方案。”

2016-07-06 13:58:37 3133

3133 altera_soc_ebook_eeworld_20151215

2016-07-15 16:03:09 13

13 基于FPGA的可堆疊存儲(chǔ)陣列設(shè)計(jì)與優(yōu)化

2017-01-07 21:28:58 0

0 Plunify 將分別于2017年5月3日(成都)和2017年5月5日(長(zhǎng)沙)的2017Xilinx All Programmable 技術(shù)研討會(huì)。同時(shí)對(duì)于InTime時(shí)序優(yōu)化工具有興趣的朋友可以在Comtech科通展位上可以了解和參觀到具體InTime的演示。

2017-04-25 15:19:55 1191

1191 Plunify?基于機(jī)器學(xué)習(xí)技術(shù)的現(xiàn)場(chǎng)可編程門陣列(FPGA)時(shí)序收斂和性能優(yōu)化軟件供應(yīng)商,今天推出了Kabuto?,可最大限度地減少和消除性能錯(cuò)誤。

2018-07-04 12:24:00 3335

3335 本文闡明了InTime和Xilinx軟件是如何通過調(diào)整編譯參數(shù)以及運(yùn)行并行編譯來優(yōu)化FPGA時(shí)序性能的。InTime通過機(jī)器學(xué)習(xí)來決定一個(gè)FPGA設(shè)計(jì)的綜合和布局布線的最佳配置組合。通過和計(jì)算服務(wù)器

2017-11-15 15:17:05 1220

1220

的可編程邏輯公司,前所未有的提高了DSP性能、設(shè)計(jì)人員的效能和邏輯效率。硬核浮點(diǎn)DSP模塊集成在正在發(fā)售的Altera 20 nm Arria 10 FPGA和SoC中,也集成在14 nm Stratix

2018-02-11 13:34:00 7749

7749 具套裝平均快出2倍,保持了FPGA和SoC設(shè)計(jì)的軟件領(lǐng)先優(yōu)勢(shì)。 Quartus II軟件14.0版支持用戶更高效的迅速實(shí)現(xiàn)FPGA和SoC設(shè)計(jì)。最新版包括新的快速重新編譯特性,對(duì)設(shè)計(jì)進(jìn)行小改動(dòng)后,編譯時(shí)間縮短了4倍;以及同類最佳的PCI Express (PCIe) IP解決方案,性能達(dá)到企業(yè)級(jí)水平。

2018-02-11 13:37:00 5607

5607 Fujisoft公司在Altera SoC合作伙伴研討會(huì)上演講的主題:Fujisoft Android SoC FPGA解決方案

2018-06-26 11:57:00 3370

3370 該演示由Altera全球合作伙伴Fujisoft提供。演示在Altera SoC上面的Android應(yīng)用程序。并且Fujisoft演示了在FPGA邏輯上實(shí)現(xiàn)2D加速IP,達(dá)到高達(dá)54fps的效果。

2018-06-26 08:08:00 4129

4129 Altera現(xiàn)在是Intel公司旗下的可編程解決方案事業(yè)部(PSG),今天發(fā)布能夠讓Stratix 10 FPGA和SoC支持高達(dá)56 Gbps數(shù)據(jù)速率的收發(fā)器技術(shù)。Altera今天演示了FPGA

2018-08-19 09:31:00 1696

1696 的功能安全領(lǐng)先供應(yīng)商YOGITECH聯(lián)合開發(fā)的鎖步解決方案采用了Altera FPGA、SoC,認(rèn)證工具流程,以及YOGITECH的知識(shí)產(chǎn)權(quán)(IP)內(nèi)核。這一解決方案幫助客戶在Altera FPGA中輕松實(shí)現(xiàn)SIL3安全設(shè)計(jì),包括低成本Cyclone V FPGA和MAX 10 FPGA系列。

2018-08-31 16:46:00 1857

1857 管理技術(shù),在Enpirion PowerSoC器件中集成高級(jí)多模式數(shù)字控制(MMDC)電源功能。由數(shù)字電源專家組成的設(shè)計(jì)團(tuán)隊(duì)將重點(diǎn)關(guān)注Enpirion PowerSoC的擴(kuò)展功能、適用性和低功耗特性,進(jìn)一步提高Altera FPGA和SoC的功效。

2018-08-16 11:26:00 1216

1216 地縮短了編譯時(shí)間,提供通用、快速跟蹤設(shè)計(jì)輸入和置入式IP集成特性,延續(xù)了Altera Quartus II軟件的領(lǐng)先優(yōu)勢(shì),令基于FPGA和SoC的設(shè)計(jì)快馬加鞭。現(xiàn)在,客戶可以在更高抽象層面上進(jìn)行設(shè)計(jì)并實(shí)現(xiàn),極大地縮短了設(shè)計(jì)時(shí)間,解決了下一代設(shè)計(jì)面臨的挑戰(zhàn)。

2018-08-25 09:18:00 1061

1061 Altera公司與Mentor Graphics合作為嵌入式軟件開發(fā)人員提供同類最佳的Vista虛擬平臺(tái),它支持Altera全系列SoC FPGA,包括具有64位四核ARM Cortex-A53

2018-08-30 16:41:00 1307

1307 Altera公司今天宣布,使用MathWorks的業(yè)界標(biāo)準(zhǔn)工作流程,為其基于ARM的SoC提供新支持。MathWorks 2014b版包括了適用于Altera SoC的自動(dòng)、高度集成、基于模型

2018-09-08 10:04:00 1057

1057 仿真器的速度優(yōu)勢(shì)和時(shí)域波形仿真器的精度優(yōu)勢(shì),是一種新的混合行為仿真方法。JNEye工具經(jīng)過優(yōu)化,支持Altera 10代系列產(chǎn)品,為用戶提供了評(píng)估Altera下一代FPGA和SoC收發(fā)器鏈路性能的平臺(tái)。

2018-09-14 15:10:00 1764

1764 關(guān)鍵詞:Quartus , FPGA , Stratix 與以前的版本相比,只需要一半的時(shí)間就能實(shí)現(xiàn)業(yè)界性能最好的設(shè)計(jì) Altera公司今天宣布推出Quartus II軟件13.0版,這一軟件實(shí)現(xiàn)了

2018-09-25 09:12:01 1542

1542 Altera的Arria II GX、Stratix IV GT、StraTIx IV GX FPGAs和HardCopy IV GX ASIC采用了通用收發(fā)器技術(shù),由一套通用開發(fā)工具為其提供支持,幫助系統(tǒng)設(shè)計(jì)人員開發(fā)完整的芯片系統(tǒng)(SoC)解決方案。

2018-10-27 08:17:00 4515

4515 用軟件從 C 轉(zhuǎn)化來的 RTL 代碼其實(shí)并不好理解。今天我們就來談?wù)劊绾卧诓桓淖?RTL 代碼的情況下,提升設(shè)計(jì)性能。 本項(xiàng)目所需應(yīng)用與工具:賽靈思HLS、Plunify Cloud 以及 InTime。 前言 高層次的設(shè)計(jì)可以讓設(shè)計(jì)以更簡(jiǎn)潔的方法捕捉,從而讓錯(cuò)誤更少,調(diào)試更輕松。

2019-09-15 11:56:00 767

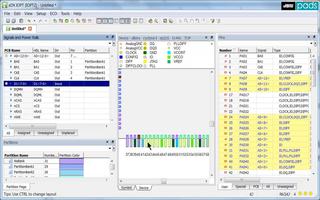

767 與 FPGA 軟件工具進(jìn)行自動(dòng)雙向信息交換可提供由供應(yīng)商規(guī)則驅(qū)動(dòng)的“設(shè)計(jì)即正確”的 I/O 分配,從而實(shí)現(xiàn)快速、無誤的優(yōu)化流程。其包括了最新的器件支持,并且可提前訪問尚未發(fā)布的 FPGA 供應(yīng)商器件。

2019-05-16 06:13:00 4264

4264

本文檔的主要內(nèi)容詳細(xì)介紹的是ALTERA公司的DE1 SoC FPGA開發(fā)板的培訓(xùn)教程免費(fèi)下載包括了:第1章 DE1-SOC 快速入門,第2章 DE1-SOC 硬件實(shí)驗(yàn),第3章 DE1-SOC 軟件

2019-07-08 08:00:00 51

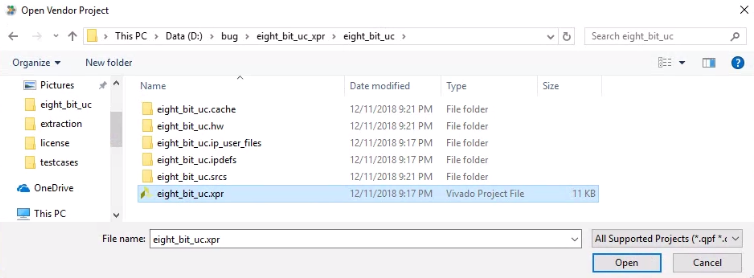

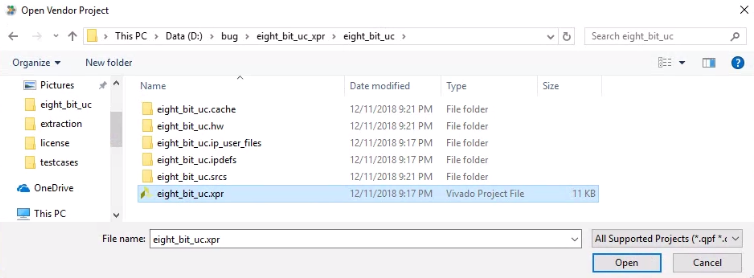

51 在學(xué)習(xí) Altera FPGA 開發(fā)之前,我們需要安裝 Altera 的 Quartus 軟件, Quartus 的軟件版本Altera每年都會(huì)有所更新, 用戶也沒有必要追求最新的軟件安裝版

2019-09-29 08:00:00 15

15 教程介紹 本教程旨在指導(dǎo)用戶通過 Plunify Cloud 的云服務(wù)器,來使用 InTime 軟件優(yōu)化 FPGA 設(shè)計(jì)。如果您首次使用 InTime,請(qǐng)免費(fèi) 申請(qǐng)?jiān)?b class="flag-6" style="color: red">軟件的本地試用 。 本教程涵蓋

2020-12-21 17:57:01 1942

1942

Altera FPGA CPLD學(xué)習(xí)筆記(肇慶理士電源技術(shù)有限)-Altera FPGA CPLD學(xué)習(xí)筆記? ? ? ? ? ? ? ? ?

2021-09-18 10:54:41 85

85 電子發(fā)燒友網(wǎng)站提供《在亞馬遜EC2云端使用Xilinx工具和InTime優(yōu)化設(shè)計(jì).pdf》資料免費(fèi)下載

2023-09-18 09:37:20 0

0 近期,英特爾子公司Altera推出了一系列FPGA軟、硬件和開發(fā)工具,使其可編程解決方案更易應(yīng)用于廣泛的用例和市場(chǎng)。Altera在年度開發(fā)者大會(huì)上公布了下一代能效與成本優(yōu)化的Agilex 3 FPGA情況,并宣布針對(duì)Agilex 5 FPGA提供新的開發(fā)套件和軟件支持。

2024-10-12 10:47:44 1504

1504 Altera 的 Agilex 3 FPGA 和 SoC 可在不影響性能的前提下顯著提高成本效益。其通過出色的 Hyperflex FPGA 架構(gòu)、先進(jìn)的收發(fā)器技術(shù)、更高的集成度和更強(qiáng)大的安全

2025-06-03 16:40:17 1412

1412

Altera Agilex? 3 FPGA和SoC FPGA Altera/Intel Agilex? 3 FPGA和SoC FPGA使創(chuàng)新者能夠?qū)⒊杀?b class="flag-6" style="color: red">優(yōu)化的設(shè)計(jì)提升到更高的性能水平。Agilex

2025-08-06 11:41:44 3808

3808

開銷急劇擴(kuò)大,導(dǎo)致上行帶寬的利用率出現(xiàn)瓶頸。 ? 為應(yīng)對(duì)這一挑戰(zhàn),Altera 正依托?Agilex SoC FPGA,提供由 AI 驅(qū)動(dòng)的 CSI 壓縮解決方案。結(jié)合 Altera 的?FPGA

2025-08-26 16:27:26 3478

3478 本文采用嚴(yán)謹(jǐn)?shù)幕鶞?zhǔn)測(cè)試方法,對(duì)全新推出的 Agilex 3 FPGA 和 SoC 產(chǎn)品家族進(jìn)行性能分析。該系列專為成本優(yōu)化型應(yīng)用設(shè)計(jì),兼具高性能、高集成度與高可靠性。

2025-10-27 09:37:28 582

582 近日,全球 FPGA 創(chuàng)新技術(shù)領(lǐng)導(dǎo)者 Altera 的 Agilex 5 FPGA 與 SoC 產(chǎn)品系列,榮獲 2025 年 AspenCore 全球電子成就獎(jiǎng)(WEAA)的處理器/DSP/FPGA 類大獎(jiǎng)。該獎(jiǎng)項(xiàng)旨在表彰在全球電子產(chǎn)業(yè)中展現(xiàn)卓越創(chuàng)新并推動(dòng)技術(shù)進(jìn)步的企業(yè)與個(gè)人。

2025-12-03 11:13:19 1347

1347

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論