在現(xiàn)代 5G 網(wǎng)絡(luò)中,快速且準(zhǔn)確的信道狀態(tài)信息 (CSI)更新是保障連接質(zhì)量、優(yōu)化 MIMO 配置并提供一致用戶(hù)體驗(yàn)的核心基礎(chǔ)。然而,隨著網(wǎng)絡(luò)密度的持續(xù)提升和流量規(guī)模的迅速激增,這些更新帶來(lái)的信令開(kāi)銷(xiāo)急劇擴(kuò)大,導(dǎo)致上行帶寬的利用率出現(xiàn)瓶頸。

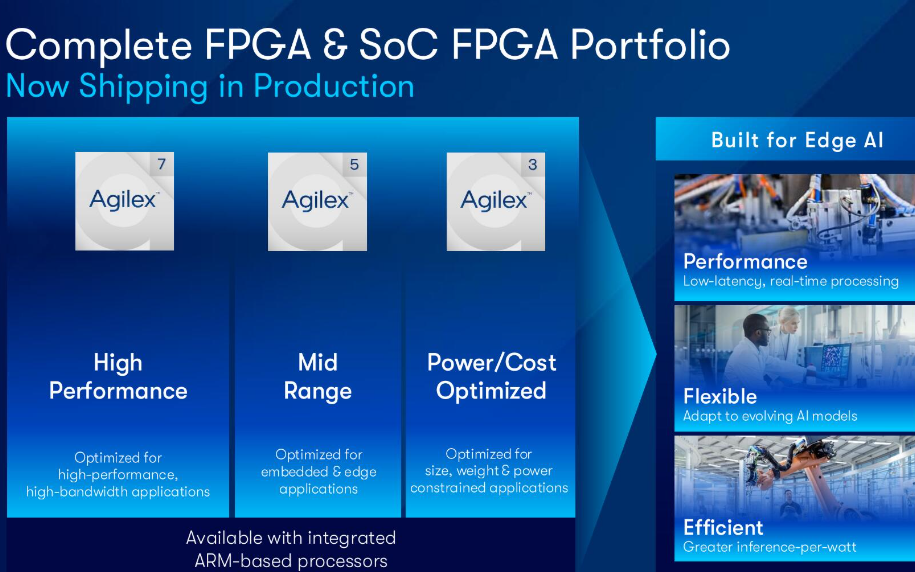

為應(yīng)對(duì)這一挑戰(zhàn),Altera 正依托Agilex SoC FPGA,提供由 AI 驅(qū)動(dòng)的 CSI 壓縮解決方案。結(jié)合 Altera 的FPGA AI 套件和 OpenVINO 開(kāi)源工具包部署深度學(xué)習(xí)模型。

該方案能夠?qū)⒏骂l率和信令負(fù)擔(dān)降低高達(dá) 99.9%,同時(shí)確保原始 CSI 數(shù)據(jù)與重構(gòu)后的數(shù)據(jù)之間保持0.9999 以上的相關(guān)性。

面向下一代 RAN 的高效壓縮解決方案

在高移動(dòng)性場(chǎng)景中,CSI 通常需要每個(gè)傳輸時(shí)間間隔更新一次,這無(wú)疑給上行鏈路容量帶來(lái)了持續(xù)的壓力。

針對(duì)這一問(wèn)題,新方案采用基于神經(jīng)網(wǎng)絡(luò)的自動(dòng)編碼器,通過(guò)在代表性信道數(shù)據(jù)上開(kāi)展訓(xùn)練,能夠以更高的準(zhǔn)確性實(shí)現(xiàn) CSI 壓縮和重構(gòu)。此舉不僅有助于減少信令數(shù)量,還能釋放頻譜資源供用戶(hù)數(shù)據(jù)使用,進(jìn)而全面提升整體網(wǎng)絡(luò)效率。

技術(shù)亮點(diǎn)

信令開(kāi)銷(xiāo)降低高達(dá) 99.9%,同時(shí)保持CSI 的無(wú)損保真度;

原始與重構(gòu)信道矩陣相關(guān)性高達(dá) 0.9999 以上;

基于FPGA AI 套件、OpenVINO 及Quartus Prime實(shí)現(xiàn)技術(shù)落地;

符合 3GPP 5G Rel-17 標(biāo)準(zhǔn),并可適配新興的 6G 框架。

這一解決方案清晰展現(xiàn)了如何借助高能效的 FPGA 邏輯結(jié)構(gòu),通過(guò)在邊緣實(shí)時(shí)執(zhí)行數(shù)據(jù)驅(qū)動(dòng)的優(yōu)化,以 AI 替代傳統(tǒng)人工調(diào)優(yōu)的啟發(fā)式方法。

以 FPGAi 打造更高效的無(wú)線(xiàn)解決方案

FPGAi 作為 Altera 面向 FPGA 架構(gòu)的 AI 原生方法,CSI 壓縮僅是其廣泛應(yīng)用中的一個(gè)典型案例。

FPGAi 還將驅(qū)動(dòng) RAN 系統(tǒng)向著更智能、更高效的方向持續(xù)演進(jìn)。借助 Agilex SoC FPGA,開(kāi)發(fā)人員能夠?qū)⑾冗M(jìn)的 AI 功能深度集成至無(wú)線(xiàn)信號(hào)鏈,進(jìn)而有效攻克帶寬、時(shí)延和功耗三大核心挑戰(zhàn)。

-

FPGA

+關(guān)注

關(guān)注

1652文章

22258瀏覽量

629427 -

Altera

+關(guān)注

關(guān)注

37文章

817瀏覽量

158027 -

AI

+關(guān)注

關(guān)注

89文章

37814瀏覽量

294910

原文標(biāo)題:Altera SoC FPGA 助力:AI 信道估計(jì)效率實(shí)現(xiàn)顯著提升

文章出處:【微信號(hào):英特爾FPGA,微信公眾號(hào):英特爾FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Altera發(fā)布 Quartus? Prime 專(zhuān)業(yè)版和 FPGA AI 套件 25.3 版:編譯更快,智能更強(qiáng)

Altera FPGAi解決方案助力mMIMO系統(tǒng)性能提升

Altera Agilex 3 FPGA和SoC產(chǎn)品家族的性能分析

Altera進(jìn)一步擴(kuò)展 Agilex? FPGA 產(chǎn)品組合,全面提升開(kāi)發(fā)體驗(yàn)

Altera Agilex 3/5 FPGA和SoC的功能特性

全球各大品牌利用NVIDIA AI技術(shù)提升運(yùn)營(yíng)效率

Altera SoC FPGA如何助力實(shí)現(xiàn)AI信道估計(jì)

Altera Agilex 3 FPGA和SoC產(chǎn)品介紹

使用Altera SoC FPGA提升AI信道估計(jì)效率

使用Altera SoC FPGA提升AI信道估計(jì)效率

評(píng)論