本文主要詳解基于FPGA的模糊PID控制器的設計實現,首先介紹了FPGA工作原理、基本特點以及FPGA的優勢,其次闡述了使用Altera的FPGA設計實現的數字模糊PID控制器,具體的跟隨小編一起來了解一下。

2018-06-01 09:26:51 18186

18186 PCBLayout QQ群312651747FPGA相關技術交流群QQ群198904805硬件設計技術交流QQ群375120144STM8技術交流QQ群112579730

2014-04-12 20:58:05

FPGA為什么是實現綠色搜索技術的關鍵?

2021-05-08 07:47:03

實現FPGA數字下變頻的多類濾波器分組級聯技術分析1 引 言 本文針對以下高效算法做了總結,進行合理的分組級聯并引入流水線技術以便于在FPGA上實現。數字下變頻(DDC)就是通過混頻、抽取和濾波等

2009-10-23 10:26:53

FPGA正在掀起一場數字信號處理的變革。本書旨在講解前端數字信號處理算法的高效實現。首先概述了當前的FPGA技術、器件以及用于設計最先進DSP系統的工具。第1章的案例研究是40多個設計示例

2023-09-19 06:38:28

本帖最后由 eehome 于 2013-1-5 10:01 編輯

IIR數字濾波器的Matlab和FPGA實現

2012-08-20 22:16:49

什么是數字中頻?FPGA怎么實現數字中頻?

2021-05-08 08:05:40

我們想從FPGA引腳或者SMA輸出,然后輸出電壓不夠,引腳應該是TTL3.3V,SMA應該是1-1.5V,然后想變成5V電壓,然后接調制器,請問有沒有相關的限幅放大器模塊?有沒有相關器件

2018-08-03 06:31:06

DSP技術廣泛應用于各個領域,但傳統的數字信號處理器由于以順序方式工作使得數據處理速度較低,且在功能重構及應用目標的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實現數字信號處理系統,具有很強的實時性和靈活性,因此利用FPGA實現數字信號處理成為數字信號處理領域的一種新的趨勢。

2019-10-17 08:12:27

求精通FPGA的指導怎么理解基于FPGA數字相關器的設計思路,懂的回貼。 詳談。

2014-04-20 12:52:59

近年來,軟件無線電已經成為通信領域一個新的發展方向,數字下變頻技術(Digital Down Converter-DDC)是軟件無線電的核心技術之一,也是計算量最大的部分。基于FPGA的DDC

2019-10-12 08:17:00

隨著集成電路技術的快速發展,半導體存儲、微處理器等相關技術的發展得到了飛速發展。 FPGA以其可靠性強、運行快、并行性等特點在電子設計中具有廣泛的意義。作為一種可編程邏輯器件,FPGA 在短短二十年

2019-10-08 10:08:10

便于改造實現。而信號處理的核心就是數字穩定校正(DSU),DSU的主要作用就是消除發射信號的相位抖動,使接收信號具有相參性。在數字技術飛速發展的今天,信號處理的硬件實現主要有FPGA和DSP等來實現

2015-02-05 15:34:43

基于FPGA的數字脈沖壓縮技術1.數字脈沖壓縮實現原理2.電路設計2.1APEX2OKE系列FPGA 簡介2.2 基于FPGA 的算法研究及實現 2.3 脈沖壓縮在FPGA 上的實現

2011-03-02 09:41:50

相關器功能只能通過一個應用編程接口(API)被主機處理器調用。圖34 XE16BB10的應用電路XE16BB10增益型信道相關器是GPS接收機的數字前端部分。可用于接收從Colossus射頻前端產生

2018-08-23 08:53:31

如何進行數字相關器基本模型分析、流水線型數字相關器模型及信號處理流程 ?

2021-04-06 06:47:28

本文基于FPGA的技術特點,結合數字復接技術的基本原理,實現了基群速率(2048kbps)數字信號的數字分接與復接。

2021-04-30 06:27:39

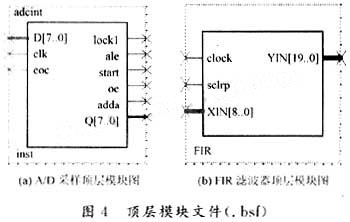

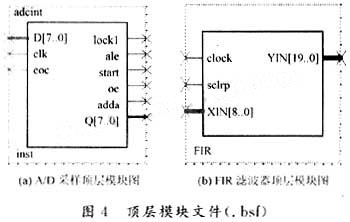

的各個領域。采用INMOS公司的IMS A100級聯型信號處理器為模板,以FIR濾波器設計為核心,用FPGA技術開發設計級聯型信號處理器,能夠應用于數字FIR濾波、高速自適應濾波、相關和卷積、離散

2019-07-30 07:22:48

求大佬分享利用FPGA技術實現的數字式頻分多路副載波解調器設計?

2021-04-08 06:52:08

請問如何利用FPGA嵌入式實現多比特自相關器的設計?

2021-05-06 09:47:25

如今,FPGA已成為數字信號處理系統的核心器件,尤其在數字通信、網絡、視頻和圖像處理等領域。現在的FPGA不僅包含查找表、寄存器、多路復用器、分布式塊存儲器,而且還嵌入專用的快速加法器、乘法器和輸入

2019-11-06 08:11:54

介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現方法,給出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC進行直接數字頻率合成的VHDL源程序。

2021-04-30 06:29:00

本文首先介紹了MQAM調制解調的基本原理,然后以64QAM為例,介紹了一種全數字實現的調制系統結構方案,并給出了解調器的具體FPGA實現方法及關鍵技術。

2021-04-30 06:46:14

本文在總結一般數字相關器設計的基礎上,設計實現了一種高性能的數字相關器。

2021-04-29 06:51:33

采用PCM編碼原理及FPGA編程技術實現PCM數字基群接口傳輸低速數據的接入

2021-04-30 07:09:04

怎么實現基于FPGA技術的智能導盲犬設計?

2021-05-08 07:37:31

怎么實現基于fpga+stm32的數字示波器設計?

2021-11-15 07:09:58

怎么利用FPGA實現數字電壓表的設計?

2021-05-06 10:19:03

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2019-08-19 06:15:33

求助FM調制器的FPGA實現,對FPGA這些完全不了解,在網上看可以用DDS技術實現FM的數字調制,就在書上按照步驟先做了產生正弦波分頻模塊尋址模塊數據存儲模塊,但編譯不能通過,也不知道該怎樣進行頻率調制,請問該怎樣實現頻率的調制,請問有人寫過頻率調制的verilog代碼嗎,急求,謝謝

2019-03-16 11:43:26

提出了用于音素識別的K子空間和時延自相關器神經網絡結構,用將時延設計加入線性自相關器,以擴展音素濾波神經網絡的方法,產生p維子空間,并采用迭代過程修改劃分,以便

2009-05-16 11:37:30 13

13 本文介紹了BOC 信號的基本結構,仿真了GPS 和Galileo 信號中采用的兩種BOC 信號的自相關函數以及鑒別器曲線。根據它們鑒別器曲線多個過零點的問題,用 2N 相關器法進行了分析和

2009-08-31 08:37:16 10

10 本文提出了一種QPSK 高性能數字調制器的FPGA 實現方案,由Altera 的IP 核NCO2.3.0 提供QPSK高穩定度的數字正弦信號,給出了QPSK 的實驗仿真結果。結果表明,基于NCO 的QPSK 數字調制器極大

2009-09-26 08:56:55 43

43 一種基帶GMSK信號相關器及其輸出概率分布該文提出一種基帶GMSK 信號相關器,并從GMSK 解調信號的相位概率分布函數以及獨立同分布隨機變量和的概率分布函數出發,給出了該

2009-10-28 23:33:22 14

14 本文介紹了數字下變頻的組成結構,并通過一個具體的實例,給出了FPGA 實現的具體過程。

2009-11-30 14:11:52 34

34 在數字通信的數據傳輸過程中,需要保持數據在傳輸過程中的同步,因此要在數據傳輸過程中插入幀同步字進行檢測,從而有效避免發送數據和接收數據在傳輸過程中出現的異步

2010-01-06 14:55:11 38

38 數字濾波器在FPGA中的實現

2010-02-09 10:21:27 77

77 介紹了一種基于新型FPGA的高速數字下變頻的實現方法,它充分利用數字下變頻的優化算法以及FPGA領域的新技術,去除由于數據速率過高而造成的各種瓶頸,極大地減少了計算量和FPG

2010-07-02 16:49:24 21

21 在數字通信的數據傳輸過程中,需要保持數據在傳輸過程中的同步,因此要在數據傳輸過程中插入幀同步字進行檢測,從而有效避免發送數據和接收數據在傳輸過程中出現的異步問題。

2010-07-21 17:21:47 15

15 本文提出了基于FPGA技術實現數字復接系統的設計方案,并介紹了有代表性的較簡單的四路同步復接器系統總體設計。硬件電路調試證明,該方案是行之有效的。

2010-08-06 16:33:16 30

30 提出一種基于DCT域的數字水印算法,并用FPGA硬件實現其中關鍵部分DCT變換。采用VHDL語言有效設計和實現DCT變換,分析與仿真結果表明:與軟件實現相比,用FPGA實現水印算法具有高

2010-12-28 10:22:14 20

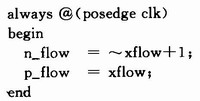

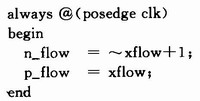

20 摘要:基于FPGA設計的數字相關器,對前端模數/轉換器在384kbps采樣率下采得的數據進行希爾波特變換,再與本地序列做相關運算,最后將相關結果送給DSP,供DSP做進一步的處

2006-03-11 13:26:25 1261

1261

摘要: 介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現方法,給出了采用ALTERA公

2009-06-20 14:14:36 989

989

基于FPGA嵌入式的多比特自相關器設計

引 言 確定性信號的不同時刻取值一般都具有較強的相關性;而干擾噪聲的隨機性較強,其不同時刻取值的

2009-11-13 10:06:04 1693

1693

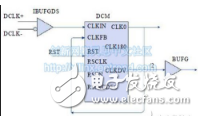

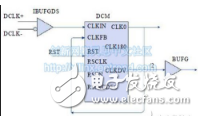

寬頻帶數字鎖相環的設計及基于FPGA的實現數字鎖相環(DPLL)技術在數字通信、無線電電子學等眾多領域得到了極為廣泛的應用。與傳統的模擬電路實現的

2009-11-23 21:00:58 1713

1713

基于FPGA的數字濾波器的設計與實現

在信息信號處理過程中,如對信號的過濾、檢測、預測等,都要使用到濾波器,數字濾波器是數字信號處理中使用最廣泛的一

2010-01-07 10:45:35 4082

4082

基于FPGA和CPLD數字邏輯實現ADC技術

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現

2010-05-25 09:39:10 1844

1844

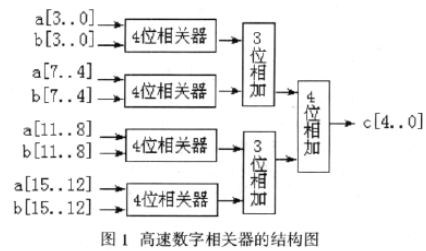

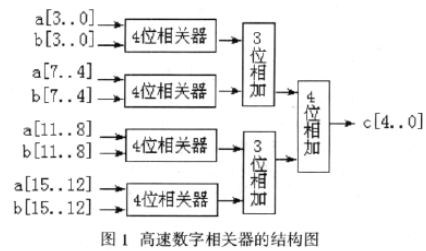

O 引言

數字相關器是擴頻通信體制下數字中頻接收機核心部件之一,在數字擴頻通信系統中應用廣泛,但由于受數字信號處理器件速度限制,無法應用于高速寬帶通

2010-10-20 09:53:47 1739

1739

數字相關器作為軟件無線電的典型應用,在擴頻通信中成為必不可少的技術。在傳統的擴頻通信中,采用模擬器件(如:聲表面波器) 來實現解擴單元,而用數字相關器可以增加系統的靈

2011-09-14 17:13:36 1336

1336

采用PN 碼序列滑動相關的方法,給出了一種超寬帶信號模擬相關器的設計方案。講述了該模擬相關器各個功能模塊的設計過程,并根據超寬帶信號的技術特點,設計并實現了基于該模擬

2011-09-20 17:46:33 57

57 本書共分8章,主要內容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設計中常用軟件簡介、用fpga實現數字信號處理的數據規劃、多種結構類型的fir數字濾波器的fpga實現、不同結構

2011-11-04 15:50:12 0

0 在Quartus Ⅱ開發環境下,用Verilog HDL硬件描述語言設計了一個可以在FPGA芯片上實現的數字時鐘. 通過將設計代碼下載到FPGA的開發平臺Altera DE2開發板上進行了功能驗證. 由于數字時鐘的通用

2011-11-29 16:51:43 184

184 為了實現對非相干雷達的接收相參處理,基于數字穩定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL編程語言,設計了一種基于FPGA的DSU硬件實現方法。實驗結果表明基于FPGA的

2012-06-26 15:48:36 27

27 2017-04-13 20:52:00 0

0 基于FPGA的數字鎖相環設計與實現技術論文

2015-10-30 10:38:35 9

9 結構類型的fir數字濾波器的fpga實現、不同結構fft的fpga實現、數字正交下變頻的fpga實現、cordic和dds的fpga實現等。

2015-12-23 11:07:46 47

47 數字圖像邊緣檢測的FPGA實現......

2016-01-04 15:31:55 18

18 Xilinx FPGA工程例子源碼:用FPGA實現數字鎖相環

2016-06-07 15:07:45 38

38 基于FPGA的空間太陽望遠鏡圖像相關算法實現

2016-08-30 15:10:14 21

21 數字成像領域中基于FPGA的圖像電子防抖技術的研究與實現

2016-09-17 07:27:00 10

10 數字信號處理的FPGA實現

2016-12-14 22:08:25 32

32 基于FPGA技術的數字相關器的設計與實現

2016-12-16 22:23:00 14

14 基于FPGA的全數字FQPSK調制器實現_楊峰

2017-03-19 11:38:26 2

2 便攜數字式相關器設計_高猛

2017-03-19 11:41:51 0

0 綜合孔徑輻射計中的數字相關處理器具有通道多、數據量和運算量極大的特點,對于處理器的處理速度要求很高,資源消耗巨大。基于節約資源的目的,采用了二級相關算法,即一級相關單元進行短點數的累加,二級相關單元

2017-11-03 10:19:29 0

0 設計和實現了基于FPGA的可編程數字下變頻器(DDC),用于寬帶數字中頻軟件無線電接收機中,主要完成了數字下變頻、數據抽取等功能。采用自頂向下的模塊化設計方法,將整個下變頻器劃分為基本單元,實現這些

2017-11-22 09:09:56 6993

6993

為同時完成4個Stokes 矢量參數的相關測量,反演海面風場,提出了新型數字相關器的設計方法。結合高速數字相關器在數字極化輻射計中的應用,介紹了高速數據采樣和相關處理系統。通過兩片高速A/D轉換器

2017-11-22 09:27:02 3245

3245 為同時完成4 個Stokes 矢量參數的相關測量,反演海面風場,提出了新型數字相關器的設計方法。結合高速數字相關器在數字極化輻射計中的應用,介紹了高速數據采樣和相關處理系統。通過兩片高速A/D

2017-11-26 08:15:35 6393

6393

根據2ICMA相關器的算法特點,在對比基于CPU并行的MPI集群、MPI+CUDA異構并行集群和Hadoop+ CUDA異構并行集群的架構特點的基礎上,提出了一種基于Hadoop+ CUDA平臺實現

2017-12-06 10:12:26 0

0 基于全加器型數字相關器存在的進位延遲過大的問題,實現了時分多址體制下的同步段數字相關,提高了同步段相關的可靠性。 0引言 數字相關器是擴頻通信體制下數字中頻接收機核心部件之一,在數字擴頻通信系統中應用廣泛,但由于受數

2018-01-18 03:49:01 2166

2166 本文檔內容介紹了基于IIR數字濾波器的FPGA實現,供參考

2018-03-02 13:45:19 36

36 本文檔的主要內容詳細介紹的是光纖系統課件之微環諧振器及相關器件的詳細資料說明。

2019-04-23 08:00:00 0

0 數字濾波器、DSP器件或可編程邏輯器件(如FPGA)實現。因為,用FPGA實現數字濾波器具有實時性強、靈活性高、處理速度快以及小批量生產成本低等優點,所以得到了較為廣泛的應用。本文以巴特沃思數字帶通濾波器為例,較為詳細地介紹了其設計和實

2020-08-06 18:50:00 3

3 采用FPGA設計芯片技術對多進制數字通信技術的QPSK調制器實現進行了設計研究,將調制器中原有多種專用芯片的功能集成在一片大規模可編程邏輯器件FPGA芯片上,實現了高度集成化,小型化。實際研究仿真表明,該方案具有突出的靈活性和高效性,為設計者提供了多種可自由選擇的設計方法和工具.

2020-07-22 17:51:13 15

15 近年來,數字AM調制技術應用越來越廣泛,具體應用中多采用專用的調制芯片完成。文中介紹一種在FPGA中實現數字AM調制的方法,采用該方法設計的系統具有使用靈活、擴展性強、便于集成等優點。文中先討論了

2020-07-31 17:50:22 20

20 本文檔的主要內容詳細介紹的是怎么樣才能使用FPGA實現數字系統內容包括了:FPGA簡介,為什么采用FPGA,開發平臺和設計工具,HDL(硬件描述語言),FPGA的設計原則,系統設計開發流程。

2020-08-11 15:29:00 9

9 相關器。本文采用流水線技術,研究了基于 FPGA的高速數字相關器的設計方法,并給出了 MAX+PLUSII環境下的仿真結果。

2020-08-13 16:56:30 1560

1560

擴頻碼的相關解擴是擴頻通信接收機的關鍵技術之一,主要介紹了數字相關器在全球定位系統(GPS)信號捕獲中的應用,并進行了FPGA實現。在設計中,采用了16路并行相關運算的方式加快相關解擴運算速度。在

2021-01-26 16:22:43 15

15 處理能力的現場可編程門陣列(FPGA)在成本、性能、體積等方面都顯示出了優勢。本文以此為背景,研究了基于FPGA的快速傅立葉變換、數字濾波、相關運算等數字信號處理算法的高效實現。

2021-02-01 16:11:00 17

17 ,使用~tera的Quartus II軟件,完成了其中的核心模塊——F盯算法的硬件實現,提高了處理速度;并運用DSP處理器,設計了一個基于FPGA的實時數字圖像處理系統.文中給出了系統的硬件電路和軟件算法模塊.仿真和調試結果表明:用FPGA與高速數字信

2021-02-05 15:54:00 142

142 本文討論了基于FPGA芯片的直接數字頻率合成器(DDS)的設計方法。因為DDS 的實現依賴于高速、高性能的數字器件,使用現場可編程器件FPGA,利用其高速、高性能及可重構性的特性,就能根據需要方便地實現各種不同頻率的信號輸出。

2021-03-02 17:11:32 36

36 實現圖像快速相關運算。1 bit相關算法以異或邏輯運算代替常規算法中的乘法,提高了運算速度,同時減小硬件實現復雜度。針對太陽米粒圖像,給出1 bit相關算法方案,并研制出基于H)GA+DSP架構的相關器。測試結果表明,該相關器的算法精度、相關運

2021-03-31 09:24:12 10

10 EDA技術使得電子線路的設計人員能在計算機上完成電路的功能設計、邏輯設計、時序測試直至印刷電路板的自動設計。本文介紹了以 VHDL 語言和硬件電路為表達方式,以 Quartus II 軟件為設計工具,最終通過 FPGA 器件實現數字時鐘的設計過程。

2021-05-25 16:28:10 40

40 基于FPGA的DDC(數字下變頻)設計與實現(電源技術審稿費多少)-該文檔為基于FPGA的DDC(數字下變頻)設計與實現講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-15 12:04:22 28

28 基于FPGA的數字下變頻器(DDC)的設計(ups電源技術轉讓)-基于FPGA的數字下變頻器(DDC)的設計.適合新手學習參考

2021-09-16 11:43:52 37

37 相關器抑制干擾信號的原理主要基于信號的相關特性,特別是在擴頻通信等應用中,其過程可以概括為以下幾點: 一、基本原理 相關器,也稱為相關接收器,利用信號的自相關特性,通過本地信號與接收信號的復現關系

2024-08-08 11:23:48 1918

1918

電子發燒友App

電子發燒友App

評論