深入理解AES算法的底層原理。

2017-10-26 14:40:07 47148

47148 ? ? Xilinx zynq系列FPGA實現神經網絡評估 本篇目錄 1. 內存占用 ??? 1.1?FPGA程序中內存的實現方式 ????1.2?Zynq的BRAM內存大小 ????1.3?一個

2022-07-10 09:24:45 2511

2511 AES加密算法流程圖如下圖所示: 明文P:未加密的原始數據;密鑰K:加密原始數據密碼,對稱算法中,加密與解密所需的密鑰相同,該密鑰不能直接進行傳輸,否則會造成密鑰泄露; 常規的做法是使用非對稱算法

2022-11-21 19:29:45 3809

3809

牢不可破。 AES加密核能同時用于FPGA核本身以及獨特 FlashROM (FROM) 內存的加密中。每個FPGA都被分成兩部分:FPGA陣列和FlashROM,兩者都可獨立編程,容許在不改

2019-07-09 09:11:44

操作,不包含列混淆操作。在最終輪中,執行字節替代、行移位和輪密鑰加操作。

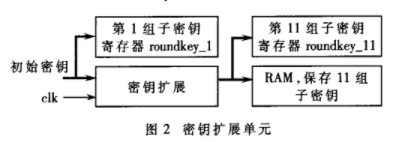

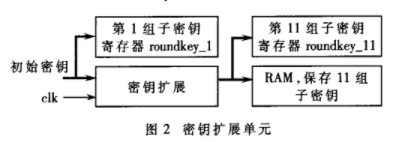

除此之外,AES每輪的加密密鑰都是由初始密鑰(128/192/256)擴展而來,對于AES-128,加密輪數為10輪,需要擴展

2025-10-23 06:13:43

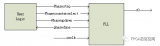

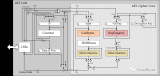

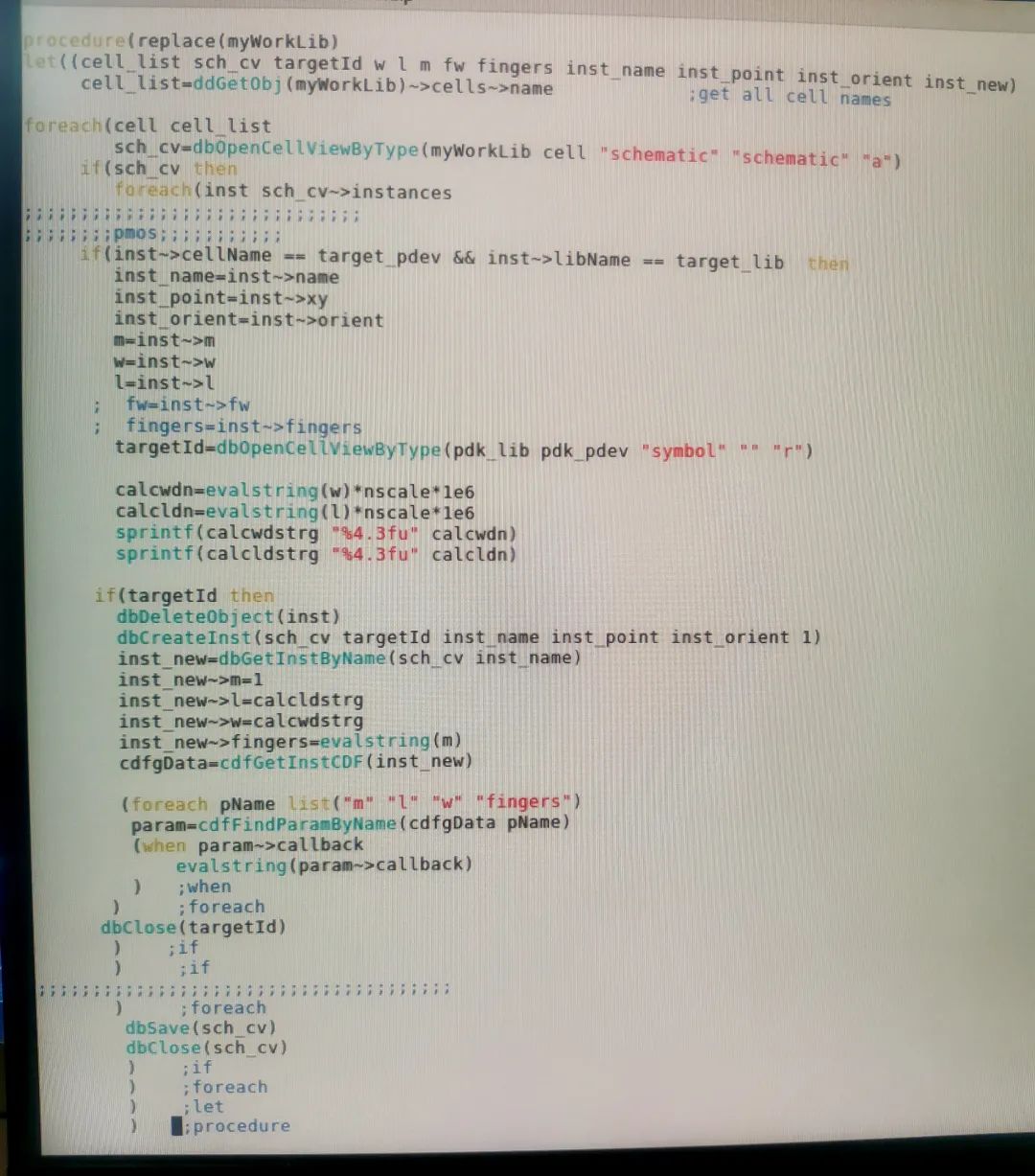

這次分享我們會簡要介紹AES加解密算法的邏輯實現,以及如何將AES算法做成硬件協處理器集成在蜂鳥E203 SoC上。

AES算法介紹

AES算法屬于對稱密碼算法中的分組密碼,其明文/密文分組長度為

2025-10-29 07:29:30

和SM4的算法流程圖再貼出來方便對比分析:

AES算法流程圖

SM4算法流程圖

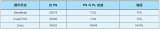

可以看到AES和SM4存在相同的操作符,例如異或、S盒替換、循環左移操作等。其中異或、循環左移操作符在理論上可以實現復用

2025-10-23 07:26:23

1、M487芯片CRYPTO模塊中對稱加密AES功能測試本次測評主要測試新唐M487芯片CRYPTO模塊中對稱加密AES功能及其性能,性能方面會使用硬件加速和純軟件實現直接的效率差異。M487中

2022-04-22 17:52:48

`廣播專業AES系列數字音頻光端機,采用先進的廣播和通信專業芯片。使用先進的FPGA、多路時分復用和時鐘恢復技術。輸入自動均衡,時鐘恢復,低抖動,透明傳輸完整AES格式信息。在1芯光纖上,傳輸10路

2011-03-13 22:54:43

。本方案以FPGA實現AES加密算法為目的,硬件角度加速AES加密。不知道這個方案有沒有吸引力,如果有的話就繼續寫設計方案了

2012-06-12 23:12:59

非常重要。通道狀態存儲器描述了在AES/EBU數據流通道中比特分配及其含義。例如的字節0的比 特0表示是家用級還是專業級,如果通道用于消費,字節0中比特0置0;用于專業時置1。奇偶校驗比特(P):通常為

2009-08-01 08:17:09

什么是AES算法?如何對AES算法進行優化?怎樣快速實現AES算法?

2021-04-28 06:51:19

本人想雇人用VHDL編寫一個用AES對一段文字或者圖像進行加密和解密。再實現的同時想看一下加密和解密所用的時間和速度。有哪位前輩有意,可以回復 價格再議。

2014-02-19 15:04:49

過程算不算是一種系統調用?在這篇博客中,我們會先簡單探究AES加解密的原理,然后對比ruby和golang的實現過程。產生的疑問在項目開發的過程中,我們時常會用戶會用到AES加解密, 但也僅僅是利...

2021-07-22 08:25:36

基于FPGA的可編程AES加解密IP

2021-01-21 07:39:11

嗨,我是一名本科生,也是使用FPGA套件的新手。在我的最后一個學期項目中,我使用Spartan 3A-3400 DSP套件實現AES,但我在查找AES-192和AES-256的verilog代碼

2019-09-11 11:24:58

加密。庫中的示例代碼“aes”不在 ESP 上運行,因為它涉及源代碼中包含的一些 avr 庫,但我隔離了庫的主要加密和解密部分,并設法編譯和運行代碼。使用我的代碼,我能夠定義純文本字符串,使用預定

2023-02-27 09:21:41

如圖,在custom_aes函數中,得到的結果是一個128位的數據,但是C卻不能定義這么大的數據,從而只定義32位的變量來接收這個結果,但是只能接收到低位的32位,請教各位大神,有沒有什么方法可以實現呢?

2023-08-16 07:53:24

圖3-3:逆S盒構造

2.AES加密算法在硬件上的優化

2.1字節替換與行位移

在俄歇算法迭代的過程中第一步就是進行字節替代,它屬于非線性變換.按照它的替換規則,輸入A對應唯一的輸出B、這

2024-06-19 19:50:22

Programmable AES Encryption IP可編程AES加密IP可以集成到FPGA中,實現了AES(Advanced Encryption Standard) Rijndael加解密

2018-11-15 09:28:49

我在 S32K118 硬件上啟用了 Csec 模塊。上位機需要執行軟件AES128-CMAC算法,然后將CMAC值發送給ECU進行校驗。但是我不知道如何實現AES128-CMAC,你能給我一些建議嗎?

2023-05-04 08:06:21

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一個單獨的奇偶校驗寫使能位,但在FPGA RAM中沒有單獨的Pariaty寫使能位。 如何實現ASIC RAM奇偶校驗寫入啟用ino FPGA RAM。謝謝娜文G K.

2020-04-24 09:37:05

大家好,我正在研究Spartan 6(xc6slx45csg324-2)評估板,我正在嘗試從xapp1014實現AES3串行數字音頻接口。AES3輸入和輸出按照AES3-Spec中的規定連接。我

2019-08-08 10:03:48

為了系統的擴展性和構建良好的人機交互,如何利用FPGA的硬件描述語言來實現AES的加解密算法?

2021-04-08 06:01:05

V3.00.0003

硬件:NuMaker-M2354 VER1.1

M2354系列MCU具有超低功率消耗特征,并有一個適合具有安全通信的IoT裝置的加密加速器。

該示例代碼用于在 AES GCM 中

2023-08-29 07:05:28

標準,主要用于保護電子數據的安全。AES 支持128、192、和256位密鑰長度,其中AES-128是最常用的一種,它使用128位(16字節)的密鑰進行加密和解密操作。AES屬于分組密碼,每次操作

2024-11-08 15:38:22

密鑰生成方案產生。大多數AES計算是在一個特別的有限域完成的。AES加密過程是在一個4×4的字節矩陣上運作,這個矩陣又稱為“狀態(state)”,其初值就是一個明文區塊(矩陣中一個元素大小就是明文區塊中

2016-08-12 11:58:43

。

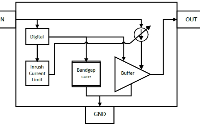

圖1

AES算法中的字節替代模塊是整個算法中唯一的非線性變換,不滿足f(x+m)=f(x)+f(m),因此需要單獨設計。AES的S盒包括仿射運算和GF(2^8)域上的求逆運算,其有限域運算可表示為

2025-10-28 07:38:53

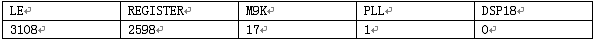

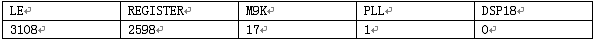

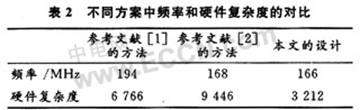

分析AES算法原理,構建基于FPGA的硬件實現框架,描述數據加解密單元和密鑰擴展單元的工作機制和硬件結構,引入核心運算模塊復用的設計思想,在不影響系統效率的前提下降低芯

2009-04-13 09:48:58 21

21 針對商業加密引擎中硬件資源和電路性能平衡問題,提出一種基于AES的低成本可重構的高速加密引擎的設計方案。該方案在AES加密算法的基礎上,根據FPGA內在的結構特點,利用VHDL語

2009-04-16 09:53:49 18

18 AES加密快速實現中利用了查表操作,查表的索引值會影響Cache命中率和加密時間,而查表的索引值和密鑰存在密切關系。通過分析AES最后一輪加密過程中查表索引值與密文和最后一輪

2009-04-18 09:42:35 32

32 文章簡單的介紹了GPON 的體系結構與下行幀的結構,并著重介紹了AES 加密的流程、方法與具體算法,最后對GPON 中的AES 加密,解密方法,AES 計數器模式在GPON中的使用進行了詳細

2009-12-14 10:23:11 16

16 AES 算法是新一代加密標準算法,文中對OpenSSL 中AES 算法的基本原理和性能進行了分析,針對其速度慢的缺點,提出了一些改進AES 算法的策略,改進的算法能有效提高加密算法操

2009-12-25 16:06:32 12

12 用硬件實現數據加密已成為信息安全的主流方向。本文提出了一種基于FPGA 的低成本的AES IP核的實現方案。該方案輪內部系統資源共用,減少了系統資源的占用。輸入密鑰與輸入數據

2010-01-06 15:11:03 11

11 AES(Advance Encryption Standard)標準由于其較高的安全性能已經在加密中得到了廣泛應用。為了進一步提高AES 標準的加解密速度,首先介紹了AES 加/解密原理、基本結構和算法流程,提出了

2010-01-15 15:29:17 13

13 本文實現了一種基于AES 算法的無線加密數字傳輸系統,給出了該系統的結構,完成了AES 算法在FPGA 上的實現,將音頻接口集成到FPGA,并用GPRS 網絡進行音視頻等數據的實時傳

2010-01-22 15:09:39 5

5 介紹AES 算法的原理以及基于FPGA 的高速實現。結合算法和FPGA 的特點,采用查表法優化處理了字節代換運算、列混合運算。同時,為了提高系統工作速度,在設計中應用了內外結合

2010-01-25 14:26:51 29

29 數字濾波器在FPGA中的實現

2010-02-09 10:21:27 77

77 在FPGA中實現高精度快速除法

2010-07-17 16:33:18 25

25 介紹AES算法的原理以及基于FPGA的高速實現。結合算法和FPGA的特點,采用查表法優化處理了字節代換運算、列混合運算。同時,為了提高系統工作速度,在設計中應用了內外結合的流水線

2010-07-17 18:09:43 46

46 乘累加器在DSP算法中有著舉足輕重的地位。現在,很多前端DSP算法都通過FPGA實現。結合FPGA具體的硬件結構,提出了乘累加器在FPGA中實現的改進方法:流水線技術、CSD編碼、DA算法,

2010-08-06 14:41:38 29

29 介紹了AES中,SubBytes算法在FPGA的具體實現.構造SubBytes的S-Box轉換表可以直接查找ROM表來實現.通過分析SubBytes算法得到一種可行性硬件邏輯電路,從而實現SubBytes變換的功能.

2010-11-09 16:42:48 25

25 在低成本FPGA中實現動態相位調整

在FPGA中,動態相位調整(DPA)主要是實現LVDS接口接收時對時鐘和數據通道的相位補償,以達到正確接收的目的。ALTERA

2010-03-25 11:45:07 3072

3072

AES算法中S-box和列混合單元的優化及FPGA技術實現

由于其較高的保密級別,AES算法被用來替代DES和3-DES,以適應更為嚴苛的數

2010-04-23 09:34:22 3473

3473

介紹了一種高斯拉普拉斯LOG算子在FPGA中的實現方案!并通過對一幅BMP圖像的處理!論證了在FPGA中實現的LOG算子的圖像增強效果

2011-05-16 17:12:24 50

50 本文在分析AES加密算法原理的基礎上,著重說明算法的實現步驟,用C語言完整地實現了AES算法的加/解密操作,并在PVR機頂盒中實現應用。

2011-09-24 01:00:58 2533

2533

差分功耗分析是破解AES密碼算法最為有效的一種攻擊技術,為了防范這種攻擊技術本文基于FPGA搭建實驗平臺實現了對AES加密算法的DPA攻擊,在此基礎上通過掩碼技術對AES加密算法進行優

2011-12-05 14:14:31 52

52 基于AES的加密算法具有速度快、強度高、便于實現等優點和ECC加密算法具有密鑰分配與管理簡單、安全強度高等優點,采用AES加密算法加密大數據塊,而用ECC加密算法管理AES密鑰,通過

2012-03-20 10:24:39 42

42 文中介紹了高級加密算法(AES)的基本原理,并給出了基于AES算法硬件加密模塊設計方案。通過Modelsim6.le對其進行仿真實現,仿真結果表明,該加密模塊能夠很好的實現AES算法

2013-02-21 15:52:41 0

0 TCAM在高速路由查找中的應用及其FPGA實現,TCAM在高速路由查找中的應用及其FPGA實現

2015-11-04 16:32:39 15

15 Xilinx FPGA工程例子源碼:在FPGACPLD中實現AD或DA的文章(英文Verilog)

2016-06-07 15:07:45 18

18 應用(諸如嵌入式系統中的應用等)中日漸流行的密碼規范。自從 2002 年美國國家標準技術研究所 (NIST) 將此規范選為標準規范以來,處理器、微控制器、FPGA和 SoC 應用的開發人員就開始利用 AES 來保護輸入、輸出及保存在系統中的數據。

2017-01-13 11:39:11 2753

2753

(Xilinx)FPGA中LVDS差分高速傳輸的實現

2017-03-01 13:12:04 66

66 AES是一種區塊加密標準算法,它的提出是為了升級替換原有的DES加密算法。因此它的安全強度高于DES算法。但不應片面理解,系統和數據的安全不僅與應用的加密算法有關,更與加密應用方案有關。和DES算法一樣,AES也屬于對稱加密算法,對密鑰的存儲與保護,直接決定了整個系統的安全。

2018-06-29 12:06:00 162676

162676 介紹了AES加密標準的Rijndael實現方法,設計了一種適合應用于嵌入式系統32位數據界面時序緊湊的AES加密IP核。該IP核能以較低的資源消耗實現在低端FPGA上速度為256Mb/s的AES加密,且可將數據位寬擴展為64位或128位等,滿足多種數據位寬應用的要求。

2017-09-07 19:14:58 13

13 根據AES算法的特點,從3方面對算法硬件實現進行改進:列混合部分使用查找表代替矩陣變換,降低算法實現的運算復雜度,采用流水線結構優化關鍵路徑一密鑰拓展,提升加密速度,利用FPGA定制RAM

2017-11-02 10:59:59 0

0 CC2541是一款基于BLE開發的芯片,該芯片白帶的AES協處理器(AES Coproc:essor)可以實現CBC、CFB、OFB、CTR、ECB、CBC MAC等多種加密解密算法。TI官方提供

2017-11-08 14:15:20 34

34 一種AES算法實現是采用輪展開的流水線結構,吞吐量很大可達到10 Gb/s量級,但消耗大量的邏輯面積。考慮在資源少的FPGA上實現AES算法,能滿足低端應用的加、解密速度一般不超過100Mb/s

2017-11-23 11:38:20 3675

3675 1 引 言 AES加密算法的一種優化的FPGA實現方法 隨著密碼分析水平,芯片處理能力和計算技術的不斷進步,des的安全強度已經難以適應新的安全需要,其實現速度、代碼大小和跨平臺性均難以繼續滿足

2017-11-30 01:31:26 2711

2711 針對輪函數在分組密碼實現過程中耗時過長的問題,提出了面向可重構密碼流處理器( RCSP)的高級加密標準( AES)算法軟件流水實現方法。該方法將輪函數操作劃分為若干流水段,不同流水段對應不同的并行

2017-12-01 17:15:26 1

1 由于對廣泛使用的AES算法的性能要求越來越高,基于軟件的密碼算法已經越來越難以滿足高吞吐量密碼破解的需求,因此越來越多的算法利用現場可編程邏輯門陣列( FPGA)平臺進行加速。針對AES算法在

2017-12-03 09:49:02 7

7 、FPGA 和 SoC 應用的開發人員就開始利用 AES 來保護輸入、輸出及保存在系統中的數據。我們可在更高抽象層上非常高效地描述算法,就像用于傳統軟件開發中那樣;但由于涉及到的操作,該算法在 FPGA 中實現起來最為高效。

2018-01-10 20:59:55 3750

3750

在FPGA中,動態相位調整(DPA)主要是實現LVDS接口接收時對時鐘和數據通道的相位補償,以達到正確接收的目的。ALTERA的高端FPGA,如STRATIX(r) 系列中自帶有DPA電路,但低端的FPGA,如CYCLONE(r)系列中是沒有的。下面介紹如何在低端FPGA中實現這個DPA的功能。

2018-02-16 17:32:33 11475

11475

的DES,已經被多方分析且廣為全世界所使用。本壓縮文件中對于AES的各個步驟分別打包為FUNCTION,便于查找。實現語言為matlab。

2018-05-25 15:18:19 11

11 隨著我國空間技術的快速發展,未來需要考慮空間數據安全性設計。傳統的星上加密 需要一個專門的裝置,占用的體積、功耗等資源均較大。AES 算法適用于軟硬件資源有限 的應用中,同時與軟件加密相比,采用

2018-12-30 09:31:00 6571

6571

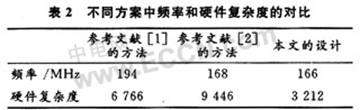

AES算法作為DES算法的替代者應用非常廣泛,其硬件實現方法已有不少討論,主要是通過提高算法頻率來提高吞吐量。但是在實際運行中,為了保證整個加密系統的穩定性,通常全局時鐘頻率較低,不可能達到算法的仿真頻率,如PCI接口電路時鐘頻率只有33MHz,因此實際數據吞吐量仍然較低。

2019-04-18 08:15:00 4156

4156

在使用單片機中,unsigned int 占2個字節,unsigned char 占一個字節。而單片機是實行的字節尋址。16字節的bit尋址實在是不好用.

2019-09-07 10:17:14 4063

4063

單元數據替換另一個。AES使用了如下幾種不同的技術來實現置換和替換。字節替代(SubBytes):通過非線性的替換函數,用查找表的方式把分組的字節矩陣中的每個字節用同一個S-BOX替換成另外一個字節

2019-12-06 21:57:54 8872

8872 AES算法的主要數學基礎是抽象代數,其中算法中的許多運算是按單字節(8bits)和4字節(32bits)定義的,單字節可看成有限域GF(2)中的一個元素,而4字節則可以看成系數在GF(2)中并且次數

2020-01-17 14:19:00 16

16 Rijndael算法為高級加密標準AES。AES密碼算法的加密速度快,安全級別高,已經成為加密各種形式的電子數據的實際標準。目前,針對AES密碼算法的加密技術已成為研究熱點。論文提出了一種低成本的AES密碼算法的硬件實現方法,并且使用FPGA器件實現了具體的設

2020-03-19 17:16:22 7

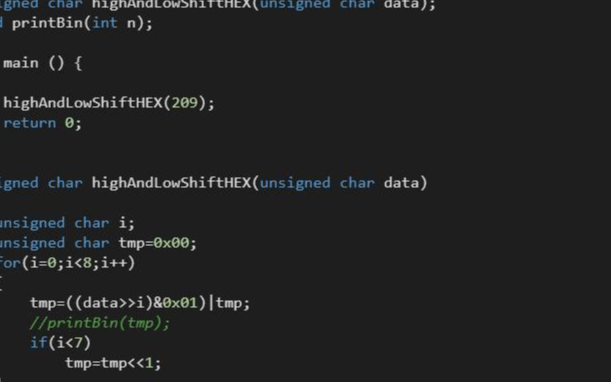

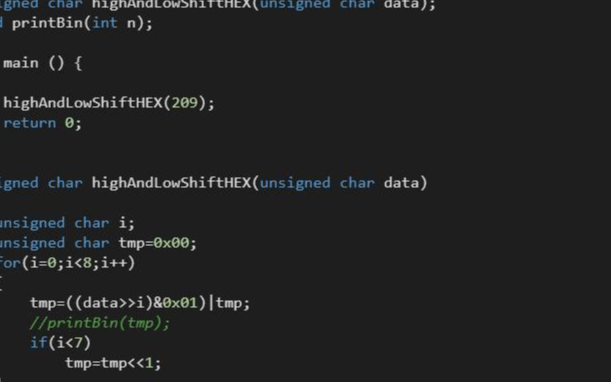

7 最近的協議中遇到字節高低位轉換的問題,于是偷懶上網查看,遇到類似的問題,也認識一個新的名字,叫做蝶式交換 問題是這樣子的 協議要求字節低位在左,高位在右,對每個字節做轉換處理,逐個交換其高低位,例如

2020-12-06 09:52:00 7702

7702

在FPGA中,實現邏輯的基本單元是查找表(LUT)而非基本門電路。目前的FPGA中,單一LE或者Cell通常能實現至少4輸入查找表的邏輯功能。

2020-12-29 17:27:22 14

14 由于AES算法的硬件實現較為復雜,在此提出一種優化算法中S—box和列混合單元的方法。其中S—box通過組合和有限域映射的方法進行優化,列混合單元使用算式重組的方法進行優化。這些優化設計通過組合邏輯

2021-01-25 14:27:14 20

20 通過將AES算法模塊化、運算一般化,給出了類AES算法的統一框架。在此框架下不僅可以同時實現AES的加密、解密,而且可以通過外部參數動態設定分組算法,使得密碼算法的使用更加靈活、安全。給出了算法的FPGA實現。結果表明設計方案可行,速度較高。

2021-03-26 15:58:04 16

16 基于FPGA的AES算法中S-box和列混合單元優化

2021-06-08 10:52:39 7

7 FPGA設計中DAC控制的Verilog實現圖文稿(ltspice 放置電源)-該文檔為FPGA設計中DAC控制的Verilog實現圖文稿資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-26 12:17:02 10

10 FPGA設計中DAC控制的Verilog實現(單片機電源維修)-該文檔為FPGA設計中DAC控制的Verilog實現資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-26 12:18:48 18

18 FPGA設計中DAC控制的Verilog實現修訂稿(空調電源芯片)-該文檔為FPGA設計中DAC控制的Verilog實現修訂稿資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-26 13:13:56 10

10 FPGA在運行期間,把配置文件存儲在SRAM中。SRAM是易失性的。掉電之后會丟失,所以FPGA每次上電都要從外部的Flash中加載數據到FPGA。這樣在加載時Flash中的數據很有可能被攔截,被

2021-07-27 14:19:09 3320

3320

FPGA中LPM_ROM設計快速實現(嵌入式開發的硬件環境)-該文檔為FPGA中LPM_ROM設計快速實現總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-08-04 10:45:04 10

10 FPGA_ASIC-MAC在FPGA中的高效實現(理士電源技術有限公司)-該文檔為FPGA_ASIC-MAC在FPGA中的高效實現講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-08-04 19:03:13 8

8 考慮 AES 加密數據沿以太網鏈路以 1G、10G 或更高的速率流式傳輸的位置。攻擊者可以攔截并存儲傳遞的消息,以便在嘗試破解加密之前進行后續分析。他將快速生成大量數據包,并且只有源地址和目標地址

2022-10-20 10:29:27 1060

1060 本文檔介紹了AES 硬件 IP 功能。高級加密標準 (AES) 是 OpenTitan 協議中使用的主要對稱加密和解密機制。 AES 單元是一個加密加速器,它接受來自處理器的請求以加密或解密 16 字節的數據塊。它作為外設模塊連接到芯片互連總線,符合外設功能的要求指南。

2023-08-03 10:46:50 2084

2084

電子發燒友網站提供《在Virtex-6 FPGA中使用全數字VCXO替換技術實現三倍速率SDI直通.pdf》資料免費下載

2023-09-14 14:52:17 5

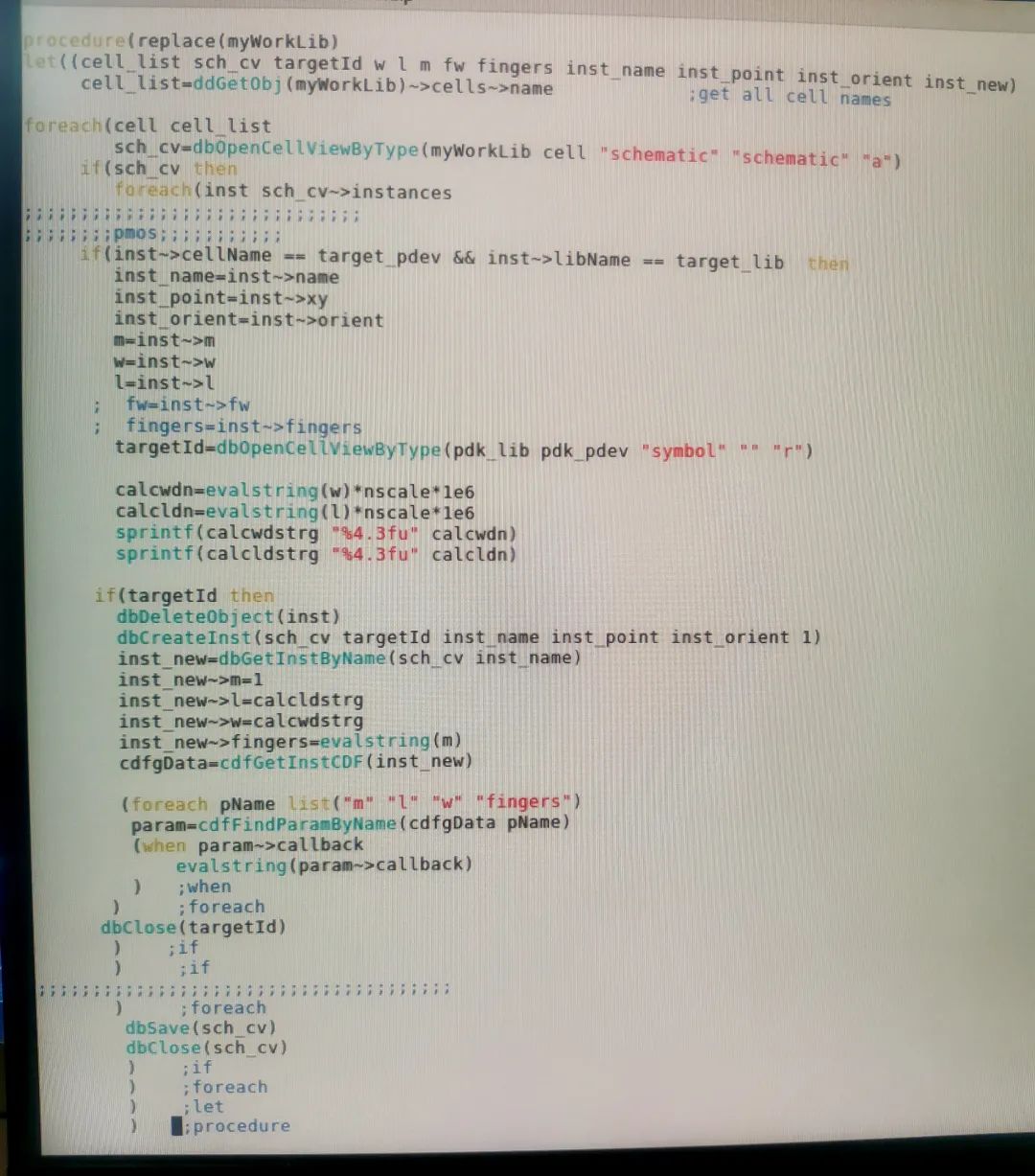

5 IC設計中,時常會遇到工藝替換的問題,使用新工藝替換舊工藝,或者這家的換那家的。

2023-10-12 14:24:11 11690

11690

可編程AES加解密IP內建密鑰擴展功能,使用初始密鑰產生擴展密鑰,用于加解密過程。可編程AES加解密IP處理128-bit分組數據,并且支持可編程的密鑰長度:128-bit,192-bit和256-bit。

2024-01-09 10:49:45 1203

1203

AES算法由美國國家標準與技術研究院(NIST)于2001年正式采納為加密標準,它是一種基于塊的加密算法,使用128位、192位或256位的密鑰長度,對數據塊進行加密。AES算法的核心是一系列變換,包括SubBytes(字節替換)、ShiftRows(行移位)、MixColumns(列混

2024-11-14 15:09:40 1732

1732 ,使用相同的密鑰進行加密和解密。它支持128、192和256位的密鑰長度,具有很高的安全性。AES加密過程包括多個輪次,每一輪包括四個步驟:SubBytes(字節替換)、ShiftRows(行移位)、MixColumns(列混淆)和AddRoundKey(輪密鑰加)。這些步驟共同確保了數據的安全

2024-11-14 15:11:06 1542

1542 的歸納以及相應的解決方案: 常見錯誤 編碼問題 : 在將字節數組轉換成字符串時,如果使用了不同的編碼格式,可能會導致解密后的數據出現亂碼。 密鑰長度問題 : AES算法支持128位、192位和256位三種密鑰長度。如果加密和解密時使用的密鑰長度不一致,會導致加密結果無法正確解

2024-11-14 15:13:03 5484

5484 AES算法(Advanced Encryption Standard,高級加密標準)在移動應用中的應用場景十分廣泛,主要體現在以下幾個方面: 1. 數據傳輸安全 在移動應用中,用戶經常需要通過網絡

2024-11-14 15:14:35 1384

1384 國產電壓基準源替換REF3025在工業電源管理應用中的替換方案

2025-03-19 09:44:28 975

975

電子發燒友App

電子發燒友App

評論