在FPGA中,動態相位調整(DPA)主要是實現LVDS接口接收時對時鐘和數據通道的相位補償,以達到正確接收的目的。ALTERA的高端FPGA,如STRATIX(r) 系列中自帶有DPA電路,但低端的FPGA,如CYCLONE(r)系列中是沒有的。下面介紹如何在低端FPGA中實現這個DPA的功能。

實現架構

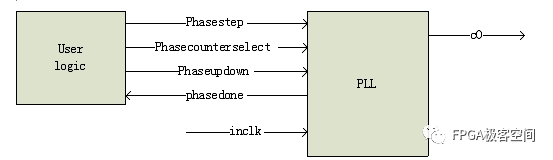

在LVDS輸入接收時,時鐘和數據的相位可能是不確定的,因此我們需要將時鐘的相位作出調整,使得時鐘能穩定的采集到輸入數據。工作的核心就是用鎖相環PLL的相位調整功能,產生若干個時鐘的不同相位,看哪些相位能準確的采集到輸入數據,然后取窗口中間的一個時鐘相位,作為正常工作時的采樣時鐘。比如通過PLL產生0,45,90,135,……,315度8個相移的時鐘,如果0,45,90度相移的時鐘能正確采樣到輸入,那么最后選取中間相位,即45度的時鐘作為采樣時鐘。這樣接口上具有最大的時序裕量,從而保證鏈路的可靠性。下圖為這個設計的基本結構,通過PLL調整相位的接口,產生了時鐘的不同相位來采集數據,最后選擇一個最合適的相位。

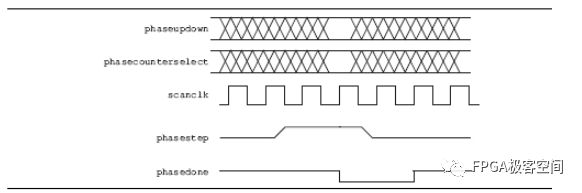

CYCLONE系列的PLL的相位調整接口時序如下圖所示:

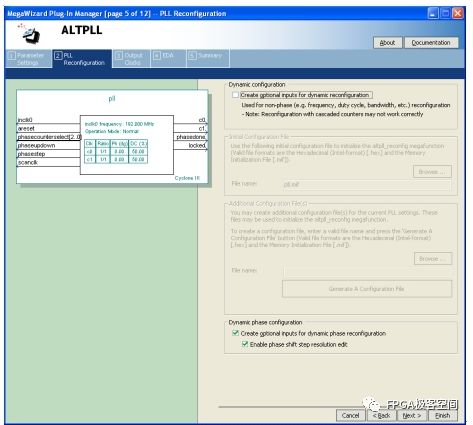

當用戶邏輯控制phasestep, phasecounterselect與phaseupdown信號時,PLL的輸出時鐘C0就改變一次相位。在QII生成PLL時,用戶必須選上create optional inputs for dynamic phase reconfigure,否則缺省是不會有這些管腳的,如下圖所示。另外必須在output clock tab中寫入phase shift step resolution的值,這樣才能確定每次相位調整的步長。

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636231

原文標題:低成本FPGA中實現動態相位調整

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

工業智能網關如何實現低成本數字化改造

利用1688價格API實現匯率動態調整,優化國際采購成本

電能質量在線監測裝置的暫態數據補傳的優先級如何在實際應用中進行動態調整?

風華電阻:低成本與高穩定性家電應用

MEMS組合導航如何實現超低成本?

商品價格動態調整接口技術詳解

動態調整同步周期的具體方法是什么?

還在為導航成本高而煩惱?組合導航開啟低成本新時代

低成本組合導航能實現精準導航定位

PLL技術在FPGA中的動態調頻與展頻功能應用

力矩電機并聯使用中的相位角調整

PanDao:通過可生產性調控實現光學設計流程的動態優化

藍牙定位低成本能否實現?

800V低成本壓縮機控制方案

低成本FPGA中實現動態相位調整方案

低成本FPGA中實現動態相位調整方案

評論