基于DSP的圖像采集與處理系統與傳統的PC端的系統相比,具有功耗低、攜帶方便、處理速度快的特點,被廣泛使用在圖像采集與處理領域。DSP(Digital Signal Process or)芯片也稱數字信號處理器,是TI公司推出的專用于數字信號處理系統中進行算法處理的微處理器器件。DSP采用哈佛結構總線設計,程序存儲器和數據存儲器分開,取值和數據訪問可以同時進行。DSP還使用流水線操作,使得多條指令重疊進行操作,可以有效地提高指令執行效率。此外,DSP還擁有獨立的硬件乘法器,在處理濾波、卷積等運算時具有很快的速度,因此,DSP特別適合在圖像采集與處理系統中作為核心器件。視頻采集端的視頻解碼芯片使用TVP5150,將采集到的模擬圖像信號轉換成數字圖像信號。

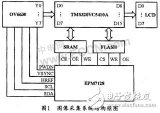

1 系統設計整體架構

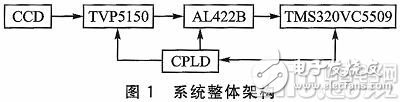

本系統是基于DSP的數字圖像處理系統,總體結構設計如圖1所示。首先CCD攝像機拍攝視頻圖像,輸出標準PAL制式視頻信號,輸入到視頻解碼芯片TVP5150中,TVP5150將模擬圖像信號轉換為數字圖像信號送入FIFO中,本系統采用AL422B。DSP通過EMIF接口從FIFO中讀取圖像數據并存入存儲器,圖像數據經過DSP中算法處理后,通過仿真器傳輸到PC機上進行顯示。其中,CPLD負責FIFO的讀寫指針復位和讀寫使能控制等工作。

(First In First Out)是一種先進先出的數據緩存器。FIFO與其他存儲器的區別是沒有讀寫地址線,操作可以變得很簡單,而且,它只能將數據順序寫入,并且順序讀出。此外,FIFO還具有以下一些特點:

①對連續的數據進行緩存,防止數據的丟失。

②可以對數據進行集中存儲,使CPU總線避免頻繁的操作。

③允許系統進行高速的DMA操作,即可以不通過CPU的干預,直接進行數據存儲,節約了使用CPU的時間,使系統的效率大大提高。

FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀寫時鐘必須是同一個時鐘,而異步FIFO可以接受一種時鐘寫入數據,另一種時鐘讀出數據,也就是讀寫時鐘可以不一致,能夠相互獨立。

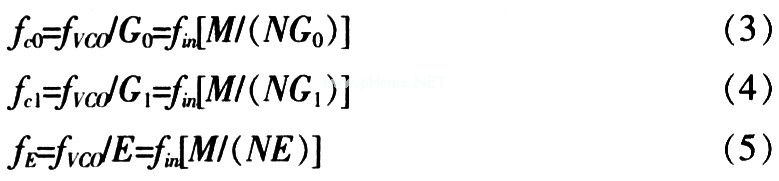

由于本系統中TVP5150送數據到DSP時,TVP5150的寫時鐘和DSP的讀時鐘是不一樣的。TVP5150的輸出時鐘是27 MHz,數據位為8位寬度,那么每秒的數據量就是216 Mbps,而DSP的輸出時鐘很難匹配27 MHz的時鐘頻率,設置為33 MHz,8位數據寬度,那么最大傳輸速率為264 Mbps。顯然,兩者的數據傳輸量在單位時間內是不一樣的,如果這時不經過任何緩存就進行數據間的相互傳輸,系統無法同步操作,并且會進入一種亞穩定狀態,從而整個系統功能失常。為了避免亞穩定狀態以實現系統數據的高速穩定的傳輸,本系統使用了異步FIFO作為解決方案,且采用AL422B作為異步FIFO存儲器,容量為3MB(393 216字節×8位),可以存儲PAL制式一幀圖形的信息。它的一些技術指標如下:

①支持VGA、CCIR、NTSC、PAL和HDTV制式的視頻信號;

②獨立的讀寫操作,可以接受不同的I/O速率;

③讀或寫周期為20 ns;

④訪問時間為15 ns;

⑤輸出使能控制;

⑥具有DRAM自刷新功能;

⑦3.3 V或5.0 V供電。

AL422B的讀寫過程分為4個步驟:寫復位,寫使能,讀復位,讀使能。首先復位寫指針![]() ,當寫使能

,當寫使能![]() 為低電平時,在WCK的上升沿將數據寫入到寫數據寄存器;當

為低電平時,在WCK的上升沿將數據寫入到寫數據寄存器;當![]()

為高電平時,寫操作被禁止。然后復位讀指針![]() ,當

,當![]() 都變為低時,在RCK的上升沿將數據寫入讀數據寄存器;反之,讀操作被禁止。

都變為低時,在RCK的上升沿將數據寫入讀數據寄存器;反之,讀操作被禁止。

2 系統硬件設計

2.1 TVP5150與AL422B的接口實現

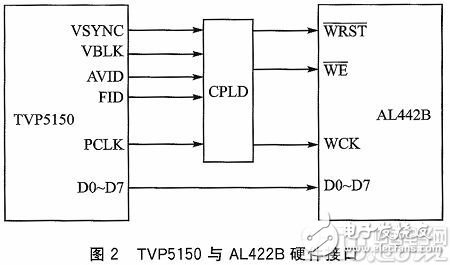

在本系統中,TVP5150的數據輸出端要與AL422B的數據寫入端相連,AL422B的數據讀出端要與DSP的數據輸入端相連。首先介紹TVP5150與AL422B之間的硬件連接,TVP5150的數據總線可以與AL422B的寫入端的數據總線直接進行連接。

TVP5150的輸出時鐘需要進行二分頻并移相半個時鐘周期,然后與AL422B的寫時鐘WCK連接,因為我們只需要獲取灰度圖像,這樣做可以將彩色部分的圖像濾除并且可以減少數據量。

TVP5150端的VSYNC、VBLK、AVID、FID借助CPLD進行邏輯組合后與AL422B的寫指針復位WRST和寫使能WE連接。具體邏輯組合將在軟件設計部分介紹。

TVP5150與AL422B接口如圖2所示。

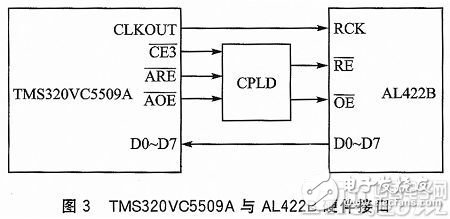

2.2 TMS320VC5509A與AL422B的接口實現

TMS320VC5509A(以下簡稱5509A)要接收來自AL422B中的數據,需要將AL422B的讀數據總線與5509A的EMIF數據總線接口直接連接。5509A的輸出時鐘CLKOUT給AL422B提供讀時鐘。AL422B的輸出使能![]() 和讀使能

和讀使能![]() 需要借助CPLD將5509A端的外部存儲器片選信號

需要借助CPLD將5509A端的外部存儲器片選信號![]() 、EMIF接口輸出使能

、EMIF接口輸出使能![]() 和EMIF接口讀使能

和EMIF接口讀使能![]() 進行邏輯組合后進行連接。組合邏輯部分在軟件設計部分介紹。TMS320VC5509A與AL422B接口如圖3所示。

進行邏輯組合后進行連接。組合邏輯部分在軟件設計部分介紹。TMS320VC5509A與AL422B接口如圖3所示。

3 系統軟件設計

軟件部分分為兩部分,分別是DSP內的程序設計和CPLD中的組合邏輯。

3. 1 DSP主程序

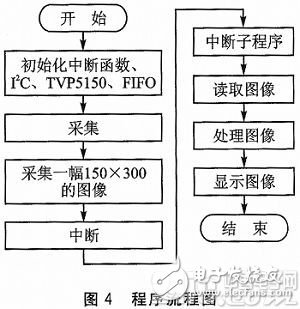

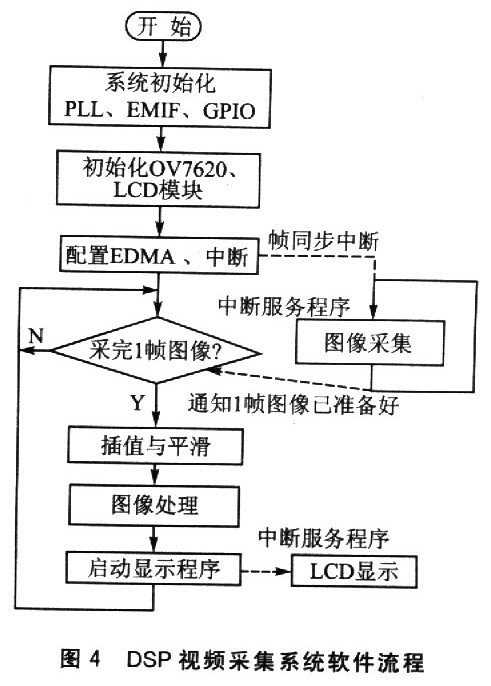

程序流程圖如圖4所示。

3.1.1 主函數初始化

主函數需要對時鐘頻率、中斷函數、EMIF外部存儲器接口、I2C總線、TVP5150視頻配置、AL422B的寫指針復位進行初始化。

其中,AL422B的初始化采用TMS320VC5509A的GPIO口GPIO0、GPIO1、GPIO2發送邏輯電平到CPLD,然后由CPLD發送命令控制AL422B的讀寫指針復位與讀寫使能。

在DSP中,首先定義GPIO口的方向控制寄存器IODIR和引腳電平寄存器IODATA,并將IODIR寄存器的低3位設為1,也就是將GPIO0、GPIO1、GPIO2的方向設為輸出。接著對IODA TA寄存器進行賦值,并將寄存器的值通過GPIO口送到CPLD,CPLD端進行邏輯組合,對AL422B的復位寫指針![]() 復位。

復位。

3.1.2 初始化TVP5150

TVP5150是視頻解碼芯片,要求其模擬輸入是PAL制信號,轉換為8位的YUV4:2:2格式的數字輸出信號。DSP需要通過GPIO口對TVP5150進行復位,方法類似于AL422B的寫指針復位控制。DSP還需要通過I2C總線控制TVP5150的寄存器,TVP5150寄存器的配置如下:

①雜項控制寄存器:地址0x03,設置為0x0f。

②輸出和數據比率選擇寄存器:地址0x0d,設置為0x40。

③配置復用引腳寄存器:地址0x0f,設置為0x0a。

④有效像素開始高位寄存器:地址0x11,設置為0x4d。

⑤有效像素開始低位寄存器:地址0x12,設置為0x02。

⑥有效像素結束低位寄存器:地址0x13,設置為0xe4。

⑦有效像素結束低位寄存器:地址0x14,設置為0x02。

經過寄存器配置,使得場消隱信號VBLK、像素有效信號AVID、場同步信號VSYNC、奇偶場標志位信號FID、輸出時鐘SCLK輸出有效,數據總線激活,并將采集到的圖像裁剪成150×300的圖像。

在初始化程序后,執行while死循環,等待中斷的到來。

3.1.3 中斷函數

由于只需要處理150×300的圖像,所以在FIFO里只需存儲150×300個像素點,存滿后發出中斷信號,DSP轉去執行中斷服務程序。中斷函數首先通過GPIO口告知CPLD使AL422 B的讀指針復位(方法類似AL422B的寫指針復位,這里不再贅述),并且使AL422B的輸出使能![]() 有效、讀使能

有效、讀使能![]() 有效(具體實現在3.2說明)。然后DSP便讀取FIFO中的數據,因為FIFO外擴在DSP的

有效(具體實現在3.2說明)。然后DSP便讀取FIFO中的數據,因為FIFO外擴在DSP的![]() 這個空間,地址為0x600000,所以DSP將

這個空間,地址為0x600000,所以DSP將![]() 中的數據寫入內存中,存入內存中的數據供后續處理。

中的數據寫入內存中,存入內存中的數據供后續處理。

這里,我們使用的處理算法為圖像的邊緣檢測法,處理完成后在CCS中進行顯示,并觀察算法處理結果。

最后,進行寫指針復位,準備下一次的圖像采集。需要注意的是,由于圖像在傳輸過程中奇偶場是分開傳輸的,FIFO中只存儲奇場的一部分圖像,而完整的圖像是由奇場和偶場共同組成的,所以獲得的圖像顯示的是一幀圖像壓縮一半的結果,圖像是失真的。但是,我們只觀察算法的處理結果,因此沒有進行圖像的完整顯示。

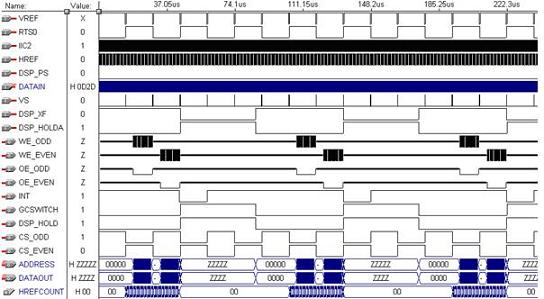

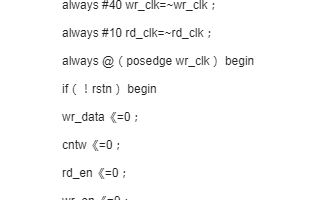

3.2 CPLD程序

CPLD接收的輸入信號有來自TMS320VC5509A的GPIO口的信號,來自TVP5150的場消隱信號VBLK、像素有效信號AVID、場同步信號VSYNC和奇偶場標志位信號FID。CPLD的輸出信號有提供給FIFO的寫使能信號![]() ,寫復位指針信號

,寫復位指針信號![]() 和讀復位指針信號

和讀復位指針信號![]() ,以及提供給TMS320VC5509A的中斷信號

,以及提供給TMS320VC5509A的中斷信號![]() 。

。

當VSYNC由高電平變為低電平時,輸出的是有效視頻信號,同時當VBLK為低電平、AVID為高電平時,TVP5150輸出有效視頻數據。

因為偶數場是從一行的中間開始掃描的,如果不設置FID信號,最后采集到的圖像可能是偶場信號,也可能是奇場信號,那么,在CCS中顯示的圖像有可能是完整的,也可能顯示的是左右顛倒的圖像,剛好錯開半行的圖像。所以,設置FID信號為0,采集奇場的信號。

CPLD將這些邏輯進行組合,使AL422B的寫使能![]() 有效,TVP5150輸出視頻數據到AL422B中。

有效,TVP5150輸出視頻數據到AL422B中。

因為要采集一幅150x 300的圖像,需要在CPLD中設置一個計數器對采集到的像素進行計數,由AL422B的寫時鐘WCK作為計數器的時鐘信號,當計數到45 000后觸發DSP外部中斷2,同時將計數器清零。

AL422B外擴在DSP的![]() 這個空間,當

這個空間,當![]() 和TMS320VC5509A的EMIF接口輸出使能信號

和TMS320VC5509A的EMIF接口輸出使能信號![]() 且為低電平時,通過CPLD的邏輯組合使能AL422B的輸出使能信號

且為低電平時,通過CPLD的邏輯組合使能AL422B的輸出使能信號![]() 。接著當TMS32 0VC5509A的EMIF接口讀使能信號

。接著當TMS32 0VC5509A的EMIF接口讀使能信號![]() 為低電平時,通過CPLD的邏輯組合使能AL422B的讀使能信號

為低電平時,通過CPLD的邏輯組合使能AL422B的讀使能信號![]() 。邏輯關系如下:

。邏輯關系如下:

![]()

4 實驗結果

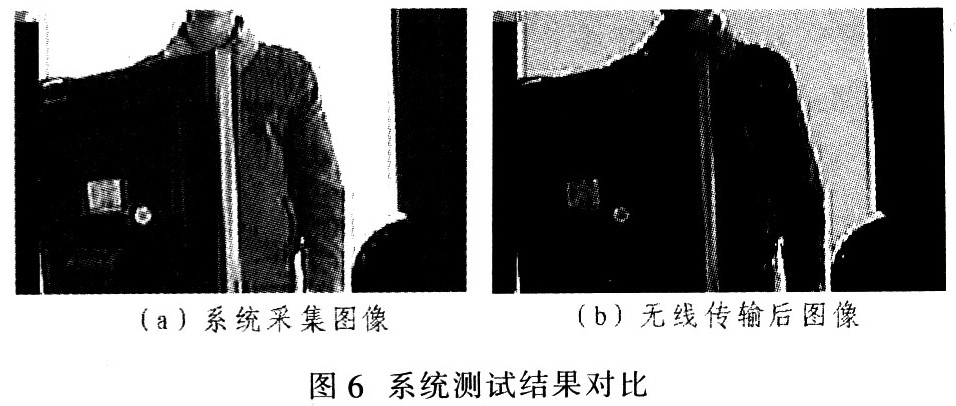

利用設計的系統進行實物圖像的采集,圖5(a)為采集的實驗室的辦公座椅場景,圖5(b)為使用邊緣檢測算法來對采集到的圖像進行的邊緣處理。

邊緣檢測能夠突出圖像的邊緣特征,使觀察者一目了然,并且蘊含了豐富的內在信息(方向、階躍性質和形狀等)。

結語

在DSP仿真軟件CCS中設置斷點,經過多次圖像采集處理的測試,均可以得到的完整的圖像信息。結果表明,使用異步FIFO作為TVP5150與DSP之間的數據傳輸連接器,能夠達到系統預設功能,并且可以穩定、高速地進行傳輸。

電子發燒友App

電子發燒友App

評論