大家好,又到了每日學習的時間了,今天我們來聊一聊基于FPGA的異步FIFO的實現。 一、FIFO簡介 FIFO是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,它與普通

2018-06-21 11:15:25 7148

7148

,它是7系列FPGA新設計的IO專用FIFO,主要用于IOLOGIC(例如ISERDES、IDDR、OSERDES或ODDR)邏輯功能的擴展。 FPGA的每個BANK有4個IN_FIFO和4個

2020-11-29 10:08:00 3670

3670

FIFO (先入先出, First In First Out )存儲器,在 FPGA 和數字 IC 設計中非常常用。 根據接入的時鐘信號,可以分為同步 FIFO 和異步 FIFO 。

2023-06-27 10:24:37 3136

3136

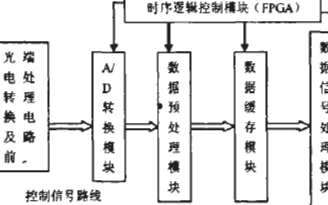

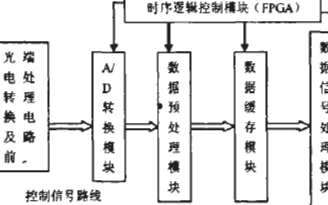

要求高的場合。本文采用FPGA+DSP構建光纖傳感信號采集處理系統.主要由ATD轉換芯片、FPGA、FIFO、DSP及其外圍電路組成,系統結構框圖如圖1所示。

2020-10-23 10:50:04 2735

2735

專家你好我的現在的硬件為6455接V5FPGA,FIFO接emif的ce5,進行數據傳輸。fifo寬度為32bit,用for循環讀取數據沒有問題,但是用EDMA發現數據不對,源數據位

2018-08-07 07:56:26

求助高手,利用FPGA產生的數據,能否通過NI的各類數據獲取系統,比如以太網DAQ NI 9201測量系統之類的板卡,把數據傳輸到電腦上?

2016-09-25 14:38:57

。由于ADC采樣頻率為10 MHz,為和PC運行速度相匹配,在FPGA內部生成一個FIFO緩存器。A/D轉換器在FPGA的ADC接口控制電路控制下,把模擬信號轉換成數字信號,并將指定通道的采樣數據存入

2020-01-07 07:00:00

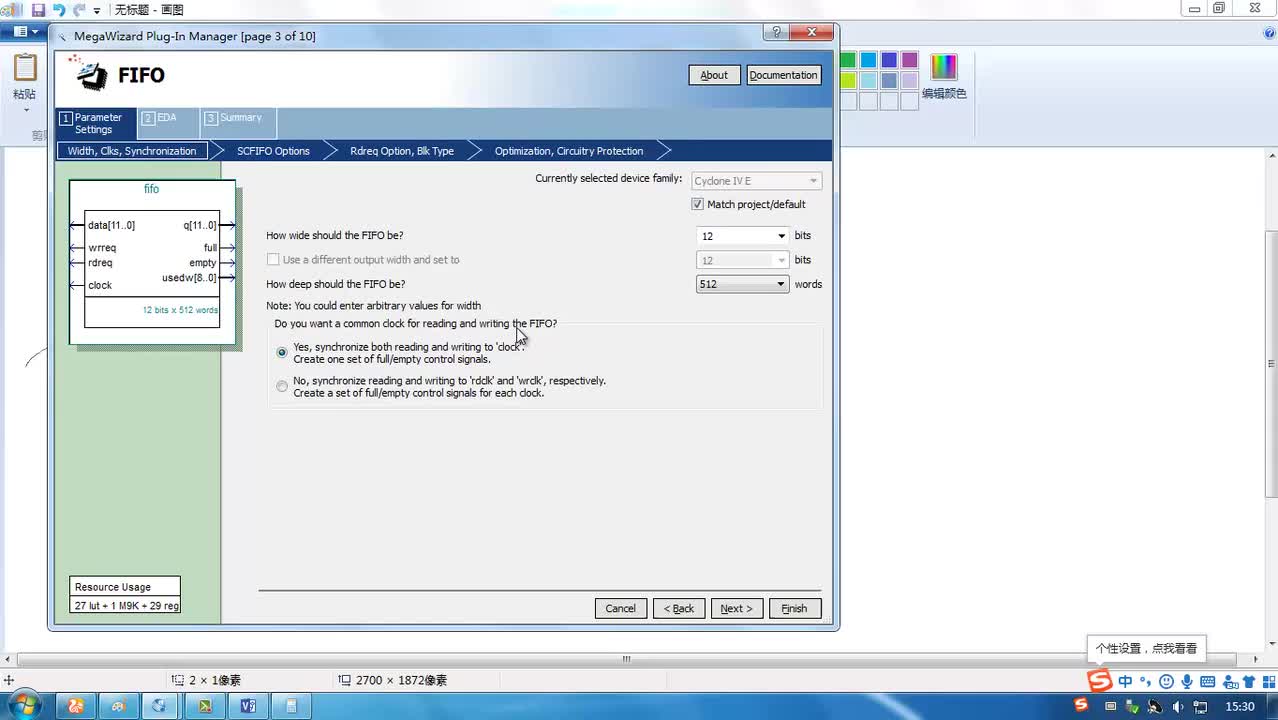

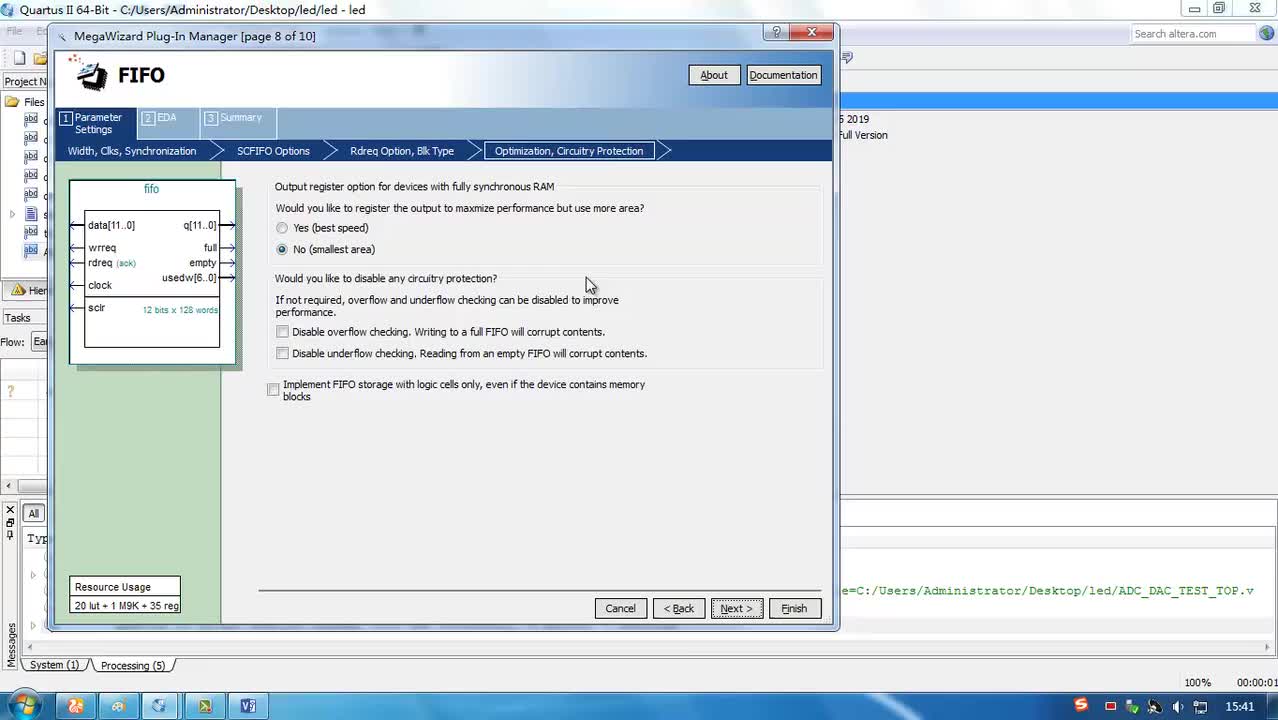

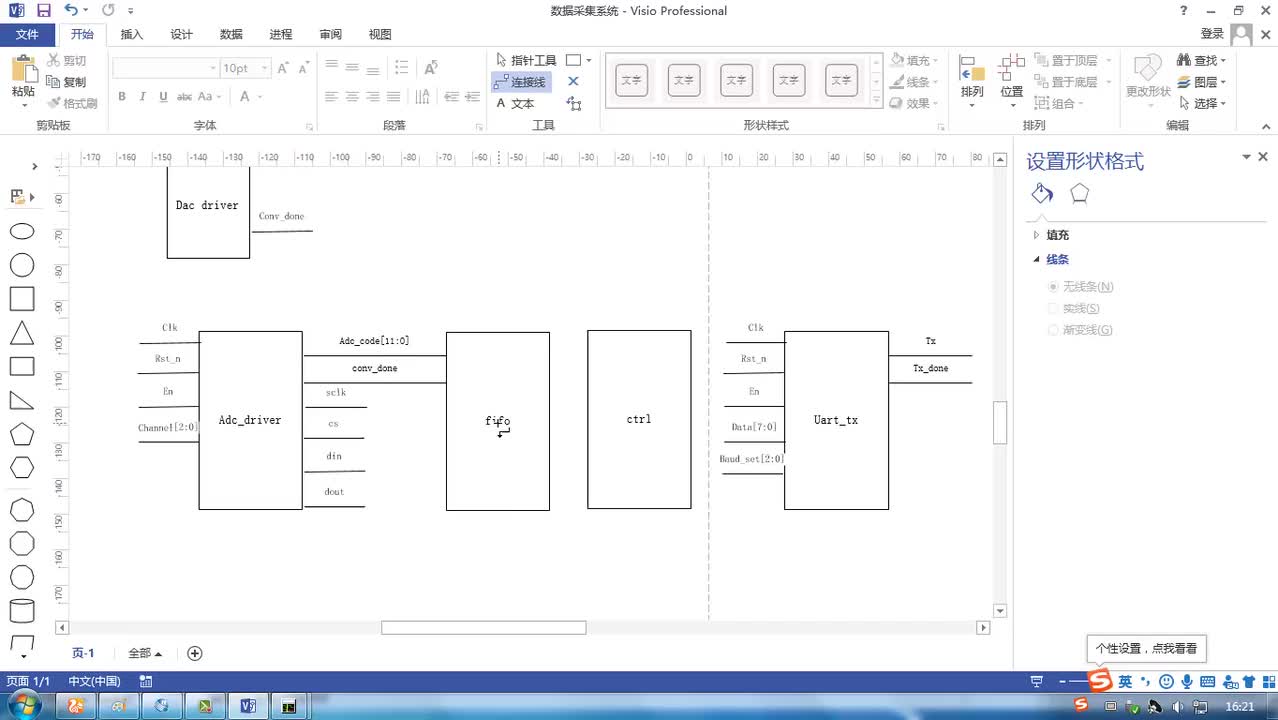

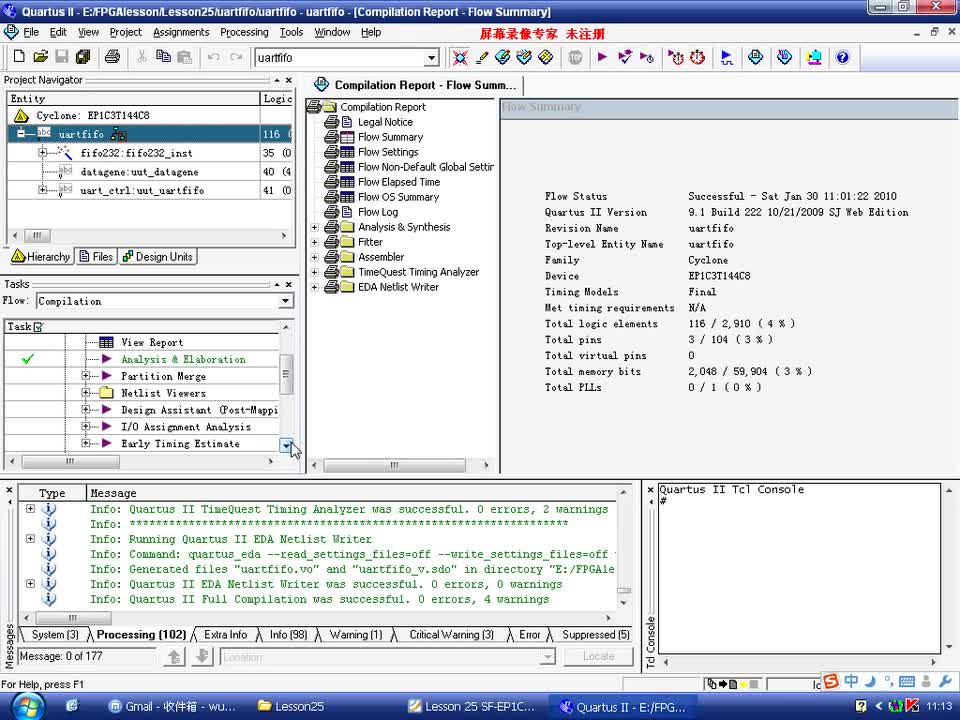

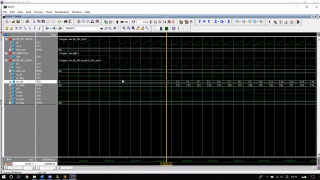

1 功能概述該工程實例內部系統功能框圖如圖所示。我們通過IP核例化一個FIFO,定時寫入數據,然后再讀出所有數據。通過ISE集成的在線邏輯分析儀chipscope,我們可以觀察FPGA片內FIFO

2019-04-08 09:34:42

)”。●“File name”即文件名,我們命名為“fifo_controller”。●“Location”下面輸入這個新建文件所存放的路徑,我們將其定位到工程路徑下的“ipcore_dir”文件夾

2019-04-08 01:10:09

我使用了AN65974的fifo部分 和an75779的uvc部分合成一套工程,工程文件見附件

現在的情況是開機后第一次獲取uvc流在卡頓一會之后大概率可以成功獲取圖像

但是之后獲取uvc流就無法

2024-02-27 06:08:36

FPGA內嵌雙口FIFO,實現高分辨力圖像數據的實時截取和降頻實時傳輸。該方法可以省去外部緩存SRAM操作,擴大圖像截取范圍,可廣泛運用于數字平板顯示系統。【關鍵詞】:DVI;;數字視頻;;FPGA

2010-04-23 11:18:05

EDMA要從FPGA的fifo模塊搬數,是不是把fifo和EDMA的時鐘都配置成同一個時鐘頻率100Mhz,然后EDMA的工作頻率也是100MHz。是不是這樣理解的?

2018-06-21 03:03:04

中斷請求)傳輸數據。NI LabVIEW FPGA中的FIFO緩沖區在LabVIEW項目瀏覽器中接受配置,并能借助板載內存或硬件邏輯獲得運行。 下圖顯示了如何經由項目瀏覽器,在板載塊存儲器中配置整數

2022-01-16 20:29:26

緩沖器,配置為THEAD0與USB端點0x82DMA通道之間的DMA通道。FPGA有2KB FIFO。當我們從PC讀取數據時,我們可以看到,一旦我們得到130kb(128kb+2kb的FPGA緩沖區

2019-10-16 11:10:21

另一組FTFO的寫時序,實現了信號不間斷的采樣和存儲。FPGA將一組數據處理完畢后,以中斷的方式通知SEP3203,處理器以DMA方式將運算后的結果存儲到片外的SDRAM中。由于數據寫滿FIFO的時間大于

2019-04-26 07:00:06

和存儲。FPGA將一組數據處理完畢后,以中斷的方式通知SEP3203,處理器以DMA方式將運算后的結果存儲到片外的SDRAM中。由于數據寫滿FIFO的時間大于FPGA處理數據的時間,所以整個系統實現了

2018-12-05 10:13:09

現在做一個項目,需要用FSMC和FPGA通信,但是FSMC接口沒有讀取FIFO的模式,希望大牛能給個思路,也可以一塊討論討論

2020-03-19 22:00:19

各位大神們,求助一下!!!我在使用dsp c6416芯片的QDMA時遇到搬數不對的問題。dsp通過emifa讀取fpga的fifo數據,fifo寫滿信號觸發dsp進入外部中斷6,開啟qdma傳輸數據

2020-04-14 09:55:47

各位大神們,求助一下!!!我在使用dsp c6416芯片的QDMA時遇到搬數不對的問題。dsp通過emifa讀取fpga的fifo數據,fifo寫滿信號觸發dsp進入外部中斷6,開啟qdma傳輸數據

2019-05-31 14:09:20

了邏輯分析儀的成本且便于攜帶。重點闡述硬件電路部分的設計。關鍵詞 邏輯分析儀;USB接口;FPGA;FIFO傳輸邏輯分析儀是數字設計驗證與調試過程中應用廣泛的工具,其能夠檢驗數字電路是否正常工作,并幫助

2019-06-18 07:56:45

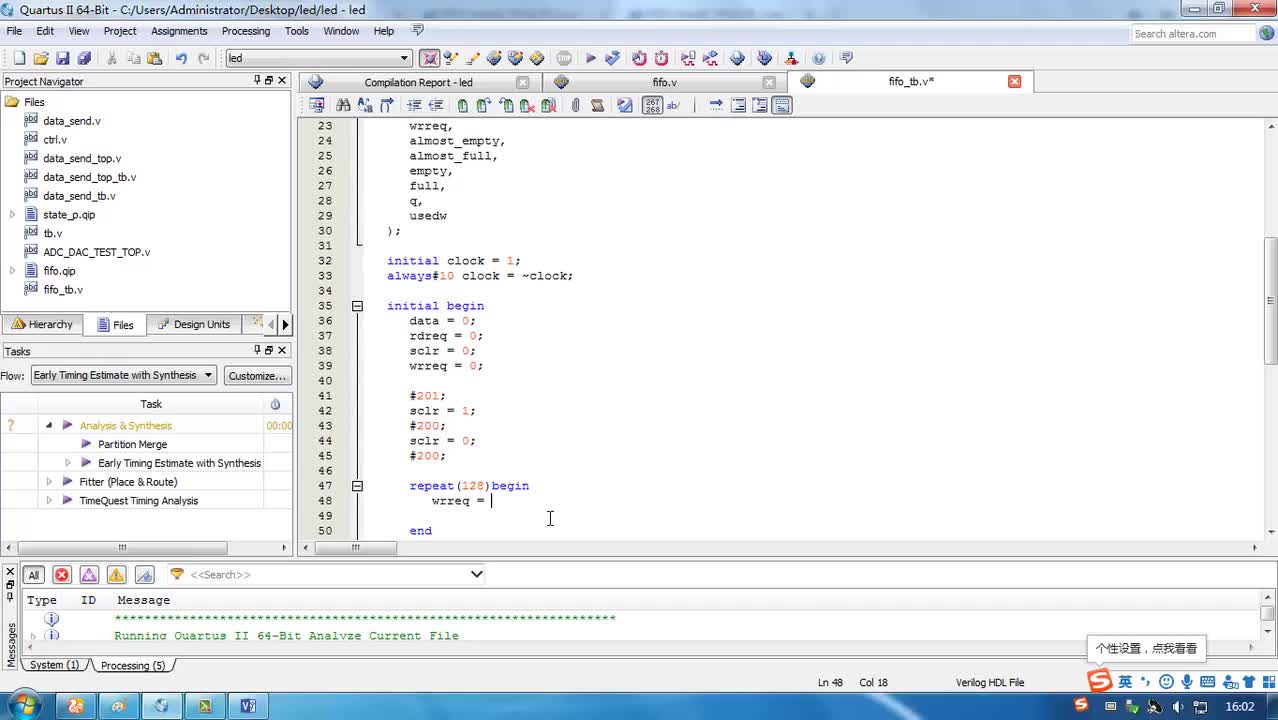

鏈接為“小墨同學”推出的零基礎FPGA“基于FIFO的串口發送機設計全流程”,https://bbs.elecfans.com/jishu_475408_1_1.html其中,有幾個部分不是很明白小墨同學的設計思路,希望大家拍磚(見圖片紅色框體部分)

2017-07-27 19:34:54

嗨,在Vivado 2015.4和ISE 14.7中實現的相同設計之間的資源利用率是否會有任何差異?考慮到這樣的事實,IP在Artix-7 FPGA中重新生成FIFO(版本9.3到13.1)時鐘向導

2019-04-24 09:12:08

現在在做一塊主控板,板子搭載DSP的28335芯片,利用FPGA的颶風2代EP2C144芯片橋接100腳STM32F103,起初規劃是用雙口RAM通信,后來改用FIFO通信,現在的情況是,DSP

2014-08-29 11:11:37

圖像壓縮之后的數據存入fifo,然后經過nrf2401發送。。但是由于圖片尺寸比較大,導致fifo深度不夠,受限于FPGA芯片尺寸的限制,fifo深度不能再選大了。。。求指導

2015-05-22 14:34:48

本文屬于本人原創,和大家一起學習FPGA,交流FPGA,希望大家多多支持。來源:至芯科技昭哥帶你學FPGA之FPGA_100天之旅_FIFO設計今天內容為基于FPGA的FIFO設計,詳細內容看以下

2017-09-26 09:34:31

求教! 我使用6713DSP的EDMA通過EMIF同步模式(SDRAM)讀取外接的FPGA的FIFO,請問讀取速度怎么確定?與EMIF的時鐘有什么關系呢?EDMA搬運數據的速度怎么確定呢?

2018-08-01 07:51:14

采用PCI總線流水式高速數據采集系統設計摘要:目前基于PCI總線的高速數據采集系統,大多采用高速A/D,CPLD或FPGA,FIFO或雙端口RAM以及通用PCI接口來設計,其通用性、靈活性差,不能

2009-10-30 15:09:49

目前基于PCI總線的高速數據采集系統,大多采用高速A/D,CPLD或FPGA,FIFO或雙端口RAM以及通用PCI接口來設計,其通用性、靈活性差,不能很好地發揮PCI總線的性能。針對這些不足,在分析

2009-03-16 18:02:05 10

10 首先介紹異步FIFO 的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法; 在傳統設計的基礎上提出一種新穎的電路結構并對其進行綜合仿真和FPGA 實現。

2009-04-16 09:25:29 46

46 介紹了PCI 9054 接口芯片的性能及數據傳輸特點,提出了一種基于PCI 9054 外擴異步FIFO(先進先出)的FPGA(現場可編程門陣列)實現方法。由于PCI 9054 內部FIFO存儲器主要用于數據

2010-01-06 15:20:10 44

44 本文主要研究了用FPGA 芯片內部的EBRSRAM 來實現異步FIFO 設計方案,重點闡述了異步FIFO 的標志信號——空/滿狀態的設計思路,并且用VHDL 語言實現,最后進行了仿真驗證。

2010-01-13 17:11:58 40

40 介紹了異步FIFO在Camera Link接口中的應用,將Camera Link接口中的幀有效信號FVAL和行有效信號LVAL引入到異步FIFO的設計中。分析了FPGA中設計異步FIFO的難點,解決了異步FIFO設計中存在的兩

2010-07-28 16:08:06 32

32 設計工程師通常在FPGA上實現FIFO(先進先出寄存器)的時候,都會使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其針對性變差,某些情況下會變得不方便或者將增加硬

2010-10-27 15:40:30 38

38 摘要:首先介紹異步FIFO的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法;在傳統設計的基礎上提出一種新穎的電路結構并對其進行

2009-06-20 12:46:50 4131

4131

FPGA設計的高速FIFO電路技術

本文主要介紹高速FIFO電路在數據采集系統中的應用,相關電路主要有高速A/D轉換器、FPGA、SDRAM存儲器等。圖1為本方案的結構框圖。在大容量

2010-05-27 09:58:59 2978

2978

本文采用VHDL描述語言,充分利用Xilinx公司Spartan II FPGA的系統資源,設計實現了一種非對稱同步FIFO,它不僅提供數據緩沖,而且能進行數據總線寬度的轉換。

2011-01-13 11:33:43 2240

2240 為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設定不當帶來的數據不連續問題,結合LabVIEWFPGA的編程特點和DMA FIFO的工作原理,提出了一種設定 FIFO 深度的方法。對FIFO不同深度的實驗表明,采

2011-09-26 13:45:17 7987

7987

文中給出了異步FIFO的實現代碼和FPGA與DSP的硬件連接電路。經驗證,利用異步FIFO的方法,在FPGA與DSP通信中的應用,具有傳輸速度快、穩定可靠、實現方便的優點。

2011-12-12 14:28:22 51

51 為實現目標識別與跟蹤的應用目的 ,在基于 TMS320DM642 的 FIFO 基礎上擴展存儲空間 ,提出一種基于

FPGA實現 SDRAM 控制器的方法。分析所用 SDRAM 的特點和工作原理

2015-10-29 14:05:57 2

2 異步FIFO結構及FPGA設計,解決亞穩態的問題

2015-11-10 15:21:37 4

4 異步FIFO在FPGA與DSP通信中的運用

2016-05-19 11:17:11 0

0 基于異步FIFO在FPGA與DSP通信中的運用

2017-10-19 10:30:56 10

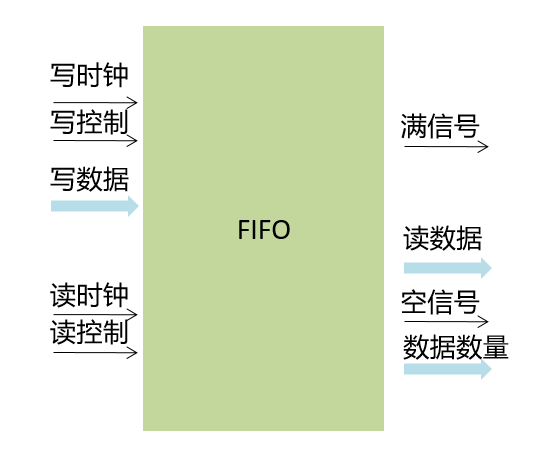

10 摘要 利用異步FIFO實現FPGA與DSP進行數據通信的方案。FPGA在寫時鐘的控制下將數據寫入FIFO,再與DSP進行握手后,DSP通過EMIFA接口將數據讀入。文中給出了異步FIFO的實現

2017-10-30 11:48:44 3

3 本文將講述如何通過項目瀏覽器窗口管理FPGA應用的組件,包括FPGA VI和主VI、FPGA終端、終端范圍的選項(例如,FPGA I/O、FPGA FIFO和FPGA終端時鐘)。下列示意圖顯示了由

2017-11-18 01:44:01 702

702

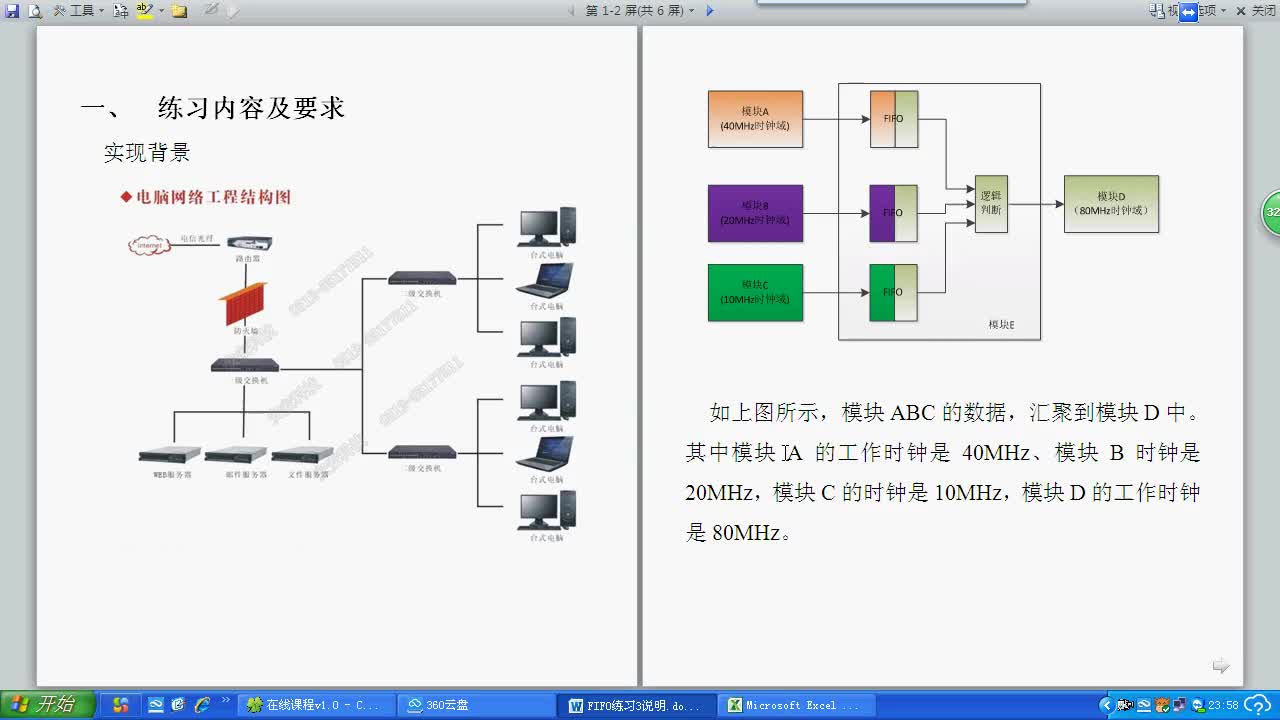

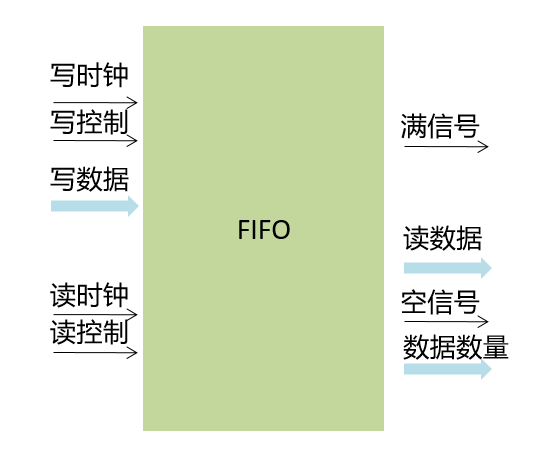

在現代電路設計中,一個系統往往包含了多個時鐘,如何在異步時鐘間傳遞數據成為一個很重要的問題,而使用異步FIFO可以有效地解決這個問題。異步FIFO是一種在電子系統中得到廣泛應用的器件,文中介紹了一種基于FPGA的異步FIFO設計方法。使用這種方法可以設計出高速、高可靠的異步FIFO。

2018-07-17 08:33:00 8860

8860

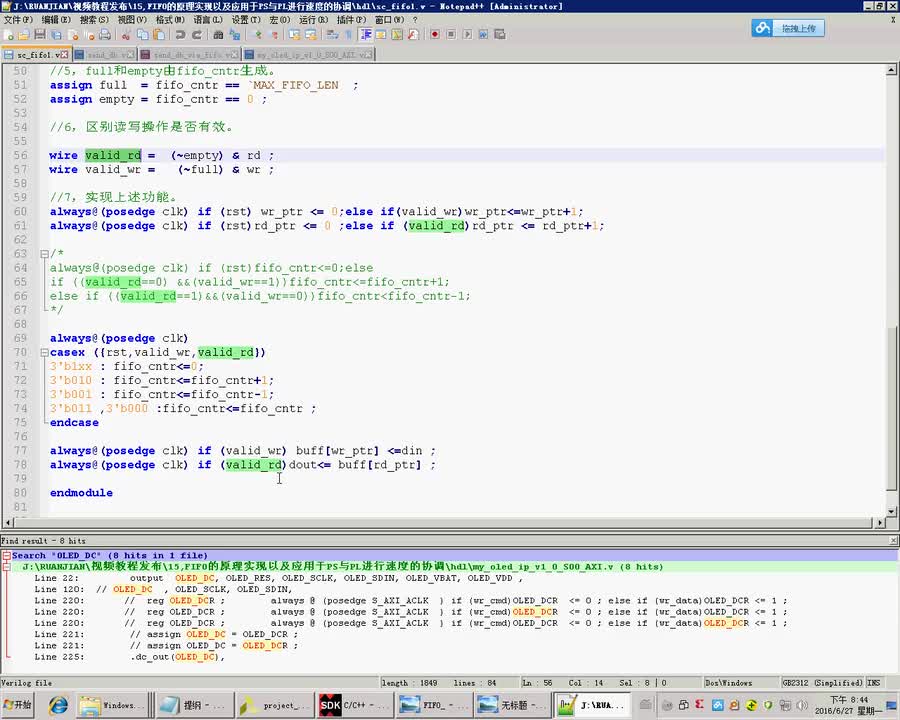

FIFO隊列有兩個位置指示指針。一個是寫指針,指向隊列的第一個存儲單元。一個讀指針,指向隊列的最后一個存儲單元。當有寫命令的時候,數據寫入寫指針指向的存儲單元,然后指針加一。當有讀命令的時候,讀指針

2018-06-29 08:51:00 16042

16042 設計工程師通常在FPGA上實現FIFO(先進先出寄存器)的時候,都會使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其針對性變差,某些情況下會變得不方便或者將增加硬件成本。此時,需要進行自行

2018-11-28 08:10:00 8891

8891

關鍵詞:FPGA , FIFO 記得在上幾篇博客中,有幾名網友提出要加進去錯誤分析這一部分,那我們就從今天這篇文章開始加進去我在消化這段代碼的過程中遇到的迷惑,與大家分享。 今天要寫的是一段

2018-09-14 07:56:01 752

752 為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設定不當帶來的數據不連續問題,結合LabVIEWFPGA的編程特點和DMA FIFO的工作原理,提出了一種設定FIFO深度的方法。對FIFO

2019-01-04 14:25:07 5203

5203

FIFO隊列具有處理簡單,開銷小的優點。但FIFO不區分報文類型,采用盡力而為的轉發模式,使對時間敏感的實時應用(如VoIP)的延遲得不到保證,關鍵業務的帶寬也不能得到保證。

2019-11-29 07:10:00 2159

2159 根據FIFO工作的時鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時鐘和寫時鐘為同一個時鐘。在時鐘沿來臨時同時發生讀寫操作。異步FIFO是指讀寫時鐘不一致,讀寫時鐘是互相獨立的。

2019-11-29 07:08:00 2265

2265 FIFO隊列不對報文進行分類,當報文進入接口的速度大于接口能發送的速度時,FIFO按報文到達接口的先后順序讓報文進入隊列,同時,FIFO在隊列的出口讓報文按進隊的順序出隊,先進的報文將先出隊,后進的報文將后出隊。

2019-11-29 07:04:00 5109

5109 FPGA電路FIFO設計的源代碼

2020-07-08 17:34:37 16

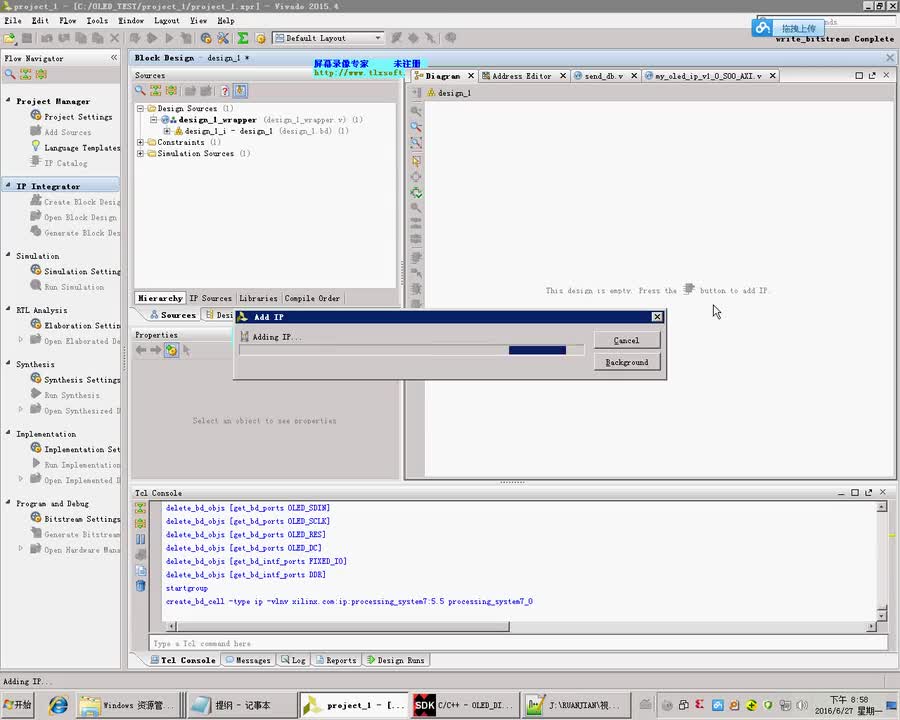

16 FIFO是FPGA應用當中非常重要的模塊,廣泛用于數據的緩存,跨時鐘域數據處理等。學好FIFO是FPGA的關鍵,靈活運用好FIFO是一個FPGA工程師必備的技能。本章主要介紹利用XILINX提供的FIFO IP進行讀寫測試。

2022-02-08 17:08:32 4442

4442

FIFO是FPGA應用當中非常重要的模塊,廣泛用于數據的緩存,跨時鐘域數據處理等。學好FIFO是FPGA的關鍵,靈活運用好FIFO是一個FPGA工程師必備的技能。本章主要介紹利用XILINX提供的FIFO IP進行讀寫測試。

2021-02-02 06:24:38 11

11 FIFO是FPGA處理跨時鐘和數據緩存的必要IP,可以這么說,只要是任意一個成熟的FPGA涉及,一定會涉及到FIFO。但是我在使用異步FIFO的時候,碰見幾個大坑,這里總結如下,避免后來者入坑。

2021-03-12 06:01:34 12

12 一:fifo是什么 FIFO的完整英文拼寫為FirstIn First Out,即先進先出。FPGA或者ASIC中使用到的FIFO一般指的是對數據的存儲具有先進先出特性的一個存儲器,常被用于數據

2021-03-12 16:30:48 4047

4047

FIFO是在FPGA設計中使用的非常頻繁,也是影響FPGA設計代碼穩定性以及效率等得關鍵因素。在數據連續讀取時,為了能不間斷的讀出數據而又不導致FIFO為空后還錯誤的讀出數據。可以將FIFO

2021-09-09 11:15:00 7773

7773 在FPGA中對圖像的一行數據進行緩存時,可以采用FIFO這一結構,如上圖所示,新一行圖像數據流入到FIFO1中,FIFO1中會對圖像數據進行緩存,當FIFO1中緩存有一行圖像數據時,在下一行圖像數據來臨的時候,將FIFO1中緩存的圖像數據讀出,并傳遞給下一個FIFO

2022-05-10 09:59:29 4734

4734 無論何時,在復雜的 FPGA 設計過程中,都不可避免地需要在模塊之間發送數據,實現這一點的常用的是 FIFO。

2022-09-20 09:10:27 3532

3532 在FPGA的設計中的,內部的FIFO和RAM是兩種非常常見的存儲單元

2023-07-11 17:23:33 2143

2143 FIFO(First In First Out)是一種先進先出的存儲結構,經常被用來在FPGA設計中進行數據緩存或者匹配傳輸速率。

2023-08-07 15:39:50 2190

2190 上文XILINX FPGA IP之FIFO對XILINX FIFO Generator IP的特性和內部處理流程進行了簡要的說明,本文通過實際例子對該IP的使用進行進一步的說明。本例子例化一個讀數

2023-09-07 18:31:35 3352

3352

FIFO作為FPGA崗位求職過程中最常被問到的基礎知識點,也是項目中最常被使用到的IP,其意義是非常重要的。本文基于對FIFO Generator的Xilinx官方手冊的閱讀與總結,匯總主要知識點

2024-11-12 10:46:11 2718

2718

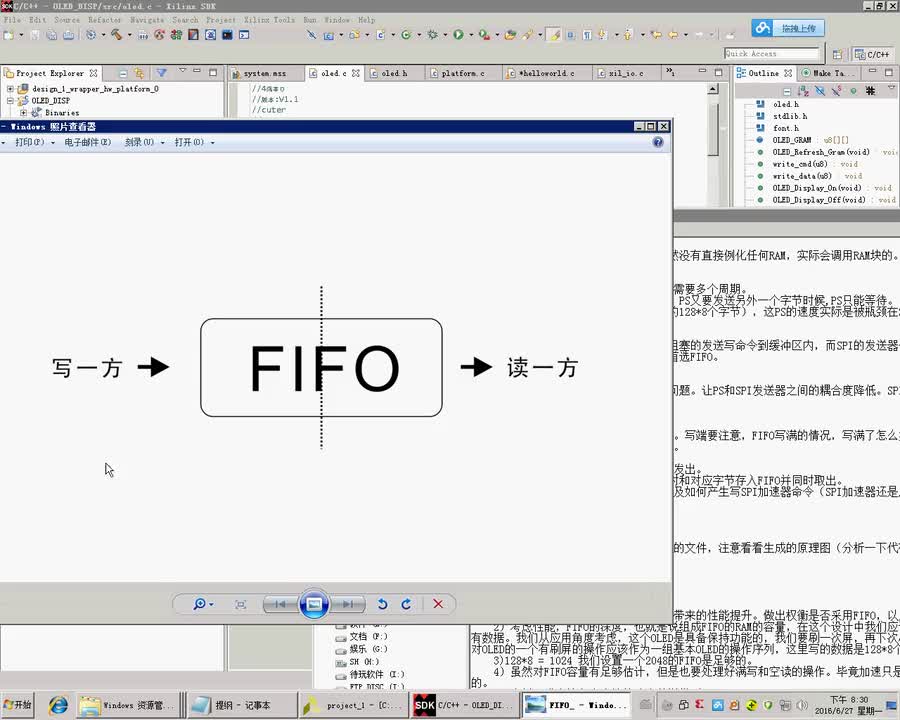

FIFO(First in First out)為先進先出隊列,具有存儲功能,可用于不同時鐘域間傳輸數據以及不同的數據寬度進行數據匹配。如其名稱,數據傳輸為單向,從一側進入,再從另一側出來,出來的順序和進入的順序相同。

2025-04-09 09:55:57 1292

1292

電子發燒友App

電子發燒友App

評論