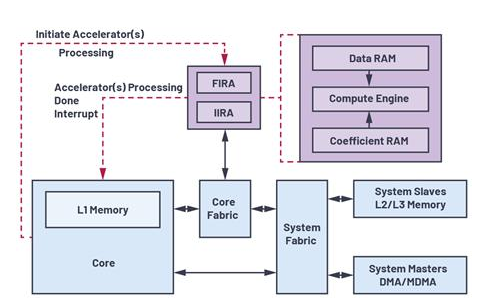

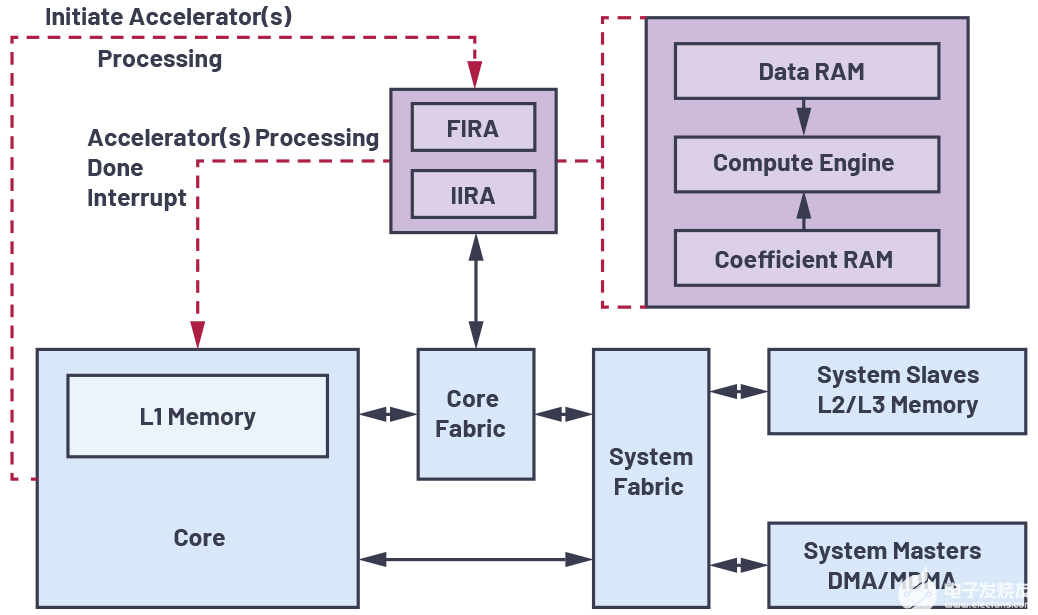

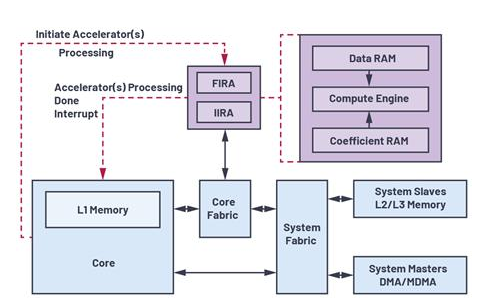

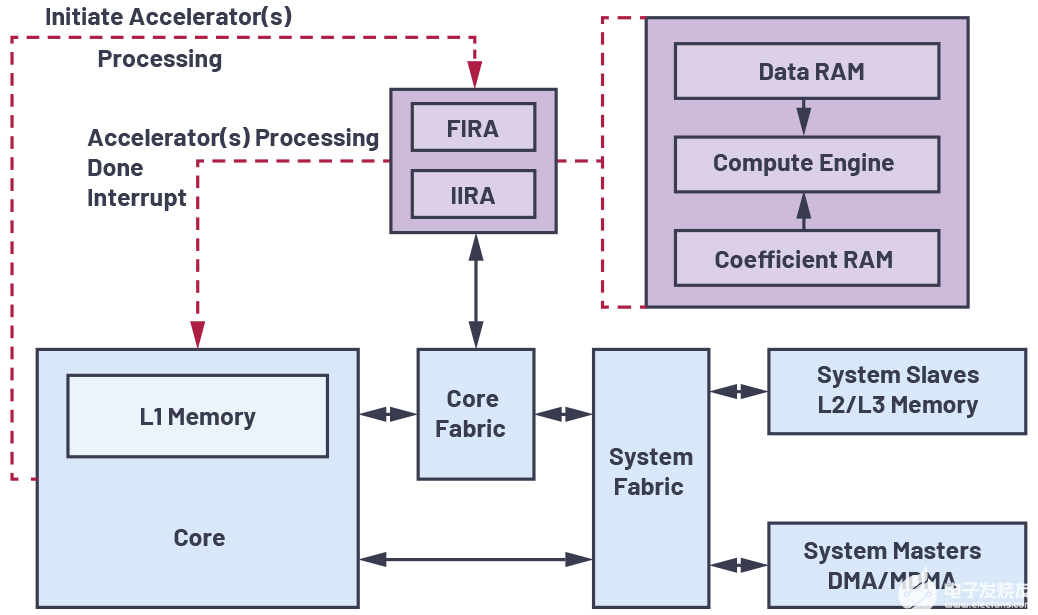

我們看到如何利用不同的加速器使用模型實(shí)現(xiàn)所需的MIPS和處理目標(biāo),從而將大量內(nèi)核MIPS轉(zhuǎn)移到ADSP-2156x處理器上的FIRA和IIRA加速器。

2020-06-22 14:42:33 2257

2257

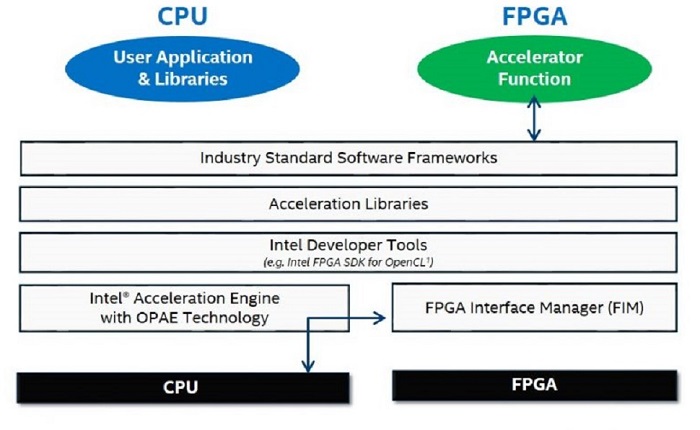

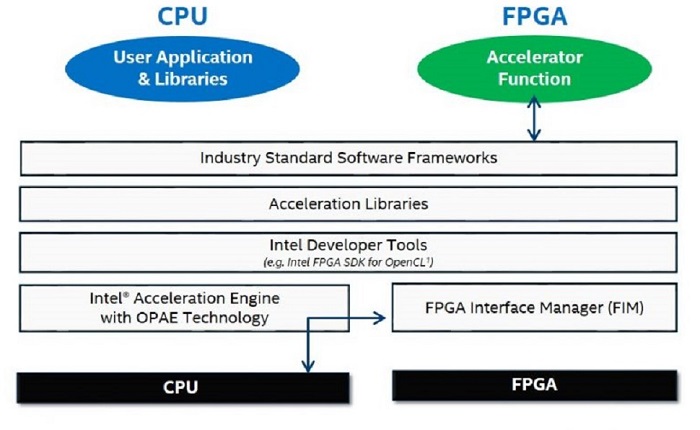

電子發(fā)燒友網(wǎng)核心提示: Altera的嵌入式軟處理器系列使您能夠充分利用FPGA內(nèi)在的并行優(yōu)勢,實(shí)現(xiàn)高級(jí)系統(tǒng)性能。多個(gè)處理器可以同時(shí)執(zhí)行代碼,而硬件加速器也能夠同時(shí)卸載大計(jì)算量

2012-10-17 13:41:19 15140

15140 提高處理器主頻可以提高處理器的性能,但是到一定程度就不能再提高了,我們需要通過雙核,或者多核來提高處理器的性能。

2024-01-24 09:59:00 4162

4162

第五代 OCTEON系列處理器支持4到 36個(gè)Arm v8內(nèi)核,并配備一系列功能強(qiáng)大的硬件加速器,用于網(wǎng)絡(luò)、安全和無線基礎(chǔ)設(shè)施應(yīng)用。

2020-03-06 08:50:02 3969

3969 硬件加速模塊需要四個(gè)時(shí)鐘,分別為clk_l , clk_r , clk_c , clk_n 。

clk_l : 整個(gè)硬件加速模塊為了最大化的節(jié)約時(shí)間成本而采用了類似處理器的流水線設(shè)計(jì),具體上將每一層

2025-10-23 07:28:15

Hi,HenryLj.mo請(qǐng)問下在Sigma 300里面使用硬件加速器slew,slew mode為RC type時(shí),對(duì)應(yīng)的time constant 與數(shù)據(jù)從當(dāng)前值到目標(biāo)值得時(shí)間有什么關(guān)系,或者說不同的time constant的值有什么用? Thanks,Jack

2019-01-29 06:55:13

的7nmFinFET工藝,其架構(gòu)采用革命性的新型2D片上網(wǎng)絡(luò)(NoC),獨(dú)創(chuàng)的機(jī)器學(xué)習(xí)處理器矩陣(MLP),并利用高帶寬GDDR6控制器、400G以太網(wǎng)和PCIExpressGen5接口,在保障ASIC級(jí)別性能的同時(shí)

2021-07-07 08:00:00

H.264解碼器中CABAC硬件加速器怎么實(shí)現(xiàn)?

2021-06-07 06:48:58

英特爾媒體加速器參考軟件是用于數(shù)字標(biāo)志、交互式白板(IWBs)和亭位使用模型的參考媒體播放器應(yīng)用軟件,它利用固定功能硬件加速來提高媒體流速、改進(jìn)工作量平衡和資源利用,以及定制的圖形處理股(GPU)管道解決方案。該用戶指南將介紹和解釋如何使用英特爾媒體加速器視窗參考軟件。

2023-08-04 07:07:34

增加了微處理器的復(fù)雜性,帶來了諸如材料、功耗、光刻、電磁兼容性等一系列問題。因此處理器設(shè)計(jì)人員開始尋找新的途徑來提高處理器的性能。Intel公司于2002年底推出了超線程技術(shù),通過共享處理器的執(zhí)行資源,提高CPU的利用率,讓處理單元獲得更高的吞吐量。

2019-09-19 06:59:47

利用MCU處理類似FPU運(yùn)算內(nèi)容,會(huì)因?yàn)镸CU本身的運(yùn)算架構(gòu)限制,讓 運(yùn)算結(jié)果得出時(shí)間會(huì)相對(duì)拉長,而在導(dǎo)入硬件加速器處理浮點(diǎn)運(yùn)算時(shí),因?yàn)?b class="flag-6" style="color: red">硬件呼叫或是資料傳遞就能透過硬件算出數(shù)據(jù),MCU本身耗在浮點(diǎn)運(yùn)算

2016-10-14 17:17:54

v3.0,它的上限是 MCUBoot v1.8.1。 當(dāng)前版本基于 MCUBoot v1.9.1,似乎支持加密硬件加速。 有什么最簡單的方法可以更新我的舊版引導(dǎo)加載器,以便運(yùn)行 MCUBoot v1.9.1?

順便說一下,我的 PSoC 是 CY8C624ABZI-S2D44,它帶有硬件加速器。

2024-05-29 08:17:06

你好, 目前,我想運(yùn)用6670中bcp硬件加速器,在調(diào)試Bcp_testProject例程中,在test_lte_dl.c文件中pend hRxSem信號(hào)量時(shí)halt住,發(fā)現(xiàn)中斷服務(wù)程序未能響應(yīng)

2018-12-25 11:27:45

目前我使用NI的機(jī)箱采集數(shù)據(jù),labview做軟件平臺(tái)生成一個(gè)系統(tǒng)。想要達(dá)到實(shí)時(shí)性效果。能否給NI或labview采用硬件加速,提高處理速的呢?如何做呢?有什么資料可以參考?

2018-09-29 09:34:24

實(shí)現(xiàn)了一種I/O流水線接口,該接口具有I/O連接加速器的典型性能。FPGA/PowerPC/APU接口FPGA允許硬件設(shè)計(jì)工程師利用單芯片上的處理器、解碼邏輯、外設(shè)和協(xié)處理器實(shí)現(xiàn)一個(gè)完整的計(jì)算系統(tǒng)

2015-02-02 14:18:19

代碼加速和代碼轉(zhuǎn)換到硬件協(xié)處理器的方法如何采用FPGA協(xié)處理器實(shí)現(xiàn)算法加速?

2021-04-13 06:39:25

)。而且,在我的測試中,我發(fā)現(xiàn)關(guān)閉“硬件加速器”允許屏幕在旋轉(zhuǎn)時(shí)正確地繪制,但是這使得系統(tǒng)使用起來非常緩慢和痛苦(壞的用戶體驗(yàn))。謝謝任何幫助。

2020-04-03 10:56:36

請(qǐng)問下在Sigma 300里面使用硬件加速器slew,slew mode為RC type時(shí),對(duì)應(yīng)的time constant 與數(shù)據(jù)從當(dāng)前值到目標(biāo)值得時(shí)間有什么關(guān)系,或者說不同的time constant的值有什么用?

謝謝,

中 J Jj

2023-11-29 07:25:43

和 DSP5509 相匹配的接口電路,確保圖像數(shù)據(jù)的正確傳輸和顯示。常見的接口有 RGB、LVDS 等。

五、Sobel 算子計(jì)算模塊設(shè)計(jì)

硬件加速:可以考慮使用硬件加速器來加速 Sobel 算子的計(jì)算。例如,可以

2024-09-25 15:25:29

飛思卡爾聯(lián)合Khronos Group 推出了一款集成了OpenVG硬件加速器的汽車多媒體嵌入式微處理器i.MX35,成為全球首款集成OpenVG硬件加速器的汽車多媒體微處理器,i.MX35卓越的多媒體性能將車載多媒體推向一個(gè)新的高度,確定了Freescale在汽車電子行業(yè)不可撼動(dòng)的引領(lǐng)地位。

2019-11-01 07:59:24

加速器適配不同的arm系統(tǒng),這對(duì)軟硬件接口和驅(qū)動(dòng)提出了非常大的挑戰(zhàn),因?yàn)榻裉斓腶rm產(chǎn)品非常豐富,從低功耗的微處理器,主流的移動(dòng)平臺(tái),到高端的服務(wù)器,高性能計(jì)算處理器都有相應(yīng)產(chǎn)品。對(duì)于一個(gè)加速器團(tuán)隊(duì)來說

2022-07-29 15:38:43

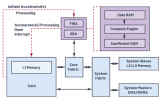

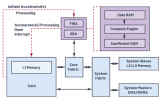

CMSDK工具設(shè)計(jì)了AHB總線系統(tǒng),在基于單級(jí)AHB總線的框架下,通過APB橋接器和AXI橋接器擴(kuò)展了APB總線和AXI總線,進(jìn)而構(gòu)成該SoC高效的總線框架。通過搭建高效的總線系統(tǒng)將M3處理器與硬件加速器

2022-08-26 15:23:33

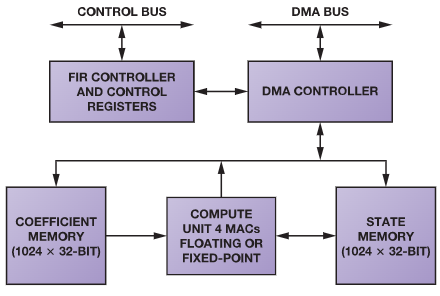

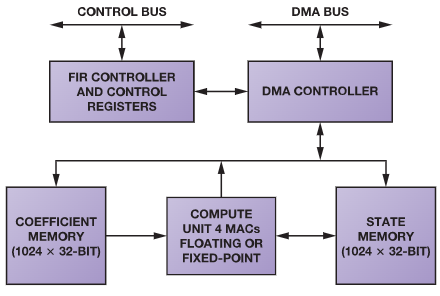

上的片內(nèi)FIR和IIR硬件加速器也分別稱為FIRA和IIRA,我們可以利用這些硬件加速器來分擔(dān)FIR和IIR處理任務(wù),讓內(nèi)核去執(zhí)行其他處理任務(wù)。在本文中,我們將借助不同的使用模型以及實(shí)時(shí)測試示例來探討如何在實(shí)踐中利用這些加速器。

2020-12-28 06:26:54

的電力線通信(PLC)。 為此,TI C2000?MCU集成了多達(dá)四個(gè)集成的片上硬件加速器,可在許多實(shí)時(shí)應(yīng)用中顯著提高設(shè)備性能。四個(gè)加速器包括浮點(diǎn)單元(FPU)、實(shí)時(shí)協(xié)處理器控制律加速器(CLA

2019-07-23 04:45:03

嵌入式處理器所實(shí)現(xiàn)的網(wǎng)絡(luò)訪問。雖然目前嵌入式處理器已經(jīng)能夠完美地應(yīng)用于多種工業(yè)應(yīng)用,但Sitara AM57x處理器所提供的視頻與圖形加速器使其在人機(jī)界面(HMI)的應(yīng)用中大發(fā)異彩。ARM

2018-09-04 10:07:50

之前總結(jié)了一些常用硬件加速方法

1)面積換速度:也就是串轉(zhuǎn)并運(yùn)算,可以多個(gè)模塊同時(shí)計(jì)算;

2)時(shí)間換空間:時(shí)序收斂下通過頻率提高性能,雖然面積可能稍微加大點(diǎn);

3)流水線操作:流水線以面積換性能,以

2025-10-29 06:20:33

--高級(jí)--疑難解答中的硬件加速是否完全開啟。 3、如果是游戲不能玩了。顯示屬性--設(shè)置--高級(jí)--適配器--列出所有模式,將該項(xiàng)的數(shù)據(jù)設(shè)置的比平時(shí)稍低一些。也就是降低刷新率及分辨率。 3d硬件加速器

2019-08-21 09:04:31

與硬件加速器和 I/O模塊的一致性能夠提高數(shù)據(jù)吞吐量以及簡化軟件開發(fā)過程。加速器一致性端口(ACP)結(jié)合芯片的NoC路由功能,可滿足硬件加速和I/O性能的最新應(yīng)用需求。ECC(錯(cuò)誤校驗(yàn)碼)保護(hù)功能可防止

2018-12-12 10:20:29

嗨!我已經(jīng)創(chuàng)建了一個(gè)硬件加速器(在vhdl中)并且合成成功完成。但是,當(dāng)我使用創(chuàng)建和導(dǎo)入外圍設(shè)備向?qū)r(shí),它向我顯示我的包在庫中不可用,盡管它是。我能做什么 ???L'enfer,c'est l

2019-02-27 14:15:31

,但是矩陣的計(jì)算量非常大。基于以上分析,我們決定在GNN Core加速器設(shè)計(jì)中用兩種不同的硬件結(jié)構(gòu)來處理聚合操作與合并操作,功能框圖如下圖所示:圖7: GNN Core功能框圖聚合器

2020-10-20 09:48:39

作為汽車半導(dǎo)體的領(lǐng)軍企業(yè)飛思卡爾聯(lián)合Khronos Group 推出了一款集成了OpenVG硬件加速器的汽車多媒體嵌入式微處理器i.MX35,成為全球首款集成OpenVG硬件加速器的汽車多媒體

2019-07-22 08:11:07

英特爾媒體加速器參考軟件是用于數(shù)字標(biāo)志、交互式白板(IWBs)和亭位使用模型的參考媒體播放器應(yīng)用軟件,它利用固定功能硬件加速來提高媒體流速、改進(jìn)工作量平衡和資源利用,以及定制的圖形處理股(GPU)管道解決方案。該用戶指南將介紹和解釋如何為Linux* 使用英特爾媒體加速器參考軟件。

2023-08-04 06:34:54

本帖最后由 一只耳朵怪 于 2018-6-19 14:25 編輯

在C6670中,因只有一個(gè)bcp硬件加速器,不同核所來數(shù)據(jù)怎樣同時(shí)運(yùn)行起來而不發(fā)生一個(gè)核經(jīng)常搶占BCP加速器,導(dǎo)致其它核數(shù)據(jù)

2018-06-19 00:42:40

處理架構(gòu)的關(guān)鍵結(jié)構(gòu)。這一引擎由一個(gè)處理器陣列加上可能存在的硬件加速器構(gòu)成。回答了下面這些問題,就等于完成了一個(gè)設(shè)計(jì)流程: 需要多少個(gè)處理器? 應(yīng)該如何安排這些處理器?&

2008-09-25 17:17:55

開發(fā)技術(shù)。分文將分享介紹硬件加速器與軟件結(jié)合的協(xié)同開發(fā)方式

軟硬件任務(wù)劃分

我們的硬件設(shè)計(jì)涉及到MFCC模塊。直接交由CPU的一次指令的五級(jí)流水線處理在麥克風(fēng)數(shù)據(jù)取入上的資源耗費(fèi)可以說是

2025-10-28 08:03:26

日前,德州儀器 (TI) 宣布推出采用控制律加速器 (CLA) 的新型 TMS320F2803x Piccolo 微處理器 (MCU),可促進(jìn)具有更高可靠性與效率的嵌入式控制應(yīng)用的開發(fā)。CLA

2019-07-26 06:21:46

問下ARM3的硬件加速器只能用verilog寫嗎?

2022-09-30 10:45:39

高級(jí)處理器特性能否提高編碼效率?

2021-04-26 06:41:08

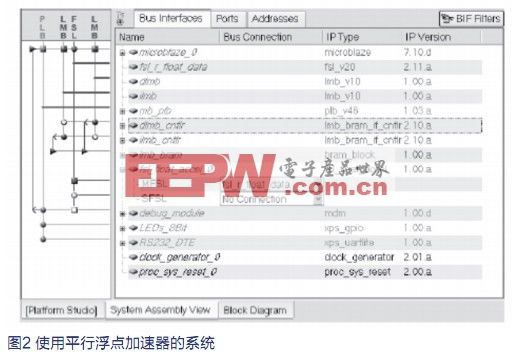

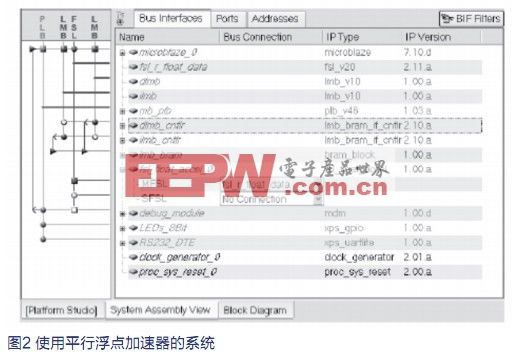

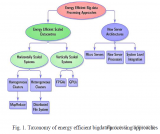

采用硬件加速發(fā)揮MicroBlaze處理能力

MicroBlaze處理器是賽靈思(Xilinx)在嵌入式開發(fā)套件 (EDK) 中提供的兩款32位內(nèi)核之一,是實(shí)現(xiàn)硬件加速的靈活工具。圖1是MicroBlaze的

2010-03-10 10:24:16 1525

1525

針對(duì)復(fù)雜算法中矩陣運(yùn)算量大, 計(jì)算復(fù)雜, 耗時(shí)多, 制約算法在線計(jì)算性能的問題, 從硬件實(shí)現(xiàn)角度, 研究基于FPGA/Nios-Ⅱ的矩陣運(yùn)算硬件加速器設(shè)計(jì), 實(shí)現(xiàn)矩陣并行計(jì)算。首先根據(jù)矩陣運(yùn)算

2011-12-06 17:30:41 89

89 電子發(fā)燒友網(wǎng)核心提示: 獲獎(jiǎng)的Nios II 嵌入式處理器C語言至硬件(C2H)加速編譯器將對(duì)時(shí)間要求較高的ANSI C函數(shù)轉(zhuǎn)換為FPGA中的硬件加速器,從而提高了性能。 特性: (1)ANSI/ISO C 代碼按鍵

2012-10-17 14:29:34 2394

2394

一種在線網(wǎng)絡(luò)安全處理器SoC的IPSec加速器_郭金星

2017-01-07 22:23:13 1

1 。 本文所聚焦的技術(shù)手段是讓一個(gè)已有的UVM驗(yàn)證平臺(tái)通過改變需求去執(zhí)行硬件加速。如果這些點(diǎn)在UVM環(huán)境開發(fā)過程中被考慮到,那么之后將環(huán)境遷移到硬件加速器作為一個(gè)性能選項(xiàng)將是一件較容易的事情。本文所提議的建議將會(huì)使你的UVM驗(yàn)證

2017-09-15 17:08:11 14

14 如果修改軟件不能實(shí)現(xiàn)所需速度,那么你可能順理成章的想到在你的設(shè)計(jì)中加入硬件加速模塊。 作 有很多種算法可對(duì)單精度浮點(diǎn)數(shù)字的正弦值進(jìn)行計(jì)算,但添加硬件加速器是功能最為強(qiáng)大的方法之一。之所以得出這一結(jié)論

2017-11-24 18:38:33 2745

2745

,因此使用硬件壓縮加速器來替換軟件壓縮。Hadoop運(yùn)行在Java虛擬機(jī)上,無法直接調(diào)用底層I/O硬件壓縮加速器。通過實(shí)現(xiàn)Hadoop壓縮器/解壓縮器類和設(shè)計(jì)C++動(dòng)態(tài)鏈接庫來解決從Hadoop系統(tǒng)中獲得壓縮數(shù)據(jù)和將數(shù)據(jù)流向I/O硬件壓縮加速器兩個(gè)關(guān)鍵技術(shù),從而將I/O硬件壓縮加速

2017-11-27 10:49:05 0

0 驗(yàn)證、分析。相比非流水線硬件加速模型,流水線硬件加速模型能提高MD5運(yùn)算效率5倍,可用于網(wǎng)絡(luò)處理器等硬件加密引擎,有效提高網(wǎng)絡(luò)處理器等硬件設(shè)備的安全性和處理效率。

2018-01-12 16:45:07 0

0 很多人認(rèn)為硬件加速器無非是一種速度更快的仿真器而已。毫無疑問,由于硬件加速器使用物理硬件進(jìn)行仿真,使用硬件加速器驗(yàn)證復(fù)雜的集成電路和大型片上系統(tǒng)(SoC)能比軟件仿真器快若干數(shù)量級(jí)。與仿真用通用計(jì)算機(jī)相比,仿真用單一功能計(jì)算機(jī)能提供更高容量、更高效的系統(tǒng)。

2018-03-28 14:50:00 4536

4536

正確利用硬件加速器對(duì)邏輯仿真進(jìn)行加速是非常有效的。如果知道某項(xiàng)設(shè)計(jì)在仿真中的運(yùn)行速度(用每秒仿真了多少設(shè)計(jì)時(shí)鐘來衡量),你就能很容易地估計(jì)出該設(shè)計(jì)的原始性能。舉個(gè)例子,我們假設(shè)仿真器以每秒1000個(gè)

2018-03-05 10:13:13 3

3 學(xué)芯片技術(shù)的機(jī)會(huì)來了!斯坦福大學(xué)2018秋季學(xué)期推出《機(jī)器學(xué)習(xí)硬件加速器》課程,深入介紹機(jī)器學(xué)習(xí)系統(tǒng)中設(shè)計(jì)訓(xùn)練和推理加速器的架構(gòu)技術(shù)。課程涵蓋經(jīng)典的ML算法,用于ML模型推理和訓(xùn)練的加速器設(shè)計(jì)等,超多專業(yè)材料和PPT,是本領(lǐng)域不可多得的專業(yè)課程。

2018-07-21 09:27:10 6889

6889 從很多方面來看,AI加速熱潮與1990年代末期和2000年代初的DSP淘金熱很類似;在那個(gè)時(shí)候,隨著有線和無線通信起飛,市場上紛紛推出高性能DSP協(xié)同處理器(co-processor)以因應(yīng)基帶處理的挑戰(zhàn)。與DSP協(xié)同處理器一樣,AI加速器的目標(biāo)是找到最快速、最節(jié)能的方法來執(zhí)行所需的運(yùn)算任務(wù)。

2018-10-29 11:40:58 4953

4953 了解協(xié)處理的價(jià)值,Zynq-7000加速器一致性端口,使用協(xié)處理器加速器的方法以及協(xié)處理器設(shè)計(jì)實(shí)例的概述。

2018-11-30 06:15:00 4782

4782 本教程討論基于Xilinx FPGA的Memcached硬件加速器的技術(shù)細(xì)節(jié),該硬件加速器可為10G以太網(wǎng)端口提供線速M(fèi)emcached服務(wù)。

2018-11-27 06:41:00 4243

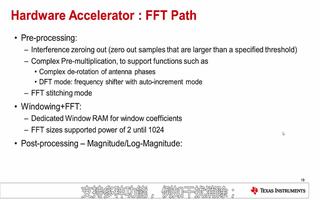

4243 2.6 mmWave波形傳感器簡介1443硬件加速器

2019-05-08 06:20:00 4155

4155

硬件加速仿真可以實(shí)現(xiàn)寄存器傳輸級(jí)(RTL)和現(xiàn)代SoC設(shè)計(jì)門級(jí)的最佳功耗分析。只有硬件加速仿真才有處理大量邏輯以及產(chǎn)生針對(duì)所有元素的切換活動(dòng)的獨(dú)有能力。

2019-10-11 17:54:29 5797

5797

隨著物聯(lián)網(wǎng)、云計(jì)算的發(fā)展和大數(shù)據(jù)時(shí)代來臨,移動(dòng)醫(yī)療、智能健康服務(wù)已離我們越來越近,今天如何加速傳統(tǒng)醫(yī)療健康設(shè)備向智能化轉(zhuǎn)型,如何有效利用移動(dòng)互聯(lián)網(wǎng)和云計(jì)算的力量,在大數(shù)據(jù)時(shí)代推出更加智慧的醫(yī)療和健康設(shè)備與服務(wù)?思其安科技攜手星云智能硬件加速器等合作聯(lián)盟伙伴,推出醫(yī)信智能健康云服務(wù)。

2019-09-27 10:41:22 5362

5362 硬件加速是指在計(jì)算機(jī)中通過把計(jì)算量非常大的工作分配給專門的硬件來處理以減輕中央處理器的工作量之技術(shù)。尤其是在圖像處理中這個(gè)技術(shù)經(jīng)常被使用。

2019-08-15 15:29:35 7913

7913

寄存器以啟動(dòng)加速器處理。一旦所有通道的配置完成,就會(huì)向內(nèi)核發(fā)送一個(gè)中斷,以便內(nèi)核將處理后的輸出用于后續(xù)操作。

2020-07-06 16:10:04 3701

3701

單片機(jī)微處理器-6500集成了硬件加速計(jì),使用硬件陀螺儀,運(yùn)動(dòng)和機(jī)載數(shù)字處理器?(DMP)在一個(gè)小,3毫米x3毫米x0.9毫米QFN包。6軸裝置是世界上第一個(gè)以1.8伏特運(yùn)行的運(yùn)動(dòng)傳感器,在全工況下

2020-11-17 14:13:29 23

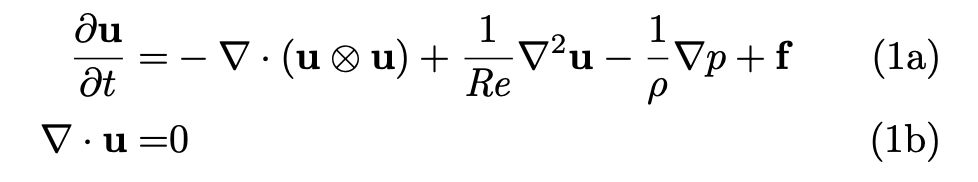

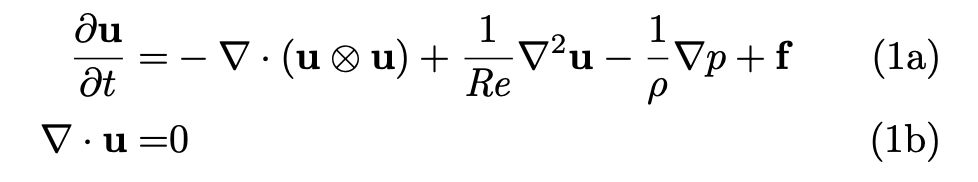

23 谷歌 AI 最近一項(xiàng)研究表明,利用機(jī)器學(xué)習(xí)和硬件加速器能夠改進(jìn)流體模擬,且不損害準(zhǔn)確率或泛化性能。 流體數(shù)值模擬對(duì)于建模多種物理現(xiàn)象而言非常重要,如天氣、氣候、空氣動(dòng)力學(xué)和等離子體物理學(xué)。流體可以用

2021-02-24 09:35:53 2667

2667

硬件加速器提升下一代SHARC處理器的性能

2021-04-23 13:06:32 6

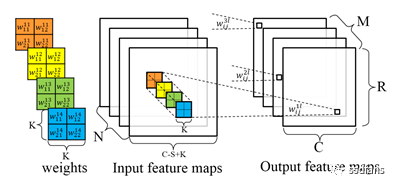

6 卷積計(jì)算的效率。基于軟硬件協(xié)同設(shè)計(jì)思想,構(gòu)建包含RISCⅤ處理器和卷積加速器的SoC系統(tǒng),RISC-V處理器基于開源的指令集標(biāo)準(zhǔn),可以根據(jù)具體的設(shè)計(jì)需求擴(kuò)展指令功能。將該SoC系統(tǒng)部署在 Xilinx ZCU102開發(fā)板上ISC-V處理器和卷積加速器分別工作在100M

2021-06-02 15:08:22 29

29 ?日前,中國硬件創(chuàng)新創(chuàng)客大賽組委會(huì)與中城智能硬件加速器正式達(dá)成戰(zhàn)略合作伙伴關(guān)系。 ? ? 中城智能硬件加速器天集社是2020年入選工信部中小企業(yè)服務(wù)平臺(tái)和國家級(jí)科技企業(yè)孵化器,鏈接全球硬件創(chuàng)新者建立

2021-07-15 15:18:02 3821

3821

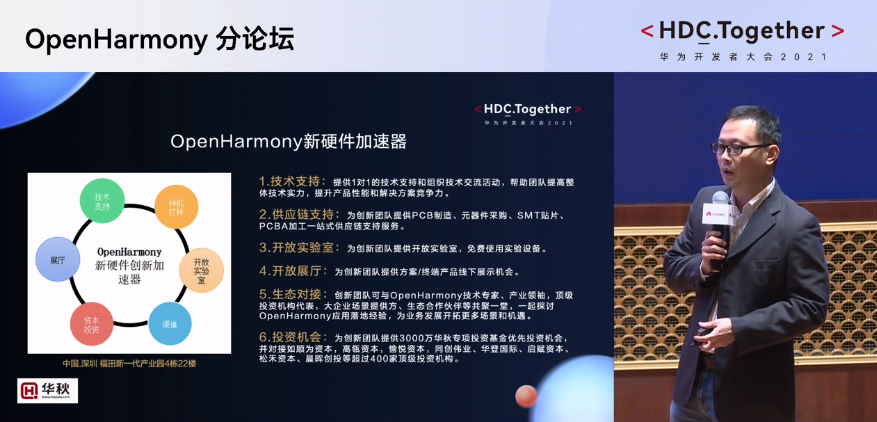

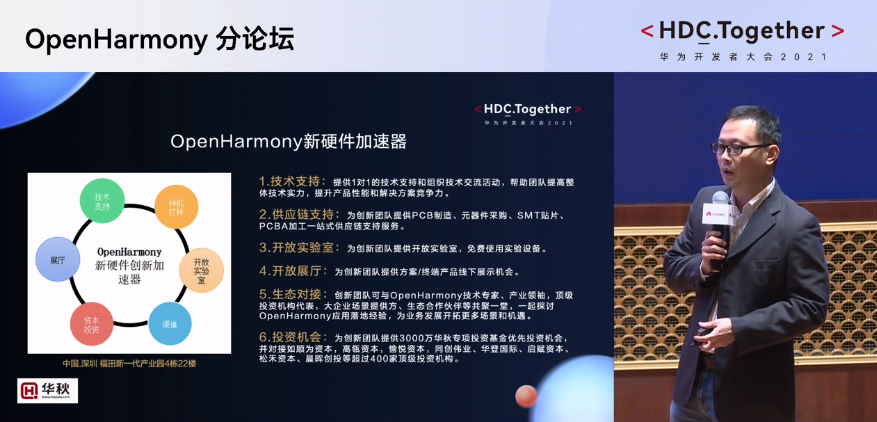

今天的2021華為開發(fā)者大會(huì)上,OpenHarmony分論壇上展示了華秋電子OpenHarmony新硬件加速器。 HDC分論壇-OpenHarmony 分論壇推薦鏈接:http://t.elecfans.com/live/1708.html 責(zé)任編輯:haq

2021-10-23 15:43:42 1582

1582

OpenHarmony 分論壇-華秋電子新硬件加速器 今天的華為開發(fā)者大會(huì)2021上,OpenHarmony分論壇上展示了華秋電子新硬件加速器 。 HDC分論壇-OpenHarmony 分論壇推薦鏈接:http://t.elecfans.com/live/1708.html 責(zé)任編輯:haq

2021-10-23 16:53:48 2152

2152

OpenHarmony Dev-Board-SIG專場:OpenHarmony 新硬件加速器

2021-12-28 15:12:30 1731

1731

AI加速器是一類專門的硬件加速器或計(jì)算機(jī)系統(tǒng)旨在加速人工智能的應(yīng)用,主要應(yīng)用于人工智能、人工神經(jīng)網(wǎng)絡(luò)、機(jī)器視覺和機(jī)器學(xué)習(xí)。

2022-02-06 12:47:00 5622

5622 的片內(nèi)FIR和IIR硬件加速器也分別稱為FIRA和IIRA,我們可以利用這些硬件加速器來分擔(dān)FIR和IIR處理任務(wù),讓內(nèi)核去執(zhí)行其他處理任務(wù)。在本文中,我們將借助不同的使用模型以及實(shí)時(shí)測試示例來探討如何在實(shí)踐中利用這些加速器。

2022-05-05 14:08:16 2198

2198 本項(xiàng)目采用Cortex-M3軟核做控制部分,大規(guī)模專用硬件加速器做濾波跟蹤計(jì)算和智能目標(biāo)檢測部分,視頻輸入輸出通過HDMI直接進(jìn)入硬件加速器,繞過軟核實(shí)現(xiàn)更快的數(shù)據(jù)處理速度。

2022-05-16 10:04:26 2202

2202 自 2021 年 10 月起,NVIDIA 和 Open Robotics 開始合作并推出了兩項(xiàng)重要的改動(dòng),現(xiàn)已發(fā)布在Humble ROS 2版本中,以提高提供硬件加速器的計(jì)算平臺(tái)的性能。

2022-07-07 09:45:07 4380

4380 加速器控制:語音識(shí)別加速器控制部分首先在軟件實(shí)現(xiàn)了NICE自定義指令的函數(shù),通過實(shí)現(xiàn)加速器開關(guān)函數(shù)以及全局變量的控制,實(shí)現(xiàn)軟件控制加速器的開啟和關(guān)閉。此外,通過接入外部的按鍵中斷實(shí)現(xiàn)按鍵控制語音識(shí)別的開啟和關(guān)閉。

2022-07-25 09:15:31 5476

5476 在開發(fā)一個(gè)加速程序的之前,有一個(gè)很重要的步驟:正確設(shè)計(jì)程序架構(gòu)。開發(fā)人員需要明確軟件應(yīng)用程序中哪一部分是需要硬件加速的,并且它多少的并行量,以保證硬件加速器件(FPGA)能完美發(fā)揮其作用。本文將分為5個(gè)步驟來介紹

2022-08-02 10:33:07 986

986

數(shù)據(jù)中心對(duì)高性能硬件加速器的需求不斷增長,這些芯片在深度學(xué)習(xí)、圖像分類、對(duì)象檢測和識(shí)別以及自然語言處理等應(yīng)用中采用人工智能技術(shù)。這些基于硬件加速器的芯片正在迅速取代傳統(tǒng)的 CPU 和 GPU,因?yàn)樗鼈兡軌蛞愿偷墓母斓?b class="flag-6" style="color: red">處理 AI 任務(wù)。

2022-08-17 15:18:11 2113

2113

當(dāng) AI 設(shè)計(jì)人員將硬件加速器整合到用于訓(xùn)練和推理應(yīng)用的定制芯片中時(shí),應(yīng)考慮以下四個(gè)因素

2022-08-19 11:35:55 2386

2386

處理器上的片上FIR和IIR硬件加速器(也稱為FIRA和IIRA)可用于卸載FIR和IIR處理任務(wù),從而騰出內(nèi)核用于其他處理。在本文中,我們將討論如何借助經(jīng)過測試的實(shí)時(shí)示例說明的不同使用模型在實(shí)踐中使用這些加速器。

2022-12-20 11:39:25 2286

2286

借助硬件加速器開發(fā)您的設(shè)計(jì)

2023-01-03 09:45:15 1450

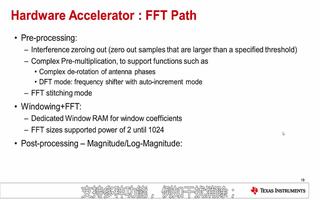

1450 SHARC ADSP-2146x處理器集成了硬件加速器,可實(shí)現(xiàn)三種廣泛使用的信號(hào)處理操作:FIR(有限脈沖響應(yīng))、IIR(無限脈沖響應(yīng))和FFT(快速傅里葉變換)。加速器卸載了核心處理器,并有可能使處理器的計(jì)算吞吐量增加一倍以上。本文以加速器在下一代音頻系統(tǒng)中的應(yīng)用為例。?

2023-03-03 14:46:51 2194

2194

了解DPU數(shù)據(jù)處理器的基礎(chǔ)知識(shí):它們是什么、它們做什么、誰在制造它們以及誰在采用它們。然后決定您的數(shù)據(jù)中心是否有朝一日會(huì)使用。

數(shù)據(jù)處理器是針對(duì)數(shù)據(jù)處理和以數(shù)據(jù)為中心的計(jì)算的硬件加速器。 不同于CPU和GPU及其他硬件加速器,DPU具有更高的并行度和MIMD架構(gòu)。

2023-04-19 15:38:23 3774

3774 作為全球首款支持第四代Intel至強(qiáng)可擴(kuò)展處理器平臺(tái)的高端存儲(chǔ),這種先發(fā)優(yōu)勢是非常明顯的,PCIe5.0、DDR5、CXL、QAT硬件加速器等新硬件形態(tài)的支持,都會(huì)大大提高MS9000G3的性能,同時(shí)降低單位功耗,實(shí)現(xiàn)綠色節(jié)能的效果。

2023-04-27 11:46:24 3489

3489

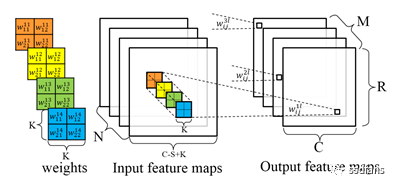

本文重點(diǎn)解釋如何使用硬件轉(zhuǎn)換卷積神經(jīng)網(wǎng)絡(luò)(CNN),并特別介紹使用帶CNN硬件加速器的人工智能(AI)微控制器在物聯(lián)網(wǎng)(IoT)邊緣實(shí)現(xiàn)人工智能應(yīng)用所帶來的好處。 AI應(yīng)用通常需要消耗大量能源,并以

2023-05-16 01:05:03 1905

1905 因?yàn)镃NN的特有計(jì)算模式,通用處理器對(duì)于CNN實(shí)現(xiàn)效率并不高,不能滿足性能要求。 因此,近來已經(jīng)提出了基于FPGA,GPU甚至ASIC設(shè)計(jì)的各種加速器來提高CNN設(shè)計(jì)的性能。

2023-06-14 16:03:43 3135

3135

電子發(fā)燒友網(wǎng)站提供《Alveo卡的區(qū)塊鏈硬件加速器解決方案.pdf》資料免費(fèi)下載

2023-09-15 14:42:57 0

0 思想是利用專門的硬件資源,如GPU或?qū)S玫慕獯a芯片,來分擔(dān)原本由CPU承擔(dān)的解碼任務(wù)。這種方式不僅可以大幅提高解碼速度,還能降低CPU的負(fù)載,從而實(shí)現(xiàn)更流暢的播放效果。 硬件加速的優(yōu)勢 高效性能 :硬件解碼器通常具有更高的解碼速度

2024-02-21 14:40:48 2009

2009

標(biāo)簽: Net FPGA , XC7K325T板卡 , XC7K325T處理板 , 軟件無線電處理平臺(tái) , 圖形圖像硬件加速器

2024-03-04 14:14:06 1610

1610

神經(jīng)網(wǎng)絡(luò)加速器是一種專門設(shè)計(jì)用于提高神經(jīng)網(wǎng)絡(luò)計(jì)算效率的硬件設(shè)備。隨著深度學(xué)習(xí)技術(shù)的快速發(fā)展和廣泛應(yīng)用,神經(jīng)網(wǎng)絡(luò)模型的復(fù)雜度和計(jì)算量急劇增加,對(duì)計(jì)算性能的要求也越來越高。傳統(tǒng)的通用處理器(CPU

2024-07-11 10:40:59 1728

1728 電子發(fā)燒友網(wǎng)站提供《適用于數(shù)據(jù)中心應(yīng)用中的硬件加速器的直流/直流轉(zhuǎn)換器解決方案.pdf》資料免費(fèi)下載

2024-08-26 09:38:15 0

0 ? 再來看一篇FPGA的綜述,我們都知道微軟包括國內(nèi)的云廠商其實(shí)都在數(shù)據(jù)中心的服務(wù)器中部署了FPGA,所以這篇論文就以數(shù)據(jù)中心的視角,來看下FPGA這個(gè)硬件加速器。 還是一樣,想要論文原文的可以私信

2025-01-14 10:29:31 1303

1303

產(chǎn)品實(shí)拍圖 利用硬件加速提升通信協(xié)議安全性,核心是通過 專用硬件模塊或可編程硬件 ,承接軟件層面難以高效處理的安全關(guān)鍵操作(如加密解密、認(rèn)證、密鑰管理等),在提升性能的同時(shí),通過硬件級(jí)隔離、防篡改等

2025-08-27 09:59:06 783

783

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論