獨熱碼在狀態(tài)機里面使用比價廣泛,這一塊有些人愛用,有些人嫌煩,有時候可以用用格雷碼跳轉,不過格雷碼只支持那種一步到底的,中間有分支就不好做了,所以后來還是回到了獨熱碼的正道上。

2018-05-05 10:15:19 8675

8675 其中采用循環(huán)二進制編碼的絕對式編碼器,其輸出信號是一種數字排序,不是權重碼,每一位沒有確定的大小,不能直接進行比較大小和算術運算,也不能直接轉換成其他信號,要經過一次碼變換,變成自然二進制碼。

2020-09-23 16:23:04 7515

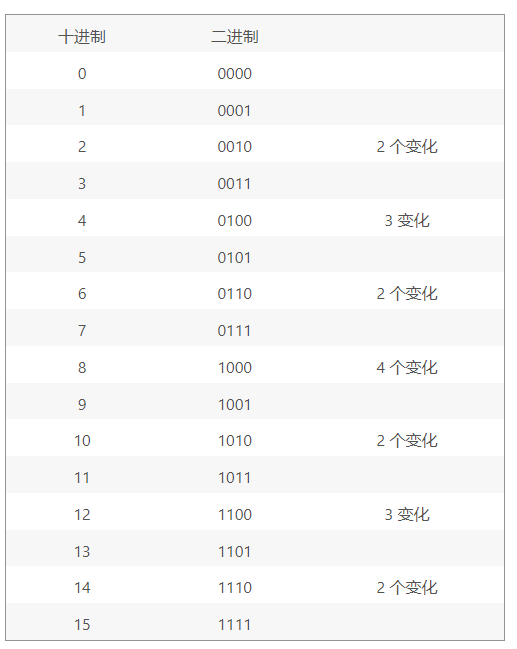

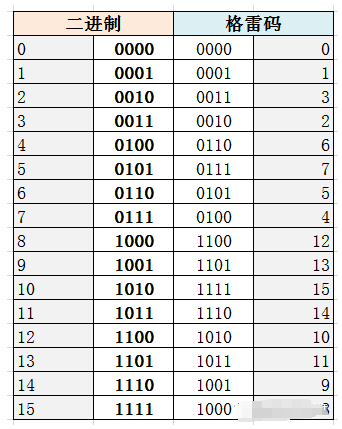

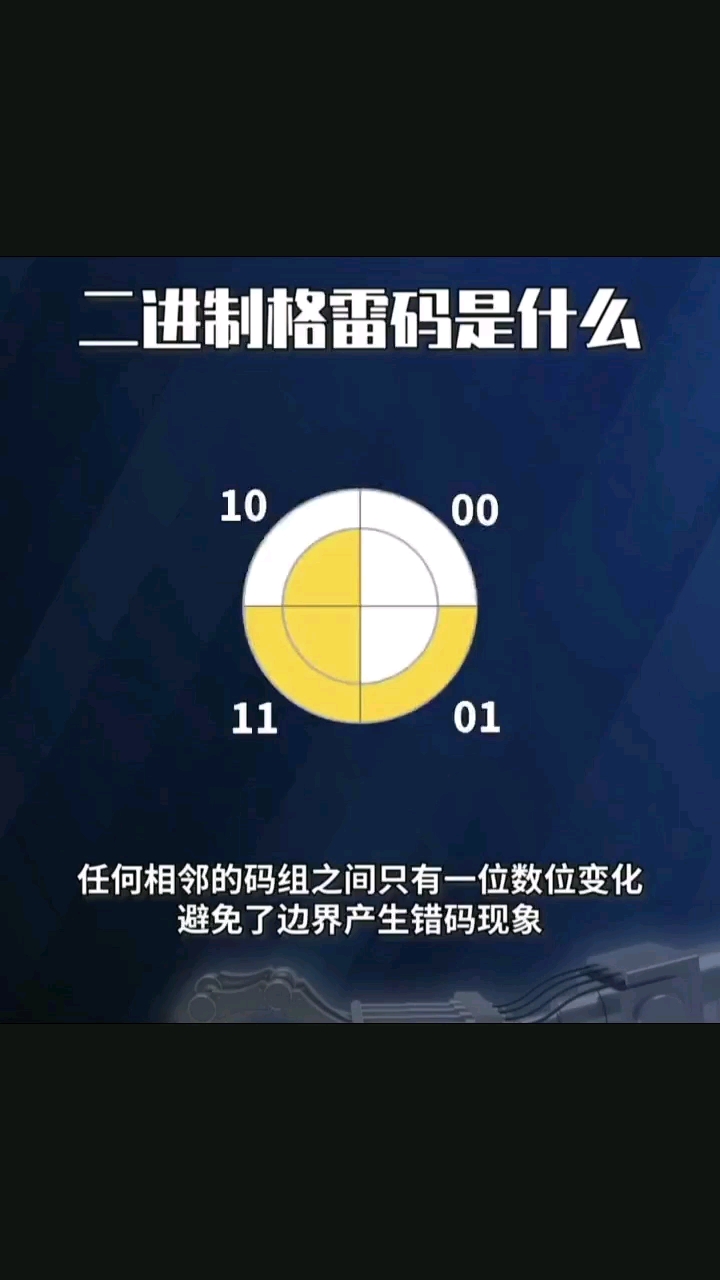

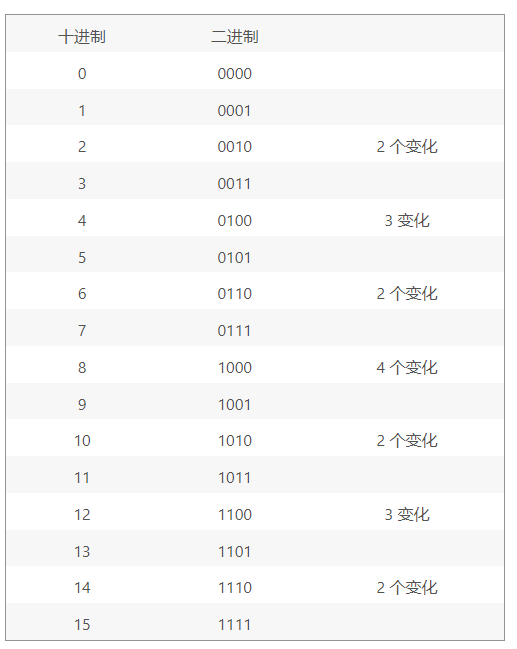

7515 格雷碼:任意相鄰的兩位之間只相差一位!在正常工作電路中,輸入時常會變化,若輸入突然變化多個位,很容易導致輸出不穩(wěn)定,有毛刺。若把輸入編為格雷碼,會有不錯的效果。

2022-12-27 16:46:11 6398

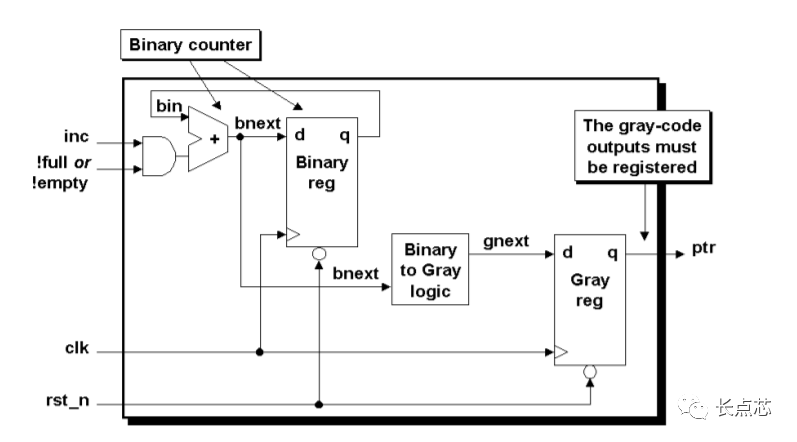

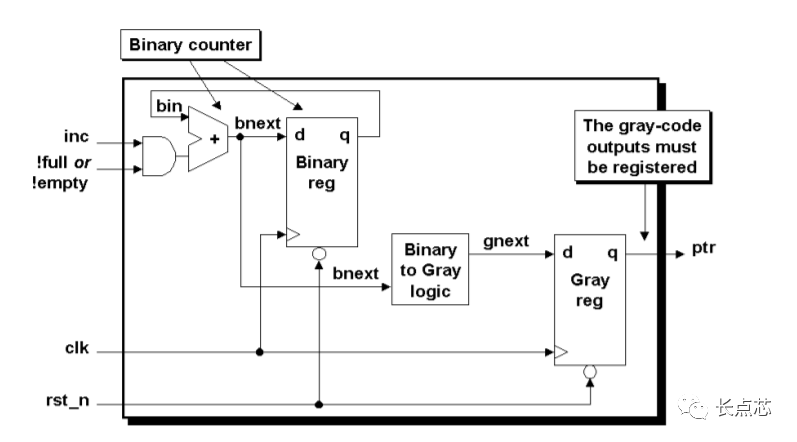

6398 相鄰的格雷碼只有1bit的差異,因此格雷碼常常用于異步fifo設計中,保證afifo的讀地址(或寫地址)被寫時鐘(或讀時鐘)采樣時最多只有1bit發(fā)生跳變。

2023-11-01 17:37:31 2498

2498

目前,針對數字電路研究的主要目標都是為了提高電路的運算速度、降低電路的功耗和減少電路邏輯輸出的誤差,因此延時、功耗和誤差是數字電路三個最重要的性能指標。

2024-02-19 13:36:08 2355

2355

單bit通過兩級同步打拍可以有效的解決亞穩(wěn)態(tài)問題。

2024-03-08 09:02:46 2754

2754

今天看到一個格雷碼計數的程序,搜了下定義,覺得還是云里霧里,定義寫的是若任意兩個相鄰的代碼只有一位二進制數不同,則這種編碼為格雷碼。首先數據傳輸時,如果是兩字節(jié)數據0x12和0x34,那最后轉成格雷

2018-08-20 14:41:36

格雷碼簡介及格雷碼與二進制的轉換程序格雷碼簡介 格雷碼(英文:Gray Code, Grey Code,又稱作葛萊碼,二進制循環(huán)碼)是1880年由法國工程師Jean-Maurice-Emlle

2011-04-22 09:00:58

關系,因而在狀態(tài)圖中每條轉移邊需要包含輸入和輸出的信息。狀態(tài)編碼 數字邏輯系統(tǒng)狀態(tài)機設計中常見的編碼方式有:二進制碼(Binary碼)、格雷碼(Gray碼)、獨熱碼(One-hot碼)以及二一十進制碼(BCD

2012-03-09 10:04:18

時鐘域處理方法如下:打兩拍;異步雙口RAM;格雷碼轉換。01方法一:打兩拍大家很清楚,處理跨時鐘域的數據有單bit和多bit之分,而打兩拍的方式常見于處理單bit數據的跨時鐘域問題。打兩拍的方式,其實

2021-03-04 09:22:51

大家好,我正在學習FPGA關于狀態(tài)機的知識點。看到書中寫到:格雷碼最大優(yōu)點在于編碼依次變化,相鄰兩個編碼之間只有一位發(fā)生變化,這樣就不會產生“過渡噪聲”。例如:二進制編碼0111轉換為下一

2017-06-19 20:29:26

dlp4500模式序列投射格雷碼,但是當設置pattern exposure:8333,pattern period為9000時其投射出來的圖案就亂了,我看了一下他的圖片連接時間image load timing 每一張都大約100ms請問如何設置呢?

2025-02-26 07:22:03

時鐘域處理方法如下:打兩拍;異步雙口RAM;格雷碼轉換。01方法一:打兩拍大家很清楚,處理跨時鐘域的數據有單bit和多bit之分,而打兩拍的方式常見于處理單bit數據的跨時鐘域問題。打兩拍的方式,其實

2021-02-21 07:00:00

的三種方法跨時鐘域處理方法如下: 1. 打兩拍; 2. 異步雙口RAM; 3. 格雷碼轉換。 方法一:打兩拍 大家很清楚,處理跨時鐘域的數據有單bit和多bit之分,而打兩拍的方式常見于處理

2021-01-08 16:55:23

在編寫有限狀態(tài)機時,為什么采用獨熱碼會占用更多的觸發(fā)器和更少的組合邏輯?從FPGA內部結構和數電知識基礎上怎樣理解???求大神們不吝賜教,多謝。

2016-03-02 00:33:29

。而絕對式編碼器是直接輸出數字量的傳感器,它是利用自然二進制或循環(huán)二進制(格雷碼)方式進行光電轉換的,編碼的設計一般是采用自然二進制碼、循環(huán)二進制碼、二進制補碼等。特點是不要計數器,在轉軸的任意位置

2011-03-08 14:16:59

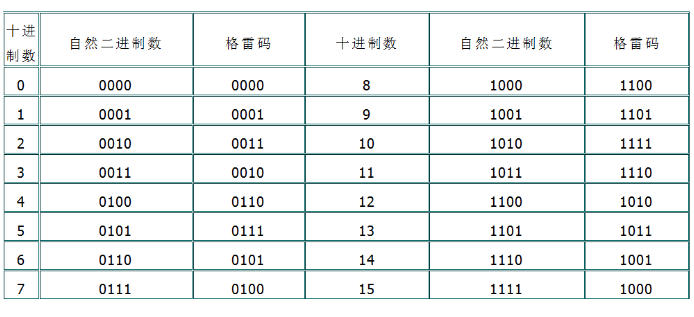

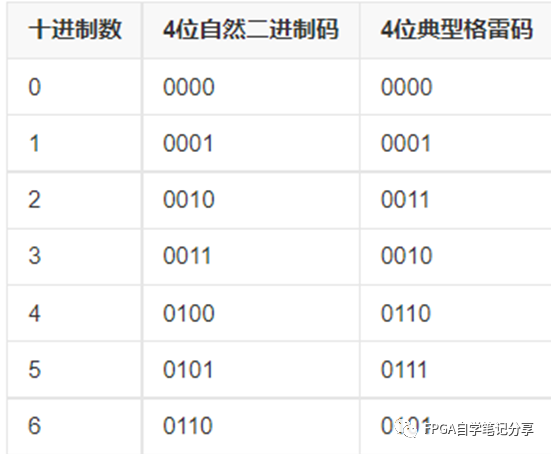

的是8421BCD碼,無權碼用得較多的是余三碼和格雷碼,我們通常所說的BCD碼指的是8421BCD碼。這些編碼跟十進制數對應的關系如下:十進制數 8421BCD碼 余3碼 格雷碼

2011-11-03 17:36:24

你好!目前我正在編寫一個代碼,涉及ASCII字符與其Gray代碼等價的轉換。我已經為我正在使用的測試代碼附加了一個文件。我花了好幾個小時試圖弄清楚在調用ascii和調用gray之間應該放置什么,以便所有東西都按預期流動,所以我一直試圖弄清楚如何確切地告訴代碼進行轉換。我在想你們是不是能幫上忙或者至少給出你的想法。任何幫助是贊賞!

2020-03-27 09:22:23

你好,我在使用DLPC350 投射格雷碼(8bit深度)時,當 切換pattern頻率 > 10frame/s,出現了圖像錯誤或者說 圖像重疊的問題:

從圖像看,像

2025-02-21 16:03:00

最近完成使用MSVC編譯器重新生成了DLP_SDK,并且將TIDA-00254項目也在msvc編譯器下重新生成成功,但是在執(zhí)行Prepare DLP LightCrafter 4500時,生成的兩張格雷碼編碼圖片有問題,如附件,請問,這種情況是怎么回事?

2025-02-28 06:37:04

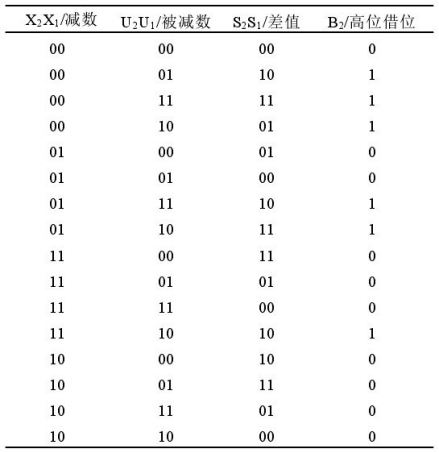

可編程邏輯器件(PLD),只不過我們一般將其用作非易失存儲器,我們以Atmel的AT28C16為例介紹如何具體實現組合邏輯的設計 首先我們要設計4位的二進制轉4位格雷碼轉換器,設一組4位二進制數值,數值按

2015-10-25 22:13:16

RAM測試方法基于格雷碼掃描的MARCH改進方法

2020-12-30 07:58:25

以手到擒來。這里介紹的三種方法跨時鐘域處理方法如下:打兩拍;異步雙口 RAM;格雷碼轉換。01方法一:打兩拍大家很清楚,處理跨時鐘域的數據有單 bit 和多 bit 之分,而打兩拍的方式常見于處理單 bit

2020-09-22 10:24:55

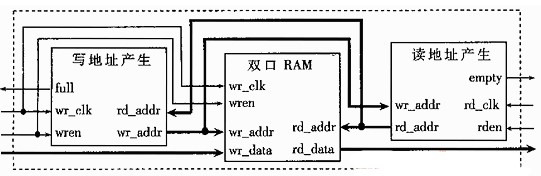

通過對FPGA芯片內部EBRSRAM的深入研究,提出了一種利用格雷碼對地址進行編碼的異步FIFO設計方案。

2021-04-13 06:41:03

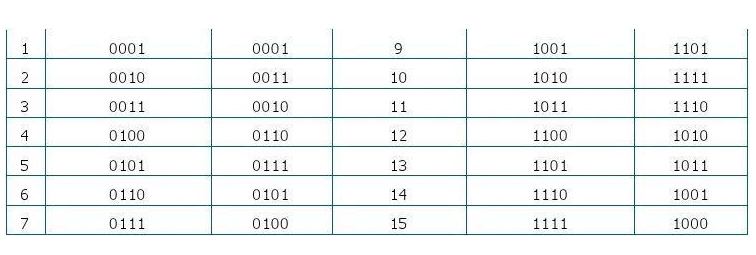

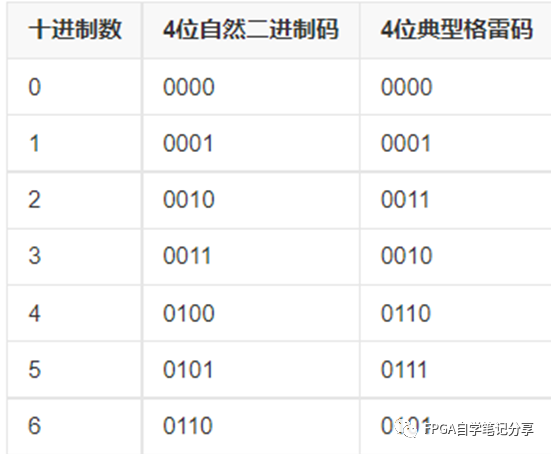

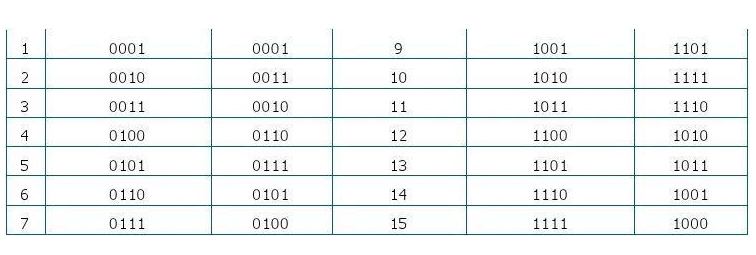

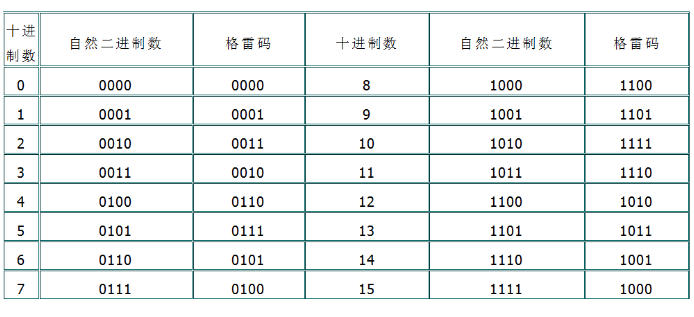

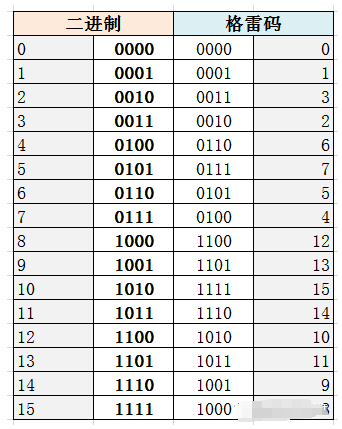

反射碼(循環(huán)碼)十進制數 二進制數 格雷碼 十進制數 二進制數 格雷碼 0 0000 0000 8 1000 1100 1 0001 0001 9 1001 1101 2 0010 0011 10

2011-04-11 10:00:29

以手到擒來。這里介紹的三種方法跨時鐘域處理方法如下:打兩拍;異步雙口 RAM;格雷碼轉換。01方法一:打兩拍大家很清楚,處理跨時鐘域的數據有單 bit 和多 bit 之分,而打兩拍的方式常見于處理單 bit

2020-10-20 09:27:37

求一個一種可控4位碼轉換電路設計。選擇合適的芯片設計一個可逆的4位碼轉換電路。當控制信號為1時,它將8421碼轉換為格雷碼;當控制信號為0時,它將格雷碼轉換為8421碼。

2020-05-25 10:12:53

本帖最后由 gk320830 于 2015-3-8 19:55 編輯

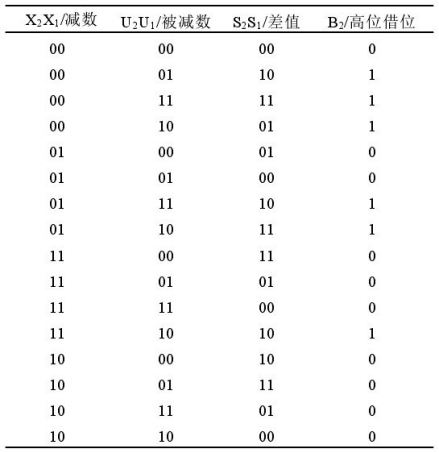

設計要求:在控制信號C=1時,將8421碼轉換為格雷碼;C=0時,將格雷碼轉換為8421碼;寫出設計步驟,列出碼變換

2012-12-27 21:25:09

以及四位碼A3A2A1A0,輸出為四位碼Y3Y2Y1Y0。當C=1時,A3A2A1A0為二進制碼,Y3Y2Y1Y0為格雷碼,電路將二進制碼轉換成格雷碼:當C=0時,A3A2A1A0為格雷碼

2015-10-24 11:03:28

//Asynchronic FIFO //function description//using gray code to synchronic asynchronic signalmoduleAsyncFIFO(wclk,rclk,wen,ren,din,dout,wrst,rrst,rempty,wfull);parameterDataWidth=8,RamDepth =16,AddrWidth=4;//portwriteinputwclk;inputwen;input[(DataWidth-1):0]din;inputwrst;//portreadinputrclk;inputren;inputrrst;//output portoutput[(DataWidth-1):0]dout;outputrempty;//high activeoutputwfull;//high active//regrempty;//regwfull;//wire[(DataWidth-1):0]dout;reg[(DataWidth-1):0]dout;wirerempty_val;wirewfull_val;/*****************************///FIFO MEMORYreg[(DataWidth-1):0]FIFO_RAM[(RamDepth-1):0];//writewire[(AddrWidth-1):0]raddr;//read addresswire[(AddrWidth-1):0]waddr;//write addressreg[AddrWidth:0]rptr_binary;//read pointer with MSBreg[AddrWidth:0]wptr_binary;//write pointer with MSBwire[AddrWidth:0]rptr_gray;//read pointer transform to gray code wire[AddrWidth:0]wptr_gray;//write pointer transform to gray codereg[AddrWidth:0]wptr_gray1;reg[AddrWidth:0]rptr_gray1;//用寄存器輸出的原因是,因為在同步到另一個時鐘域的時候,必須不經過任何組合邏輯,同步器的第一級對于組合邏輯產生的毛刺很敏感,//同時同步器的兩個寄存器要盡量的放的近些。防止設計者加入組合邏輯//synchronic reg variate reg[AddrWidth:0]w_rptr_gray;reg[AddrWidth:0]w_rptr_gray1; reg[AddrWidth:0]r_wptr_gray;reg[AddrWidth:0]r_wptr_gray1;//write and read address generationassignraddr = rptr_binary[(AddrWidth-1):0];assignwaddr = wptr_binary[(AddrWidth-1):0];/*******************the synchronization of asynchronous clock dpmains************///read pointer synchronize to write clockalways @(posedge wclk,negedge wrst)if(!wrst){w_rptr_gray1,w_rptr_gray}

2016-07-04 16:48:19

我在網上看到一篇利用格雷碼來設計異步FIFO,但是看他們寫的一些源碼,小弟有些不是很理解,在設計時為什么會出現Waddr和wptr兩個關于寫指針的問題,他們之間的關系是什么????wptr在定義時候為什么比Waddr多一位呀???

2017-05-19 11:04:13

請問:看了幾天,沒頭緒。難道是做成很多副圖片,按順序投射出來的?謝謝

2019-02-13 10:17:48

,我想用格雷碼進行3D重建,這個格雷碼的固件直接生成好的demo嗎,還是說要在opencv里自己生成序列重新生成那個bin文件?謝謝!

2025-02-26 06:13:46

產品介紹:precilec雷恩rcs58s系列,屬于雷恩絕對值產品的一個標準類型,外徑58mm,單圈16位,輸出信號為格雷碼制SSI同步串行,產品采用嚴格防塵防水,高的防護等級,ip66/ip67

2022-01-10 14:42:07

格雷碼計數器的Verilog描述

2009-08-03 09:39:58 45

45 介紹了位置檢測傳感器---絕對值編碼器的原理及特點,并介紹了一種在PLC 控制系統(tǒng)中,將編碼器的格雷編碼轉換為二進制編碼的一種運算方法及其在位置檢測中的應用。實踐

2009-08-13 09:28:34 173

173 本文提出了基于FPGA 正碼速調整的設計方案,采用格雷碼對地址編碼的異步FIFO設計,并利用MAXPLUSⅡ進行編譯和仿真。結果表明,設計方法切實可行。

2010-01-13 15:16:07 25

25 給出了一個利用格雷碼對地址編碼的羿步FIFO 的實現方法,并給出了VHDL 程序,以解決異步讀寫時鐘引起的問題。

2010-07-16 15:15:42 26

26 格雷碼簡介及格雷碼與二進制的轉換程序

格雷碼簡介 格雷碼(英文:Gray Code, Grey Code,又稱作葛萊碼,二進制循環(huán)碼)是1880年由

2009-01-16 11:52:52 5434

5434 和羅盤式等,被廣泛應用于氣象、海洋、環(huán)境、農業(yè)、林業(yè)、水利、電力、科研等領域。測量原理光電式風向傳感器的核心采用絕對式格雷碼盤編碼(四位格雷碼或七位格雷 碼),利用光

2025-01-14 16:15:00

格雷碼運算研究

在數字系統(tǒng)中只能識別0和1,各種數據要轉換為二進制代碼才能進行處理,格雷碼是一種無權碼,采用絕對編碼方式,典型格雷碼是

2010-03-18 14:07:20 1612

1612 我們知道格雷碼計數的特點就是相鄰的碼字只有一個比特不同,那么我們在設計格雷碼計數時找到這個比特取反就是了。找到這個比特的思路: 先將格雷碼換算成二進制碼,此二進制碼中

2011-11-11 09:32:23 2319

2319 二進位碼第n位 = 二進位碼第(n+1)位+格雷碼第n位。因為二進位碼和格雷碼皆有相同位數,所以二進位碼可從最高位的左邊位元取0,以進行計算

2011-11-11 09:38:43 8404

8404

討論了Gray Code 的由來,剖析了關于格雷碼的一些不合理說法,明確了其正宗的發(fā)明者應該是弗蘭克·格雷,正確的英文名稱是Gray Code,規(guī)范的中文名稱是格雷碼。

2011-11-28 16:04:15 6657

6657

電子發(fā)燒友網核心提示: 本例程是Verilog HDL源代碼:關于基本組合邏輯功能中二進制到格雷碼轉換的功能實現源代碼。注意:程序運行在不同軟件平臺可能要作一些修改,請注意閱讀程

2012-10-15 11:52:00 3942

3942 2014-07-09 22:54:40 6

6 聯(lián)接各品牌的SSI信號傳感器

★SSI信號可同時冗余設備連接PLC的SSI模塊和本款儀表

★強大的信號與電源抗干擾容錯功能,更可靠安全

★單圈10-26位可調,多圈24-29位可調

★輸入信號格雷碼

2016-04-28 16:59:59 12

12 典型的二進制格雷碼簡稱格雷碼,因1953年公開的弗蘭克·格雷專利“Pulse Code Communication”而得名,當初是為了通信,現在則常用于模擬-數字轉換和位置-數字轉換中。法國電訊工程師波特在1880年曾用過的波特碼相當于它的一種變形。

2018-03-02 14:29:55 60398

60398

在一組數的編碼中,若任意兩個相鄰的代碼只有一位二進制數不同,則稱這種編碼為格雷碼(Gray Code),另外由于最大數與最小數之間也僅一位數不同,即“首尾相連”,因此又稱循環(huán)碼或反射碼。

2018-03-02 14:47:11 39921

39921

格雷碼屬于可靠性編碼,是一種錯誤最小化的編碼方式。因為,雖然自然二進制碼可以直接由數/模轉換器轉換成模擬信號,但在某些情況,例如從十進制的3轉換為4時二進制碼的每一位都要變,能使數字電路產生很大的尖峰電流脈沖。

2018-03-02 15:23:58 50302

50302

格雷碼,又叫循環(huán)二進制碼或反射二進制碼,格雷碼是我們在工程中常會遇到的一種編碼方式,它的基本的特點就是任意兩個相鄰的代碼只有一位二進制數不同,這點在下面會詳細講解到。格雷碼的基本特點就是任意兩個相鄰的代碼只有一位二進制數不同。

2018-03-02 15:48:53 19588

19588

編碼器是將信號或數據進行編制、轉換為可用以通訊、傳輸和存儲的信號形式的設備。格雷碼屬于可靠性編碼,是一種錯誤最小化的編碼方式。因為,雖然自然二進制碼可以直接由數/模轉換器轉換成模擬信號。

2018-03-02 16:13:26 13461

13461

通過改變設計,破壞毛刺產生的條件,來減少毛刺的發(fā)生。例如,在數字電路設計中,常常采用格雷碼計數器取代普通的二進制計數器,這是因為格雷碼計數器的輸出每次只有一位跳變,消除了競爭冒險的發(fā)生條件,避免了毛刺的產生。

2018-06-23 08:49:00 2095

2095

設計背景:典型的二進制格雷碼(Binary Gray Code)簡稱格雷碼,因1953年公開的弗蘭克·格雷(Frank Gray,18870913-19690523)專利“Pulse Code

2018-08-28 16:16:03 3907

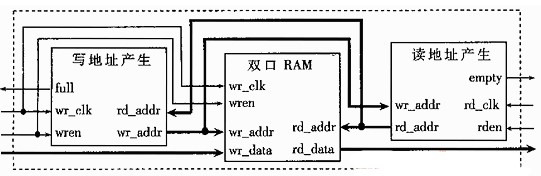

3907 FIFO (先進先出隊列)是一種在電子系統(tǒng)得到廣泛應用的器件,通常用于數據的緩存和用于容納異步信號的頻率或相位的差異。FIFO的實現通常是利用雙口RAM和讀寫地址產生模塊來實現的。FIFO的接口信號包括異步的寫時鐘(wr_clk)和讀時鐘(rd_clk)、與寫時鐘同步的寫有效(wren)和寫數據(wr_data)、與讀時鐘同步的讀有效(rden)和讀數據(rd_data)。

2019-08-02 08:10:00 2872

2872

在傳遞讀寫時鐘域的指針使用格雷碼來傳遞,如何把二進制轉換為格雷碼,格雷碼是如何判斷讀空寫滿呢?

2018-09-15 09:38:19 9117

9117

格雷碼(Gray Code)因1953年公開的弗蘭克.格雷的專利而得名。格雷碼是二進制循環(huán)碼,其編碼最大的特點是任意上下相鄰的兩個碼值間,只有一位碼不同,這樣在碼值上下變化過程中,每次只改變一位碼

2019-01-11 10:28:48 16765

16765

異步FIFO通過比較讀寫地址進行滿空判斷,但是讀寫地址屬于不同的時鐘域,所以在比較之前需要先將讀寫地址進行同步處理,將寫地址同步到讀時鐘域再和讀地址比較進行FIFO空狀態(tài)判斷(同步后的寫地址一定是小于或者等于當前的寫地址,所以此時判斷FIFO為空不一定是真空,這樣更保守)。 將讀地址同步到寫時鐘域再和寫地址比較進行FIFO滿狀態(tài)判斷(同步后的讀地址一定是小于或者等于當前的讀地址,所以此時判斷FIFO為滿不一定是真空,這樣更保守

2021-08-04 14:05:21 5131

5131 絕對編碼器中的傳感器輸出格雷碼序列,需要一些復雜的轉換方法才能正確使用。本文展示了如何獲取絕對編碼器使用的格雷碼并將其轉換為二進制。

2022-05-05 15:41:49 8256

8256

本文介紹格雷碼,這是絕對編碼器與控制器通信所必需的一種特殊二進制排列。

2022-05-05 15:47:11 12361

12361 格雷碼(Gray Code)是由貝爾實驗室的弗蘭克·格雷(Frank Gray,1887-1969)在20世紀40年代提出,并在1953年取得美國專利“Pulse Code

2022-07-03 11:41:34 7272

7272 Push信息產生的連續(xù)寫指針wpt, 通過同步后,在rclk域與rpt進行比較,以產生rclk域的Empty信號。

2022-09-02 11:20:24 3886

3886 格雷碼是一種特殊的二進制碼,在結構光三維視覺中,常常被用于編碼。比起我們常見的二進制碼,格雷碼具有相鄰數字的編碼只有一位不同的優(yōu)點,這個優(yōu)點對于解碼而言十分重要,可以減少光解碼的錯誤率。下面我們可以看下如何對結構光用格雷碼編碼,并如何對編碼的結構光進行解碼。

2022-12-21 11:14:51 2016

2016 格雷碼的解碼很簡單,只要把投影的格雷碼結構光再還原回十進制數字,我們就能知道相機中的像素點(uc,vc)對應的是投影圖片的哪一列(up)了。想要得到一個好的三維重建結果,主要是對相機捕捉到的結構光進行準確的二值化操作,使得相機圖片中每個像素點都能夠正確解碼。

2022-12-21 11:06:11 2031

2031 對于新手來說,使用格雷碼做單目結構光三維重建是一個入門級的訓練。但是在復現時往往會遇到一個問題,明明解碼都很不錯了,重建后的點云精度卻很低,甚至重建出來的平面點云出現斷層現象。

2023-01-13 11:41:16 1930

1930 格雷碼是一種循環(huán)二進制編碼,特點是相鄰數變化時只有一位數據跳變。

2023-01-17 11:15:17 6786

6786

FPGA多bit跨時鐘域適合將計數器信號轉換為格雷碼。

2023-05-25 15:21:31 3679

3679

上一篇文章我們講了二進制轉gray碼,這次我們聊一下gray碼轉二進制碼。

2023-05-25 15:22:07 2538

2538

很多人在面試時被問到為什么異步FIFO中需要用到格雷碼,可能大部分的答案是格雷碼可以消除亞穩(wěn)態(tài)。這種回答比較模糊,今天我們就針對這個來深入探討一下。

2023-08-26 14:20:25 1655

1655

異步FIFO包含"讀"和"寫“兩個部分,寫操作和讀操作在不同的時鐘域中執(zhí)行,這意味著Write_Clk和Read_Clk的頻率和相位可以完全獨立。異步FIFO的原理很簡單,寫操作是在寫使能有效時,寫地址指針(Write_Pointer)逐漸遞增,將數據寫入存儲器的相應位置。讀操作是在讀使能信號有效時,讀地址指(Read_Pointer)逐漸遞增,從存儲器的相應位置讀取數據。

2023-09-14 11:21:45 2183

2183

設計者為了提升FIFO的速度使用了將二進制計數器和格雷碼計數器結合在一起的方法,從最開始用一組寄存器來進行格雷碼到二進制碼的轉換,二進制碼的遞增和二進制碼到格雷碼的轉換,到后來的style#2(如圖)。

2023-10-20 10:50:00 1055

1055

?公用端子插腳中心位置?可用格雷碼輸出?良好的視覺性?可水洗?BCD10Position?端接樣式:J型引線

2022-09-21 11:37:20 0

0 ?公用端子插腳中心位置?可用格雷碼輸出?良好的視覺性?可水洗?BCD10Position?端接樣式:鷗翼

2022-09-21 11:37:21 0

0 ?公用端子插腳中心位置?可用格雷碼輸出?良好的視覺性?可水洗?BCD16Position?端接樣式:J型引線

2022-09-21 11:37:22 0

0 ?公用端子插腳中心位置?可用格雷碼輸出?良好的視覺性?可水洗?BCD16Position?端接樣式:鷗翼

2022-09-21 11:37:22 0

0 符合RoHS標準公用端子插腳中心位置可用格雷碼輸出良好的視覺性可水洗

2022-09-21 11:39:25 0

0 符合RoHS標準公用端子插腳中心位置可用格雷碼輸出良好的視覺性可水洗

2022-09-21 11:39:26 0

0 符合RoHS標準公用端子插腳中心位置可用格雷碼輸出良好的視覺性可水洗

2022-09-21 11:39:26 0

0 符合RoHS標準公用端子插腳中心位置可用格雷碼輸出良好的視覺性可水洗

2022-09-21 11:39:27 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論