本文介紹FPGA與高速ADC接口方式和標(biāo)準(zhǔn)以及JESD204與FPGA高速串行接口。

2025-06-12 14:18:21 2883

2883

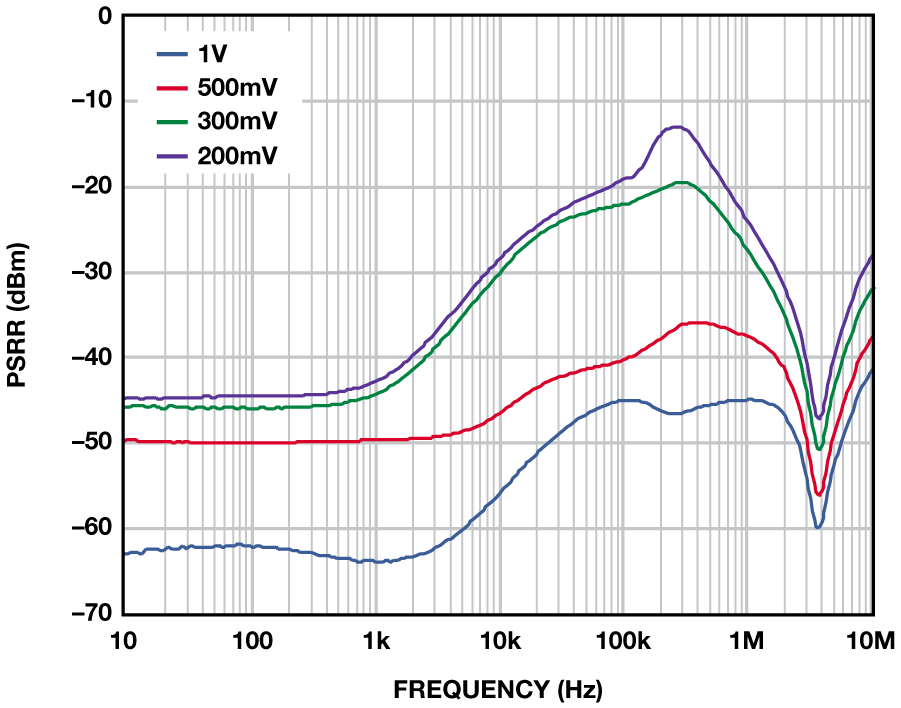

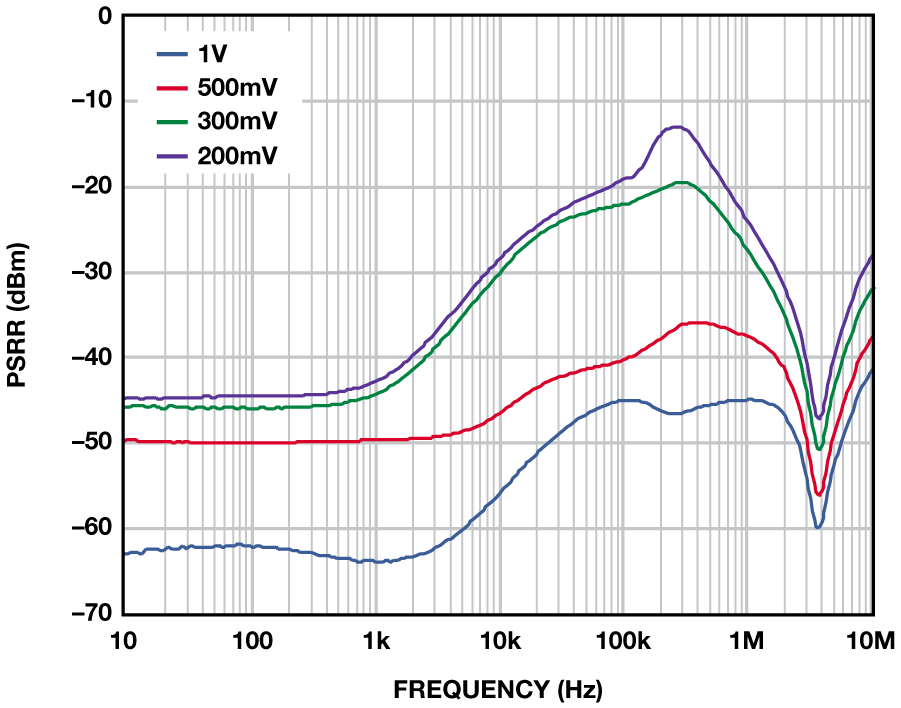

LDO 電源抑制比(PSRR)與裕量電壓相關(guān)——裕量電壓指輸入與輸出電壓之差。對(duì)于固定裕量電壓,PSRR隨著負(fù)載電流的提高而降低,大負(fù)載電流和小裕量電壓條件下尤其如此。

2022-11-30 11:10:25 2545

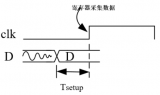

2545 今天有個(gè)小伙伴遇到一個(gè)問(wèn)題,就是在vivado里面綜合后看到的建立時(shí)間和保持時(shí)間裕量都是inf,我們來(lái)看看怎么解決這個(gè)問(wèn)題。

2023-07-30 10:26:02 2193

2193

這篇文章是探討對(duì)接收端進(jìn)行時(shí)序優(yōu)化(即ready打拍,或稱(chēng)backward打拍)的方式。

2023-12-04 10:20:55 1207

1207

在數(shù)字IC/FPGA設(shè)計(jì)的過(guò)程中,對(duì)PPA的優(yōu)化是無(wú)處不在的,也是芯片設(shè)計(jì)工程師的使命所在。此節(jié)主要將介紹performance性能的優(yōu)化,如何對(duì)時(shí)序路徑進(jìn)行優(yōu)化,提高工作時(shí)鐘頻率。

2025-12-09 10:33:20 2964

2964

在TMS320LF2407串行接口中的信息傳遞的高速率。本設(shè)計(jì)綜合考慮速度、工作電壓、噪聲容限等因素的影響.采用了一種新穎的觸發(fā)器結(jié)構(gòu)(圖4A部分),本文接口電路中大都采用了該觸發(fā)器的電路設(shè)計(jì),工作電壓降低到3.3V,大大

2019-06-18 05:00:11

下一代總線,在各自的瓶頸上,時(shí)序裕量非常小,設(shè)計(jì)極為困難。其二,由于技術(shù)的發(fā)展,大家更多的關(guān)注DDR3,關(guān)注高速串行總線,共同時(shí)鐘系統(tǒng)的研究越來(lái)越少,相應(yīng)的總結(jié)文章也不常見(jiàn),就帶來(lái)很多設(shè)計(jì)問(wèn)題,也就

2014-10-21 09:35:50

和遠(yuǎn)端串?dāng)_這種方法來(lái)研究多線間串?dāng)_問(wèn)題。利用Hyperlynx,主要分析串?dāng)_對(duì)高速信號(hào)傳輸模型的侵害作用并根據(jù)仿真結(jié)果,獲得了最佳的解決辦法,優(yōu)化設(shè)計(jì)目標(biāo)。【關(guān)鍵詞】:信號(hào)完整性;;反射;;串?dāng)_;;近

2010-05-13 09:10:07

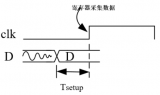

高速電路的時(shí)序分析電路中,數(shù)據(jù)的傳輸一般都是在時(shí)鐘對(duì)數(shù)據(jù)信號(hào)進(jìn)行有序的收發(fā)控制下進(jìn)行的。芯片只能按規(guī)定的時(shí)序發(fā)送和接收數(shù)據(jù),過(guò)長(zhǎng)的信號(hào)延遲或信號(hào)延時(shí)匹配不當(dāng)都會(huì)影響芯片的建立和保持時(shí)間,導(dǎo)致芯片無(wú)法

2012-08-02 22:26:06

DDR布線在pcb設(shè)計(jì)中占有舉足輕重的地位,設(shè)計(jì)成功的關(guān)鍵就是要保證系統(tǒng)有充足的裕量。要保證系統(tǒng)的時(shí)序,線長(zhǎng)又是一個(gè)重要的環(huán)節(jié)。我們來(lái)回顧一下,DDR布線,線長(zhǎng)匹配的基本原則是:地址,控制/命令信號(hào)

2018-09-20 10:29:55

的保持時(shí)間Th 3. 時(shí)序裕量SlackSlack :約束文件要求時(shí)鐘周期與實(shí)際布局布線后時(shí)鐘周期的差值,表示時(shí)序裕量的一個(gè)稱(chēng)謂,大于零表示滿足時(shí)序,小于零表示不滿足時(shí)序1) Setup

2018-07-03 02:11:23

的保持時(shí)間Th 3. 時(shí)序裕量SlackSlack :約束文件要求時(shí)鐘周期與實(shí)際布局布線后時(shí)鐘周期的差值,表示時(shí)序裕量的一個(gè)稱(chēng)謂,大于零表示滿足時(shí)序,小于零表示不滿足時(shí)序1) Setup

2018-07-09 09:16:13

FPGA中的I_O時(shí)序優(yōu)化設(shè)計(jì)在數(shù)字系統(tǒng)的同步接口設(shè)計(jì)中, 可編程邏輯器件的輸入輸出往往需要和周?chē)缕瑢?duì)接,此時(shí)IPO接口的時(shí)序問(wèn)題顯得尤為重要。介紹了幾種FPGA中的IPO時(shí)序優(yōu)化設(shè)計(jì)的方案, 切實(shí)有效的解決了IPO接口中的時(shí)序同步問(wèn)題。

2012-08-12 11:57:59

VGA驅(qū)動(dòng)接口時(shí)序設(shè)計(jì)之7優(yōu)化本文節(jié)選自特權(quán)同學(xué)的圖書(shū)《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt最后,再次編譯系統(tǒng),查看時(shí)序

2015-08-10 15:03:08

FPGA的時(shí)序優(yōu)化高級(jí)研修班通知通過(guò)設(shè)立四大專(zhuān)題,幫助工程師更加深入理解FPGA時(shí)序,并掌握時(shí)序約束和優(yōu)化的方法。1.FPGA靜態(tài)時(shí)序分析2.FPGA異步電路處理方法3.FPGA時(shí)序約束方法4.FPGA時(shí)序優(yōu)化方法

2013-03-27 15:20:27

FPGA平臺(tái)接地點(diǎn)接線到實(shí)驗(yàn)室大地。

綜上所述,F(xiàn)PGA的高速接口應(yīng)用需要綜合考慮信號(hào)完整性、電源管理、接口標(biāo)準(zhǔn)化、布線與布局以及靜電防護(hù)等方面。遵循這些注意事項(xiàng)將有助于確保FPGA高速接口的穩(wěn)定性和可靠性,從而滿足各種應(yīng)用場(chǎng)景對(duì)數(shù)據(jù)吞吐量、信號(hào)完整性、低延遲和高可靠性的嚴(yán)格要求。

2024-05-27 16:02:50

容差,設(shè)計(jì)師可以優(yōu)化功耗和輸出噪聲,為敏感型模擬電路打造出高效的低噪聲電源。在裕量電壓超低的條件下,輸入和輸出電壓的最差條件容差可能對(duì) PSRR 形成影響。在設(shè)計(jì)時(shí)充分考慮最差條件容差可以確保可靠

2018-10-23 17:07:54

的延時(shí)。并且當(dāng)大量不同的讀請(qǐng)求交叉處理時(shí),讀處理模塊的并行處理結(jié)構(gòu)更能夠充分利用PCIe的亂序傳輸能力來(lái)提高吞吐量。為了清晰的說(shuō)明讀處理模塊對(duì)吞吐量的提升,設(shè)置如圖1所示的簡(jiǎn)單時(shí)序樣例,樣例中PCIe

2025-08-05 18:09:27

布線在設(shè)計(jì)中占有舉足輕重的地位,設(shè)計(jì)成功的關(guān)鍵就是要保證系統(tǒng)有充足的時(shí)序裕量。要保證系統(tǒng)的時(shí)序,線長(zhǎng)匹配又是一個(gè)重要的環(huán)節(jié)。我們來(lái)回顧一下,布線,線長(zhǎng)匹配的基本原則是:地址,控制/命令信號(hào)與時(shí)鐘

2018-09-20 10:59:44

InTime 利用大數(shù)據(jù)分析和人工智能,建立時(shí)序數(shù)據(jù)庫(kù),無(wú)需修改源代碼即可優(yōu)化設(shè)計(jì),為工程師推薦最佳工具參數(shù)組合。了解更多>>

2017-04-18 14:53:40

Hi,用到TI的電源芯片TPS54329,原理圖設(shè)計(jì)、環(huán)路測(cè)試結(jié)果如附件。 在測(cè)試環(huán)路穩(wěn)定性時(shí),將C20分別焊上22pF和68pF。測(cè)得結(jié)果22pF相位裕量不足,68pF相位裕量較好。但是參考其

2019-07-25 14:08:42

描述此參考設(shè)計(jì)可輕松實(shí)現(xiàn)支持電壓裕量調(diào)節(jié)功能的 USB Type-C? 電源的系統(tǒng)集成。TPS62136 降壓轉(zhuǎn)換器可高效地將電源從常用 9V、12V 或 15V 適配器轉(zhuǎn)換為 USB Type-C

2018-10-26 10:38:28

能夠有一些時(shí)序問(wèn)題,我們?cè)偻ㄟ^(guò)時(shí)序分析的方法對(duì)它進(jìn)行優(yōu)化。我們這里把原本的100M時(shí)鐘改成了200M時(shí)鐘,具體步驟如下: 一:更改時(shí)鐘之后進(jìn)行綜合,并打開(kāi)timing analysis 二:通過(guò)

2018-08-22 11:45:54

輪的運(yùn)行后,即擊中目標(biāo)時(shí)序,TNS=0。 VXLAN_S57H項(xiàng)目相對(duì)需要優(yōu)化的目標(biāo)較為簡(jiǎn)單,容易滿足。且工程量較小,整體綜合編譯布局布線周期較短,無(wú)法有力說(shuō)明InTime帶來(lái)的優(yōu)化便利性。工程2工程2

2017-07-05 11:00:48

合成。正弦波的衰減將導(dǎo)致需要傳輸?shù)男盘?hào)產(chǎn)生邊沿退化、幅度降低等問(wèn)題,影響傳輸線的帶寬。使用高速板材可以降低單位長(zhǎng)度傳輸線的損耗。所以在線長(zhǎng)相同的情況下,高速板材能使傳輸線帶寬更高,信號(hào)裕量更大。同理

2019-06-27 18:38:26

在繪制電氣CAD圖紙的過(guò)程中,生成設(shè)備表是必不可少的。那么生成設(shè)備表的過(guò)程中需要統(tǒng)計(jì)線纜長(zhǎng)度時(shí)考慮到實(shí)際工程的情況,此時(shí)便需要用到浩辰CAD電氣軟件中的線纜裕度功能了。那么什么是CAD線纜裕度?又如

2021-05-20 09:48:47

提出有效的PPA優(yōu)化方案。其實(shí)這一條經(jīng)驗(yàn)是并不特指高頻設(shè)計(jì),是做好設(shè)計(jì)的基本功,缺陷率高同學(xué)往往問(wèn)題就出現(xiàn)在這里。2.建立把代碼通過(guò)人腦轉(zhuǎn)化成電路的能力。verilog描述的就是電路,時(shí)序優(yōu)化也是在電路

2022-06-23 15:43:18

最近用EPM1270T144C5N 做了一個(gè)可編程的延遲脈沖發(fā)生器,設(shè)計(jì)頻率100M,在QUARTUS里編譯完了之后軟件給出時(shí)序警告,有些路徑setup裕量不足,給出的Fmax僅為84.41M,但是燒到板子里用100M晶振還是可以正常工作,是不是timequest analyzer不靠譜啊。

2014-04-18 15:31:15

摘要:RS 232接口是現(xiàn)在最常用的一種通信接口。隨著FPGA技術(shù)的高速發(fā)展,一些常見(jiàn)的接口電路的時(shí)序電路可以通過(guò)FPGA實(shí)現(xiàn),通過(guò)這種設(shè)計(jì)可減少電路系統(tǒng)元件的數(shù)量,提高系統(tǒng)集成度和可靠性。詳細(xì)闡述

2019-06-19 07:42:37

今天跟大家分享下浙江大學(xué)原創(chuàng)的“高速設(shè)計(jì)講義”(如有侵權(quán)請(qǐng)告知),內(nèi)含設(shè)計(jì)方法、信號(hào)完整性、板級(jí)高速時(shí)序分析!{:19:}

2016-08-17 14:14:57

Hi,以前在學(xué)校的時(shí)候就經(jīng)常遇見(jiàn)時(shí)序收斂的問(wèn)題,尤其是改RTL好麻煩啊。工作以后和朋友們一起做了個(gè)時(shí)序優(yōu)化的軟件,叫InTime,希望可以幫助有相同問(wèn)題的朋友。^_^我們搞了免費(fèi)試用的活動(dòng),有興趣

2017-05-11 10:55:17

降低效率為代價(jià)。優(yōu)化配電網(wǎng)絡(luò)可以改善這些參數(shù),同時(shí)將噪聲降低到必要的水平。本文在闡述高性能信號(hào)鏈中電源紋波的影響的基礎(chǔ)上進(jìn)一步分析。我們將深入探討如何優(yōu)化高速數(shù)據(jù)轉(zhuǎn)換器的配電網(wǎng)絡(luò)。我們將對(duì)標(biāo)準(zhǔn)PDN

2021-07-17 07:00:01

上引起的差異,為了更好地說(shuō)明這些Skew對(duì)時(shí)序的具體影響,下面我們還是通過(guò)時(shí)序圖分析的方法來(lái)計(jì)算一下源同步時(shí)鐘系統(tǒng)中信號(hào)的建立時(shí)間裕量和保持時(shí)間裕量。首先考慮建立時(shí)間裕量:和普通時(shí)序分析的方法一下,我們也是從

2014-12-30 14:05:08

紫光的FPGA哪些系列支持高速接口?相關(guān)接口有哪些免費(fèi)的IP可以使用呢?性能怎么樣?

2024-03-20 16:58:29

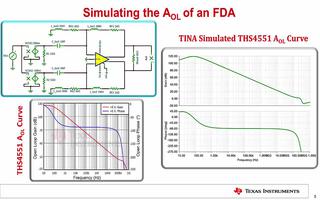

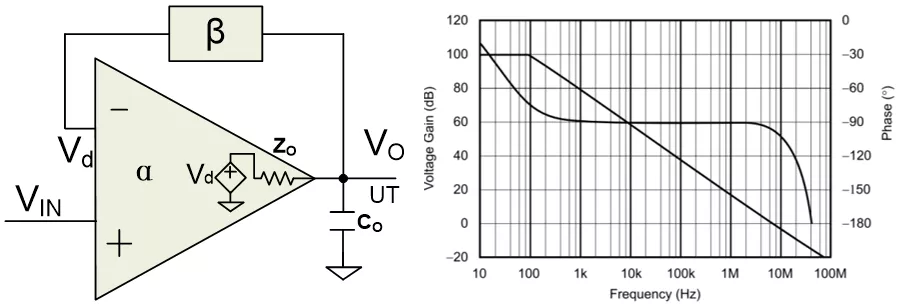

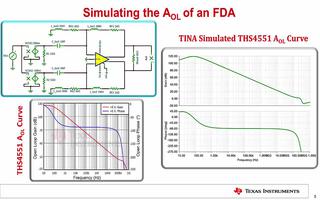

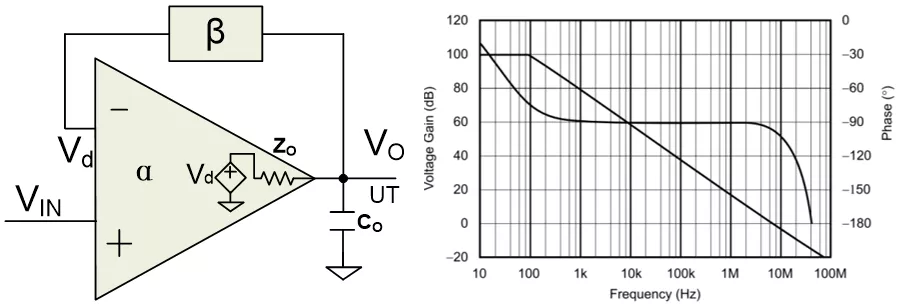

請(qǐng)教如何測(cè)試OP放大器的相位裕量。定義為在開(kāi)環(huán)的情況下0DB所對(duì)應(yīng)的DEG與180的差。但是也有看到提到閉環(huán)情況下測(cè)試。

2024-08-16 15:12:03

如何收斂高速ADC時(shí)序?有哪種辦法可以最大化ADC的建立和保持時(shí)間?

2021-04-14 06:06:09

在穩(wěn)定性分析中,相位裕量要求大于45°。請(qǐng)問(wèn)上圖中的環(huán)路增益曲線的相位裕量是68.59°還是(180°-68.59°)?

2024-08-08 06:30:32

新手,需要對(duì)一個(gè)工程時(shí)序優(yōu)化,現(xiàn)在只能到110MHZ, 需要到150MHZ以上,跪求時(shí)序優(yōu)化資料或例程。。

2015-12-05 11:22:54

問(wèn)題:采用單電源供電時(shí),我的運(yùn)算放大器輸出會(huì)高度失真。這可能是因?yàn)槟撤N裕量問(wèn)題嗎?答案:裕量(headroom)肯定是輸出失真的眾多原因之一。有些人可能還不熟悉裕量的概念,它用于衡量放大器的輸入

2018-10-31 10:23:35

變則通,通則久。事物都有其運(yùn)行的規(guī)律,把握好規(guī)律,就能更好的實(shí)現(xiàn)人的目的。在數(shù)字后端設(shè)計(jì)中,時(shí)序優(yōu)化一直是關(guān)鍵問(wèn)題,尤其追求高頻高性能的設(shè)計(jì)中,時(shí)許問(wèn)題常常貫穿始終。大大小小二十幾個(gè)項(xiàng)目模塊后端工作

2020-12-10 07:37:31

Cadence高速PCB的時(shí)序分析:列位看觀,在上一次的連載中,我們介紹了什么是時(shí)序電路,時(shí)序分析的兩種分類(lèi)(同步和異步),并講述了一些關(guān)于SDRAM 的基本概念。這一次的連載中,

2009-07-01 17:23:27 0

0 Cadence 高速 PCB 的時(shí)序分析 1.引言 時(shí)序分析,也許是 SI 分析中難度最大的一部分。我懷著滿腔的期許給 Cadence 的資深工程師發(fā)了一封 e-mail,希望能夠得到一份時(shí)序分析的案

2010-04-05 06:37:13 0

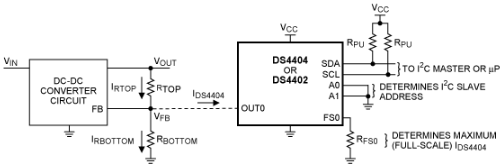

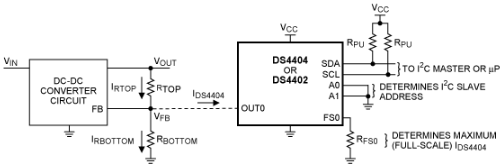

0 如何在DC-DC轉(zhuǎn)換器中增加裕量調(diào)節(jié)功能

本應(yīng)用筆記介紹了一種簡(jiǎn)便的通過(guò)連接DS4404 4通道可調(diào)節(jié)電流型DAC (或2通道版本DS4402)在DC-DC轉(zhuǎn)換器中增加裕量調(diào)節(jié)功能的方法。

2009-04-16 16:08:36 745

745

摘要:隨著高速信號(hào)的普及,迫切需要保證這些信號(hào)接口能夠維持正確時(shí)序和保真度的措施。上升時(shí)間一般在亞納秒級(jí),傳輸延時(shí)在納秒級(jí)。系統(tǒng)對(duì)時(shí)序的要求越來(lái)越嚴(yán)格,如果不

2009-05-05 08:30:48 900

900

DS4426應(yīng)用電路(四通道、I²C、可控制裕量的IDAC,具有三路電源跟蹤)

2009-07-25 21:46:50 868

868 更高速的 ADC 在轉(zhuǎn)換器輸出和接收機(jī)輸入之間有嚴(yán)格的時(shí)序要求;知道如何利用產(chǎn)品說(shuō)明書(shū)數(shù)字來(lái)保證無(wú)錯(cuò)誤數(shù)字傳輸。

最近幾年,高速、高精度的模數(shù)轉(zhuǎn)換器 (ADC)

2010-07-13 09:59:10 969

969 一、摘要 從簡(jiǎn)單SRAM接口到高速同步接口,TimingDesigner軟件允許設(shè)計(jì)者在設(shè)計(jì)流程的初期就判斷出潛在的時(shí)序問(wèn)題,盡最大可能在第一時(shí)間解決時(shí)序問(wèn)題。在設(shè)計(jì)過(guò)程的早期檢測(cè)到時(shí)序問(wèn)題,不僅節(jié)省時(shí)間,而且可以更容易的實(shí)施設(shè)計(jì)方案。美國(guó)EMA公司的設(shè)計(jì)自動(dòng)

2011-01-13 16:25:00 103

103 簡(jiǎn)要介紹了先入先出FIFO存儲(chǔ)器的工作原理! 詳細(xì)剖析了在實(shí)際大型路由器研發(fā)中使用的高速大容量緩存機(jī)制及其設(shè)計(jì)方法!并給出了關(guān)鍵部分的時(shí)序仿真結(jié)果.

2011-05-17 10:44:08 19

19 介紹了采用STA (靜態(tài)時(shí)序分析)對(duì)FPGA (現(xiàn)場(chǎng)可編程門(mén)陣列)設(shè)計(jì)進(jìn)行時(shí)序驗(yàn)證的基本原理,并介紹了幾種與STA相關(guān)聯(lián)的時(shí)序約束。針對(duì)時(shí)序不滿足的情況,提出了幾種常用的促進(jìn) 時(shí)序收斂的方

2011-05-27 08:58:50 70

70 本內(nèi)容詳細(xì)介紹了高速PCB設(shè)計(jì)的布局布線優(yōu)化方法,歡迎大家下載學(xué)習(xí)

2011-09-27 16:22:33 0

0 對(duì)于廣大PCB設(shè)計(jì)工程師而言,提到時(shí)序問(wèn)題就感覺(jué)比較茫然。看到時(shí)序圖,更是一頭霧水,感覺(jué)時(shí)序問(wèn)題特別深?yuàn)W。其實(shí)在平常的設(shè)計(jì)中最常見(jiàn)的是各種等長(zhǎng)關(guān)系,網(wǎng)上流傳的Layout Gu

2012-10-22 11:51:56 5548

5548

電子發(fā)燒友網(wǎng)核心提示 :RS 232接口是現(xiàn)在最常用的一種通信接口。隨著FPGA技術(shù)的高速發(fā)展,一些常見(jiàn)的接口電路的時(shí)序電路可以通過(guò)FPGA實(shí)現(xiàn),通過(guò)這種設(shè)計(jì)可減少電路系統(tǒng)元件的數(shù)量

2012-11-27 10:28:11 11607

11607 LDO的運(yùn)行困境:低裕量和最小負(fù)載 。

2016-01-07 14:32:25 22

22 配置控制器局域網(wǎng)絡(luò)(CAN)位時(shí)序,優(yōu)化系統(tǒng)性能

2016-01-07 16:18:57 0

0 高速SPI和SCI接口

2017-10-20 10:29:04 10

10 時(shí)間和資源,這會(huì)對(duì)系統(tǒng)設(shè)計(jì)進(jìn)度造成負(fù)面影響,更糟糕的是,在設(shè)計(jì)系統(tǒng)時(shí),這類(lèi)負(fù)面影響可能并不明顯。 通過(guò)在接收器處引入PCI Express 4.0(PCIe 4.0)通路裕量特性。

2017-11-16 13:37:50 8211

8211

針對(duì)八通道采樣器AD9252的高速串行數(shù)據(jù)接口的特點(diǎn),提出了一種基于FPGA時(shí)序約束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行數(shù)據(jù),利用FPGA內(nèi)部的時(shí)鐘管理模塊DCM、位置約束

2017-11-17 12:27:01 7353

7353

現(xiàn)有的工具和技術(shù)可幫助您有效地實(shí)現(xiàn)時(shí)序性能目標(biāo)。當(dāng)您的FPGA 設(shè)計(jì)無(wú)法滿足時(shí)序性能目標(biāo)時(shí),其原因可能并不明顯。解決方案不僅取決于FPGA 實(shí)現(xiàn)工具為滿足時(shí)序要求而優(yōu)化設(shè)計(jì)的能力,還取決于設(shè)計(jì)人員指定前方目標(biāo),診斷并隔離下游時(shí)序問(wèn)題的能力。

2017-11-18 04:32:34 3843

3843 與賽靈思FPGA連接的數(shù)據(jù)轉(zhuǎn)換器正迅速采用全新JESD204B高速串行鏈路。要使用該接口格式及協(xié)議,設(shè)計(jì)必須考慮一些基本硬件及時(shí)序問(wèn)題。

2018-07-19 13:51:00 6518

6518

ADI宣布推出Power by Linear? ADM1266 Super Sequencer? 超級(jí)時(shí)序控制器,這是一款高度可編程器件,可對(duì)多達(dá)17個(gè)電源進(jìn)行監(jiān)控、時(shí)序控制和裕量調(diào)節(jié)。對(duì)于供電軌數(shù)量較多的情況,可用專(zhuān)有的雙線式器件間總線同步操作16個(gè)ADM1266。

2018-07-23 15:16:00 2405

2405 15.3 全差分放大器 — FDA的穩(wěn)定性和相位裕量

2018-08-02 00:11:00 9932

9932

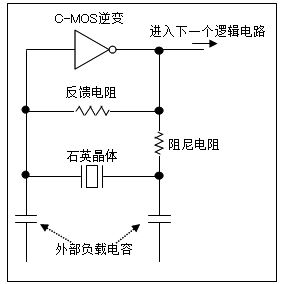

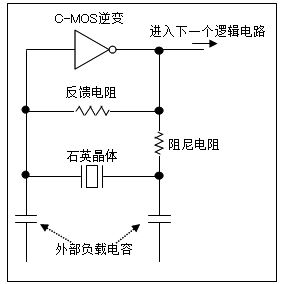

振蕩裕量是指振蕩停止的裕量,這是振蕩電路中最重要的術(shù)語(yǔ)。該裕量是以晶體諧振器電阻為基礎(chǔ)的比值,表明振蕩電路放大能力的大小。

2018-10-23 17:15:51 6821

6821 建立時(shí)間;保持時(shí)間;建立時(shí)間裕量;保持時(shí)間裕量

2018-12-01 08:20:57 4312

4312

因高速問(wèn)題產(chǎn)生的信號(hào)過(guò)沖、下沖、反射、振鈴、串?dāng)_等將嚴(yán)重影響系統(tǒng)的正常時(shí)序,系統(tǒng)時(shí)序余量的減少迫使人們關(guān)注影響數(shù)字波形時(shí)序和質(zhì)量的各種現(xiàn)象。由于速度的提高使時(shí)序變得苛刻時(shí),無(wú)論事先對(duì)系統(tǒng)原理理解得多么透徹,任何忽略和簡(jiǎn)化都可能給系統(tǒng)帶來(lái)嚴(yán)重的后果。

2019-06-03 15:18:15 1091

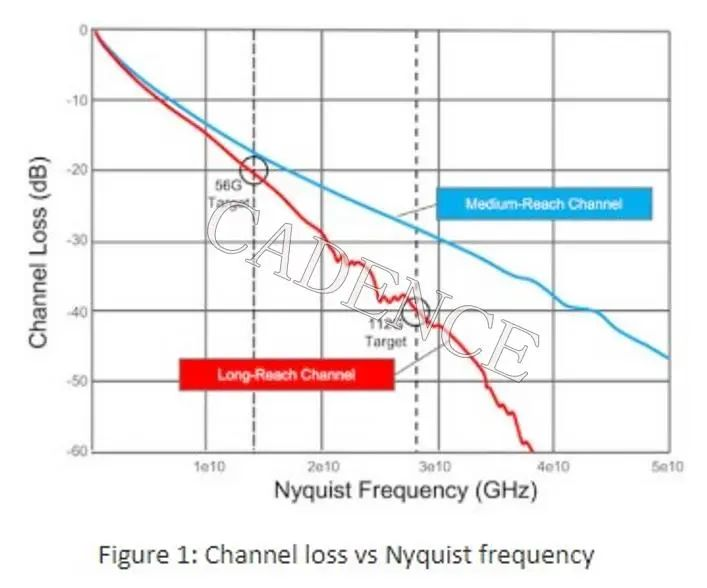

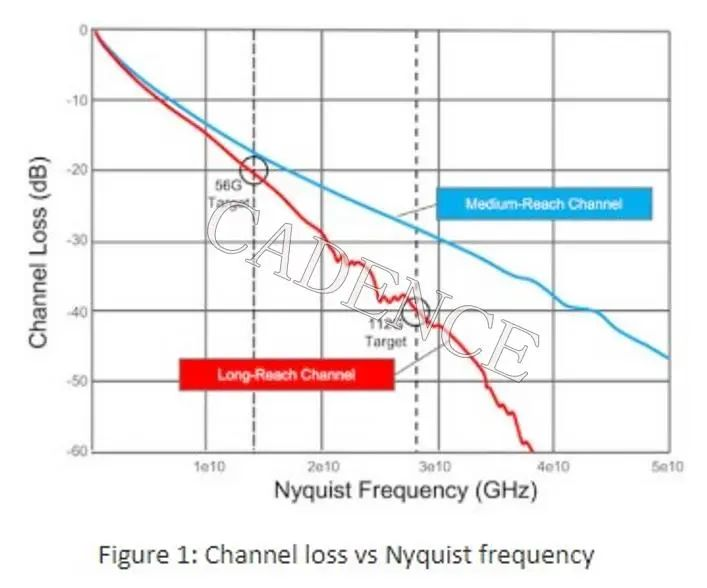

1091 優(yōu)化高速連接的關(guān)鍵是確保最小的信號(hào)丟失量。一旦識(shí)別出連接的帶寬,就可以進(jìn)一步探索s參數(shù)以完理解連接的本質(zhì)。

2020-05-29 10:37:15 1328

1328 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的時(shí)序分析的優(yōu)化策略詳細(xì)說(shuō)明。

2021-01-14 16:03:59 17

17 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的時(shí)序分析的優(yōu)化策略詳細(xì)說(shuō)明。

2021-01-14 16:03:59 19

19 方法,能夠有效減少時(shí)序路徑問(wèn)題分析所需工作量。 時(shí)序路徑問(wèn)題分析定義為通過(guò)調(diào)查一條或多條具有負(fù)裕量的時(shí)序路徑來(lái)判斷達(dá)成時(shí)序收斂的方法。當(dāng)設(shè)計(jì)無(wú)法達(dá)成時(shí)序收斂時(shí),作為分析步驟的第一步,不應(yīng)對(duì)個(gè)別時(shí)序路徑進(jìn)行詳細(xì)時(shí)序分

2021-05-19 11:25:47 3923

3923

。 WNS 代表最差負(fù)時(shí)序裕量 (Worst Negative Slack) TNS 代表總的負(fù)時(shí)序裕量 (Total Negative Slack),也就是負(fù)時(shí)序裕量路徑之和。 WHS 代表最差保持時(shí)序裕

2021-10-21 14:32:35 29249

29249

高速電路信號(hào)完整性分析與設(shè)計(jì)—時(shí)序計(jì)算

2022-02-10 17:16:41 0

0 1、如何降低功耗?

(1) 優(yōu)化方向:

組合邏輯+時(shí)序邏輯+存儲(chǔ)

(2) 組合邏輯:

??(a)通過(guò)算法優(yōu)化的方式減少門(mén)電路

??(b)模塊復(fù)用、資源共享

(3) 時(shí)序邏輯:

??(a)盡量減少無(wú)用

2022-02-11 15:30:36 2

2 時(shí)間裕量包括建立時(shí)間裕量和保持時(shí)間裕量(setup slack和hold slack)。從字面上理解,所謂“裕量”即富余的、多出的。什么意思呢?即保持最低要求的建立時(shí)間或保持時(shí)間所多出的時(shí)間,那么“裕量”越多,意味著時(shí)序約束越寬松。

2022-08-04 17:45:04 1079

1079 Interline CCD 圖像傳感器的垂直時(shí)序優(yōu)化

2022-11-15 20:36:34 3

3 本文介紹了在低功耗系統(tǒng)中降低功耗同時(shí)保持測(cè)量和監(jiān)控應(yīng)用所需的精度的時(shí)序因素和解決方案。它解釋了當(dāng)所選ADC是逐次逼近寄存器(SAR)ADC時(shí)影響時(shí)序的因素。對(duì)于Σ-Δ(∑-Δ)架構(gòu),時(shí)序考慮因素有所不同(請(qǐng)參閱本系列文章的第1部分)。本文探討了模擬前端時(shí)序、ADC時(shí)序和數(shù)字接口時(shí)序中的信號(hào)鏈考慮因素。

2022-12-13 11:20:18 2663

2663

LVDS解串器的偏斜裕量是其抖動(dòng)容限的指標(biāo)。應(yīng)用筆記3821:4通道(3個(gè)數(shù)據(jù)通道加時(shí)鐘通道)LVDS串行器/解串器的偏斜裕量測(cè)量展示了一種利用串行器和LVDS互連來(lái)測(cè)量偏斜裕量的方法。本應(yīng)用筆記描述了如何僅使用解串器測(cè)量偏斜裕量。概述的過(guò)程幾乎可用于任何LVDS解串器。

2023-01-10 09:20:05 1496

1496

達(dá)拉斯半導(dǎo)體的DS80C320處理器由于吞吐量的提高,提供了廣泛的新應(yīng)用機(jī)會(huì)。然而,速度的提高還需要注意與處理器接口的內(nèi)存的時(shí)序要求。本應(yīng)用筆記確定了與存儲(chǔ)器接口相關(guān)的關(guān)鍵時(shí)序路徑,并確定了各種CPU晶體頻率所需的存儲(chǔ)器速度。

2023-01-10 10:18:34 2541

2541

脈寬調(diào)制(PWM)裕量調(diào)節(jié)是一種調(diào)節(jié)電源輸出電壓的簡(jiǎn)單技術(shù)。本應(yīng)用筆記討論了PWM對(duì)電源輸出電壓噪聲的影響、PWM的使能和禁用以及PWM低通濾波器的影響。本文使用MAX34451系統(tǒng)管理器和MAX15041評(píng)估(EV)板。

2023-01-13 14:35:52 1512

1512

和增加系統(tǒng)熱負(fù)荷的問(wèn)題。為了盡量減少這些問(wèn)題,LDO可以在輸入和輸出電壓之間的較小差值(裕量電壓)下工作。本文討論低裕量電壓操作對(duì)電源抑制和總輸出噪聲的影響。

2023-02-03 16:30:51 2231

2231

時(shí)間裕量包括建立時(shí)間裕量和保持時(shí)間裕量(setup slack和hold slack)。從字面上理解,所謂“裕量”即富余的、多出的。

2023-02-06 11:06:03 793

793 LTM4673具有雙線式串行接口,可對(duì)輸出進(jìn)行精確地裕量調(diào)節(jié)、微調(diào)和可編程上電和關(guān)斷時(shí)序控制。

2023-02-07 14:53:27 546

546 本應(yīng)用筆記介紹了與DS80C320以外的Maxim高速微控制器的外部存儲(chǔ)器接口。使用這些微控制器的系統(tǒng)設(shè)計(jì)人員必須了解不同器件系列的多路復(fù)用地址/數(shù)據(jù)鎖存要求和鎖存參數(shù)。討論了EPROM和SRAM參數(shù),以確保微控制器和外部器件之間的正確匹配。

2023-03-01 13:56:28 1792

1792

? ? 1、時(shí)序錯(cuò)誤的影響 ? ? ? 一個(gè)設(shè)計(jì)的時(shí)序報(bào)告中,design run 時(shí)序有紅色,裕量(slack)為負(fù)數(shù)時(shí),表示時(shí)序約束出現(xiàn)違例,雖然個(gè)別違例不代表你的工程就有致命的問(wèn)題,但是這是一

2023-03-17 03:25:03 2014

2014 本應(yīng)用筆記解釋了將DC-DC轉(zhuǎn)換器連接至DS4404 4通道可調(diào)電流DAC(或DS4402,2通道版本)是多么容易增加裕量調(diào)節(jié)功能。

2023-04-08 11:43:25 1804

1804

向量和動(dòng)態(tài)仿真 。本文將介紹靜態(tài)時(shí)序分析的基本概念和方法,包括時(shí)序約束,時(shí)序路徑,時(shí)序裕量,setup檢查和hold檢查等。 時(shí)序路徑 同步電路設(shè)計(jì)中,時(shí)序是一個(gè)主要的考慮因素,它影響了電路的性能和功能。為了驗(yàn)證電路是否能在最

2023-06-28 09:38:57 2402

2402

電子發(fā)燒友網(wǎng)站提供《嵌入式系統(tǒng)外圍接口的時(shí)序分析與電路設(shè)計(jì).pdf》資料免費(fèi)下載

2023-10-09 16:50:13 1

1 振蕩裕量是指振蕩停止的裕量,這是振蕩電路中最重要的術(shù)語(yǔ)。

2023-10-12 09:50:02 2403

2403

相位與輸入相位之間的差距。在設(shè)計(jì)放大電路時(shí),我們需要對(duì)閉合速率與相位裕量進(jìn)行分析和優(yōu)化,以達(dá)到最佳性能。 在傳統(tǒng)的電路設(shè)計(jì)中,通常需要進(jìn)行實(shí)驗(yàn)來(lái)獲得閉合速率與相位裕量。但隨著現(xiàn)代電路仿真技術(shù)的發(fā)展,我們可以使用開(kāi)環(huán)

2023-10-29 11:29:50 1390

1390 相位裕度是什么?相位裕度多少合適? 相位裕度是衡量系統(tǒng)穩(wěn)定性的一個(gè)重要指標(biāo),它描述的是系統(tǒng)對(duì)相位變化的容忍程度,通常用于評(píng)估控制系統(tǒng)的穩(wěn)定性和性能。相位裕度的具體定義是,系統(tǒng)在相位截?cái)囝l率處相位滯后

2023-10-31 10:33:18 9402

9402 【避坑指南】電容耐壓降額裕量不合理導(dǎo)致電容頻繁被擊穿

2023-11-23 09:04:45 3356

3356

高速 112G 設(shè)計(jì)和通道運(yùn)行裕度

2023-12-05 14:24:34 1632

1632

過(guò)沖與相位裕量

2023-12-08 17:22:40 1191

1191

電子發(fā)燒友網(wǎng)站提供《LDO的運(yùn)行困境:低裕量和最小負(fù)載.pdf》資料免費(fèi)下載

2023-11-24 09:13:50 0

0 電子發(fā)燒友網(wǎng)站提供《高速ADC與FPGA的LVDS數(shù)據(jù)接口中避免時(shí)序誤差的設(shè)計(jì)考慮.pdf》資料免費(fèi)下載

2024-10-15 09:50:32 8

8

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論