時鐘是整個電路最重要、最特殊的信號,系統內大部分器件的動作都是在時鐘的跳變沿上進行, 這就要求時鐘信號時延差要非常小, 否則就可能造成時序邏輯狀態出錯。

2020-06-26 10:37:00 6144

6144

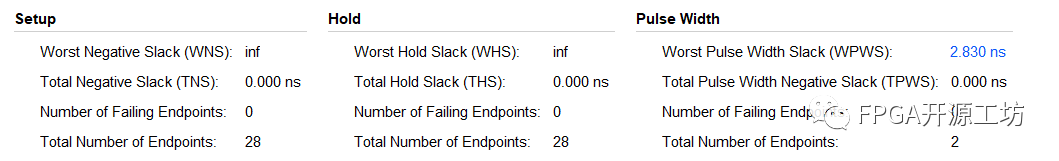

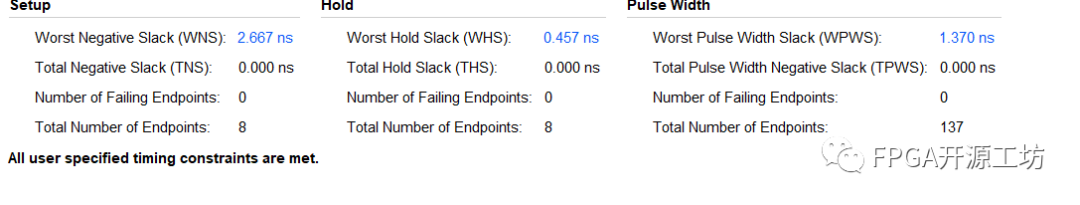

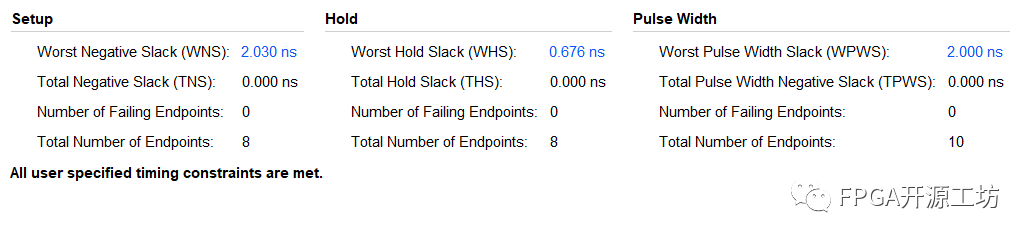

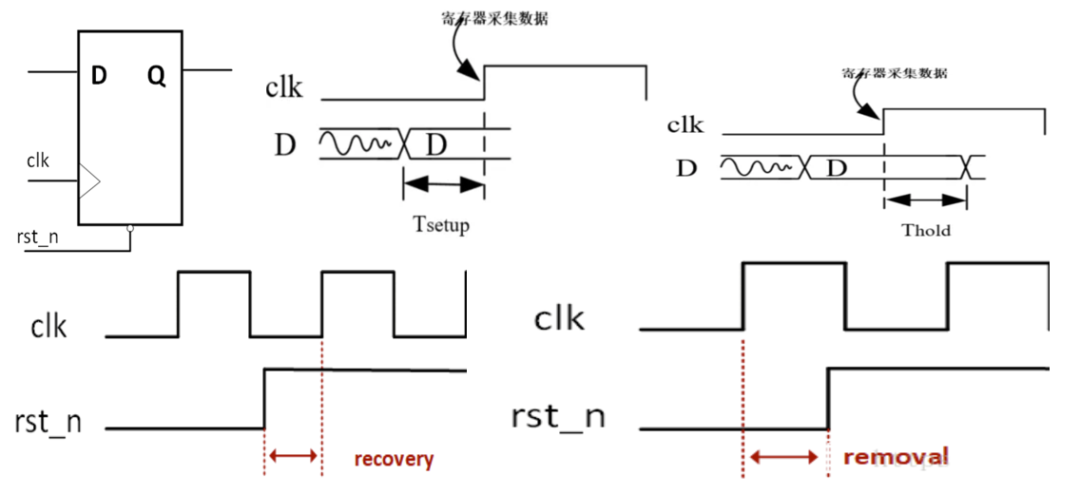

靜態時序分析包括建立時間分析和保持時間分析。建立時間設置不正確可以通過降低芯片工作頻率解決,保持時間設置不正確芯片無法正常工作。

2022-08-22 10:38:24 5380

5380 建立時間(setup time)和保持時間(hold time)是時序分析中最重要的概念之一,深入理解建立時間和保持時間是進行時序分析的基礎。

2023-06-21 10:44:01 2768

2768

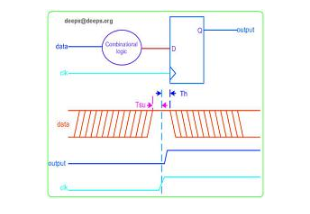

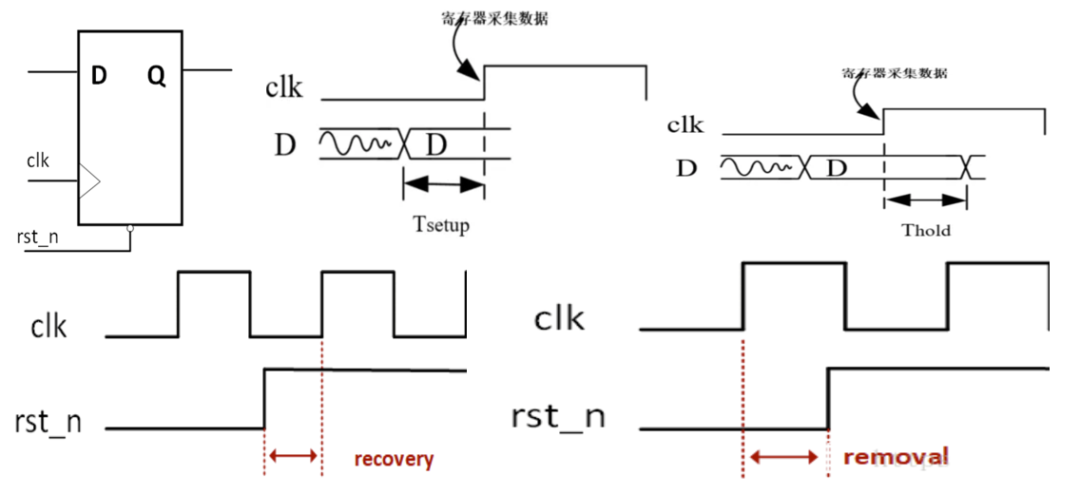

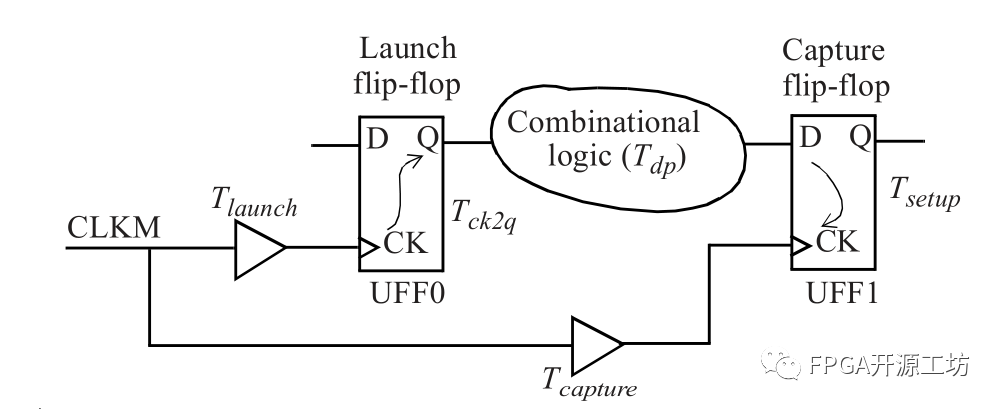

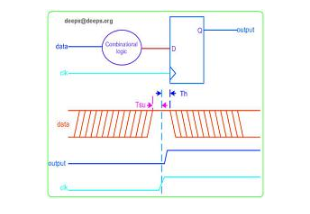

時序分析本質上就是一種時序檢查,目的是檢查設計中所有的D觸發器是否能夠正常工作,也就是檢查D觸發器的同步端口(數據輸入端口)的變化是否滿足建立時間要求(Setup)和保持時間要求(Hold);檢查D

2023-07-14 10:48:19 5776

5776

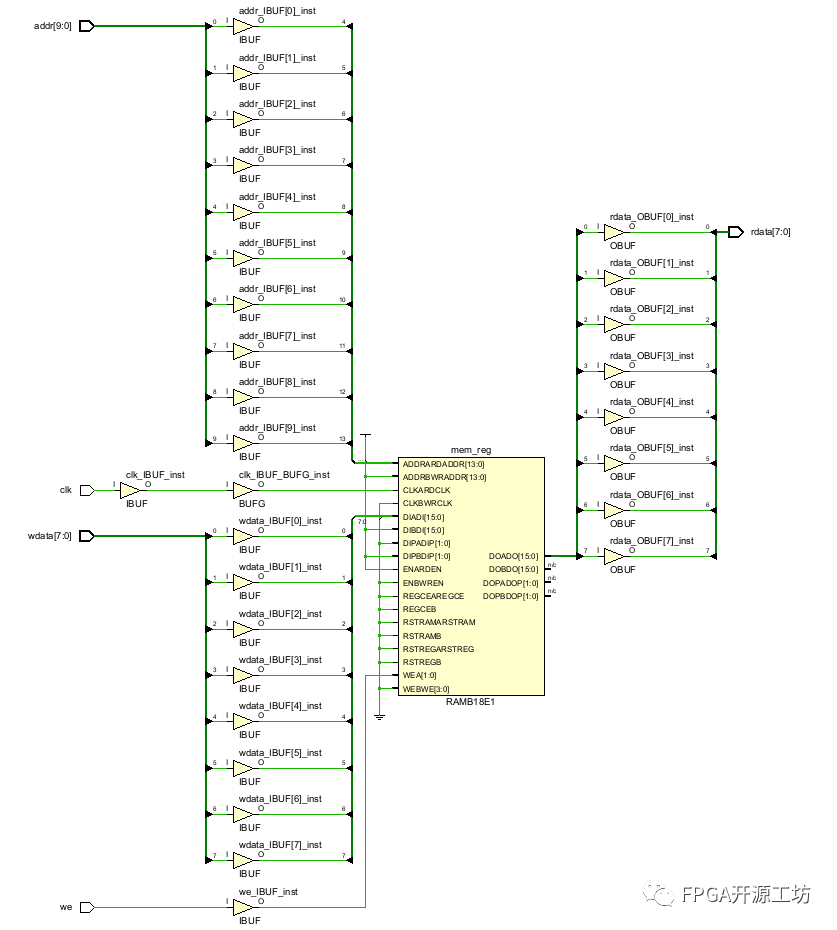

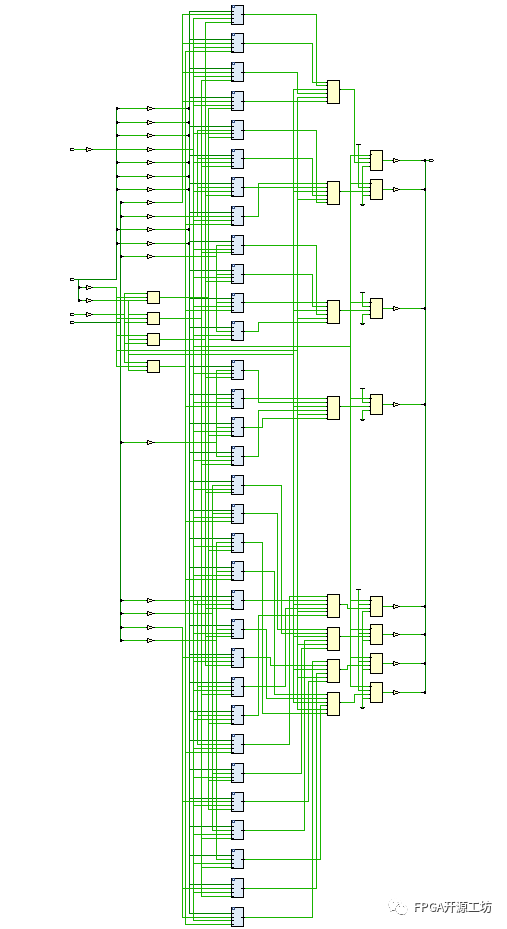

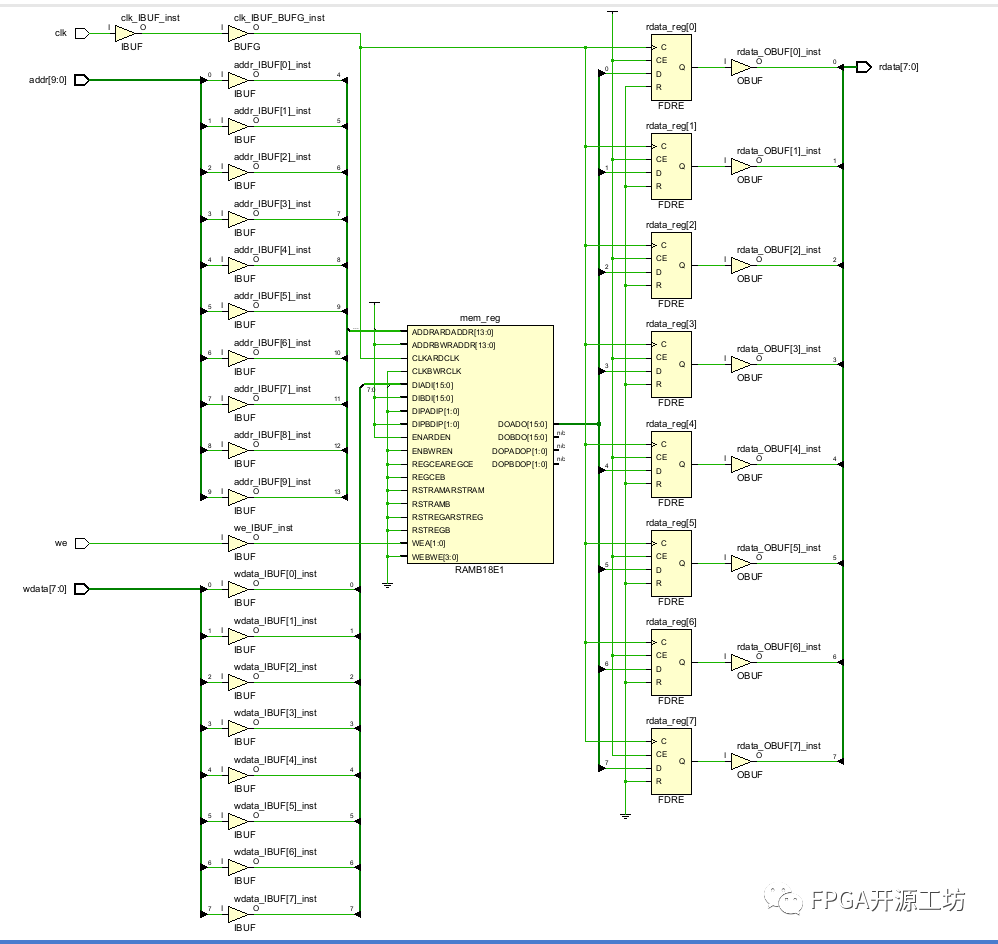

FPGA中時序約束是設計的關鍵點之一,準確的時鐘約束有利于代碼功能的完整呈現。進行時序約束,讓軟件布局布線后的電路能夠滿足使用的要求。

2023-08-14 17:49:55 2211

2211

我理解這個D觸發正常運轉要滿足四個約束,第一個是建立時間,第二個是保持時間,第三個是對于最后一個傳輸門的關斷時間的控制,第四個是[時鐘周期]() 約束。

2023-12-04 15:44:02 3182

3182

是 FPGA/ASIC 時序定義的基礎概念。后面要講到的其它時序約束都是建立在周期約束的基礎上的,很多其它時序公式,可以用周期公式推導。周期約束是一個基本時序和綜合約束,它附加在時鐘網線上,時序分析工具根據

2024-06-17 17:07:28

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間

2023-11-15 17:41:10

+ 組合邏輯延時Tlogic + FPGA內部的網絡延時Tnet + 寄存器時鐘建立時間Tsu –時鐘偏斜TclkskewFmax = 1 / Tclk在QuartusII時序分析后很容易看到Fmax

2018-07-03 02:11:23

+ 組合邏輯延時Tlogic + FPGA內部的網絡延時Tnet + 寄存器時鐘建立時間Tsu –時鐘偏斜TclkskewFmax = 1 / Tclk在QuartusII時序分析后很容易看到Fmax

2018-07-09 09:16:13

的幾個基本的重要的時序分析參數:fMAX(最大時鐘頻率):在不違背內部建立時間tsu和保持時間th要求下可以達到的最大時鐘頻率;tSU(時鐘建立時間):在寄存器的時鐘信號已經在時鐘引腳建立之前,經由數據或者使能輸入而進入寄存器的數據必須在輸入引腳出現的時間長度;(equation:tsu

2012-04-09 09:41:41

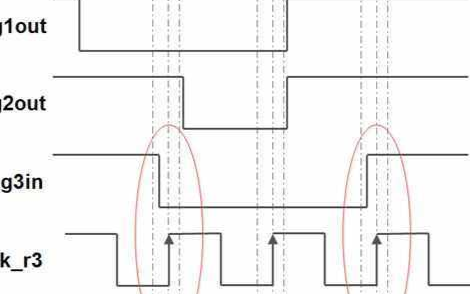

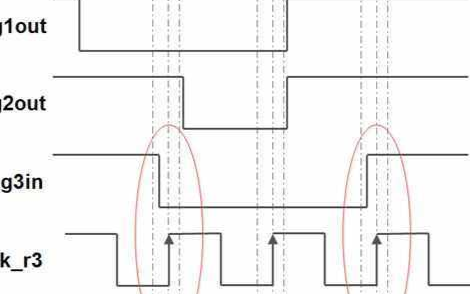

建立時間和保持時間本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 在這個波形中,我們看到clk_r3的前后

2015-07-17 12:02:10

VGA驅動接口時序設計之4建立和保持時間分析本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt下面我們可以簡單

2015-08-02 19:26:19

們最壞的情況進行分析,然后得出相應的時序余量。左圖的豎線條是時鐘的latch沿,我們看在它前面9.713ns數據都是保持穩定的,完全滿足ADV7123芯片datasheet上的0.2ns建立時間要求;右圖

2015-08-10 15:03:08

的寄存器同樣有建立時間Tsu和保持時間Th要求,也必須在整個路徑的傳輸時序中予以考慮。(特權同學,版權所有) 圖8.48 CMOS Sensor和FPGA連接的寄存器模型另外,從前面的分析,我們得到

2015-08-14 11:24:01

所示,在報告中,數據的建立時間有9~13ns的余量,而保持時間也都有7~11ns的余量,可謂余量充足。(特權同學,版權所有)圖8.57 setup時序報告圖8.58 hold時序報告另外,我們也可以

2015-08-19 21:58:55

FPGA設計中的時序分析及異步設計注意事項建立時間(setup time):是指在觸發器的時鐘信號上升沿到來以前,數據穩定不變的時間,如果建立時間不夠,數據將不能在這個時鐘上升沿被打入觸發器;保持

2009-12-07 10:14:33

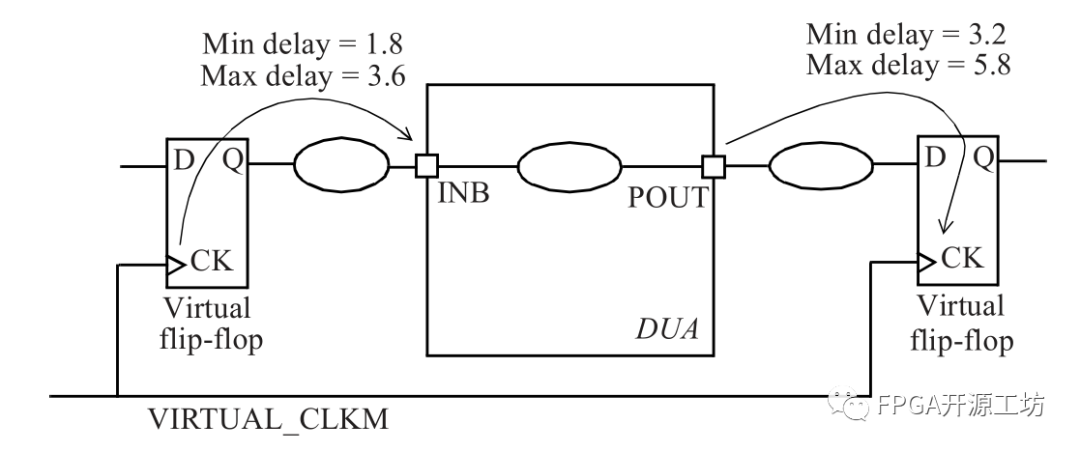

整個系統進行時序分析,所以FPGA需要作為一個整體分析,其中包括FPGA的建立時間、保持時間以及傳輸延時。傳統的建立時間、保持時間以及傳輸延時都是針對寄存器形式的分析。但是針對整個系統FPGA的建立時間

2012-04-25 15:42:03

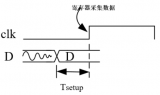

(latch edge):數據鎖存的時鐘邊沿,也是靜態時序分析的終點。3.Clock Setup Time (Tsu) 建立時間(Tsu):是指在時鐘沿到來之前數據從不穩定到穩定所需的時間,如果建立

2012-01-11 11:43:06

如圖,建立時間和保持時間都是針對的時鐘沿,如圖所示,時鐘沿有一個上升的過程,圖中虛線與clk上升沿的交點是什么?幅值的50%?還是低電平(低于2.5V)往高電平(高于2.5V)跳轉的那個點?

2018-11-29 00:20:02

本帖最后由 虎子哥 于 2015-3-12 21:24 編輯

建立時間(Setup Time):是指在觸發器的時鐘信號上升沿到來以前,數據穩定不變的時間,如果建立時間不夠,數據將不能在這個時鐘

2015-03-10 23:19:03

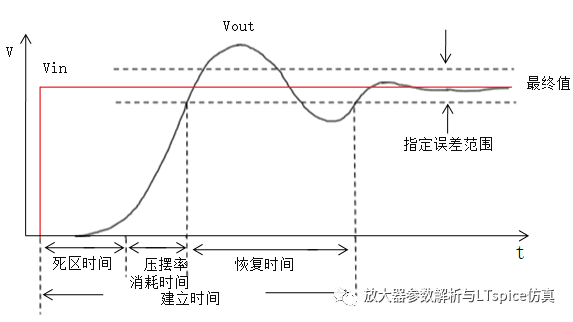

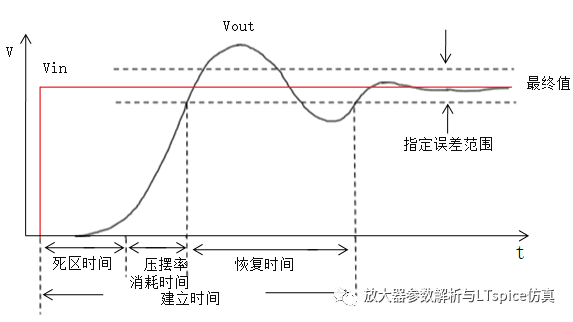

作者: TI專家 Bruce Trump翻譯: TI信號鏈工程師 Michael Huang (黃翔) 建立時間是運放階躍響應進入和停留在最終值的特定誤差范圍內的所需時間。它在一些應用中十分重要

2018-09-20 16:32:36

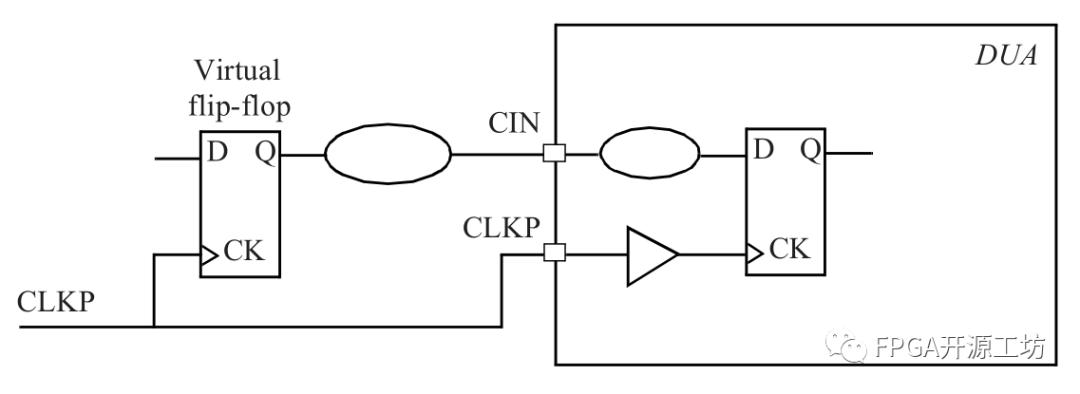

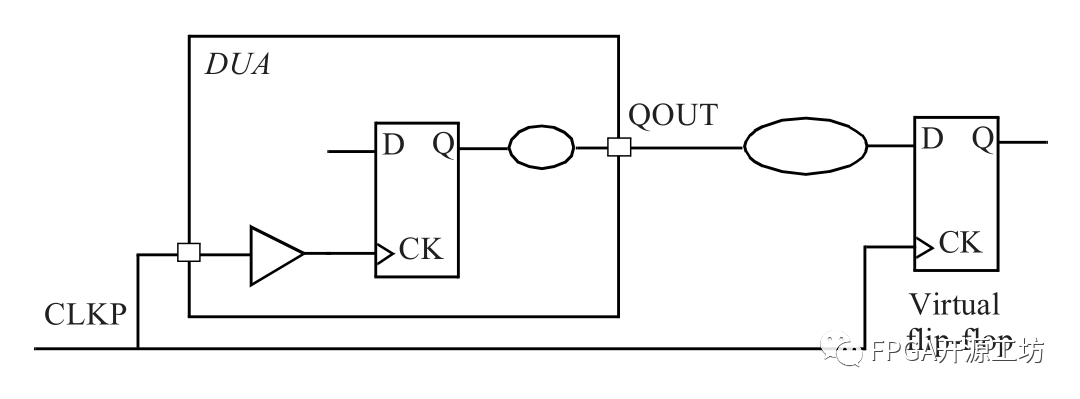

約束中的注意事項。 一、時序分析中的重要概念 在數字系統中有兩個非常重要的概念:建立時間和保持時間,其示意圖如圖1所示。一個數字系統能否正常工作跟這兩個概念密切相關。只有建立時間和保持時間都同時得到

2020-08-16 07:25:02

ADC時延和建立時間的區別是什么?以及ADC時延和建立時間將會如何影響您的應用電路?

2021-04-12 07:19:18

中建立時間曲線,±20V輸出,如果按照數據手冊中4V/uS爬升速率計算,0到20V跳變時間為5uS,從以上兩圖頁可以看出,信號在5uS內達到設定值20V,該時間也小于建立時間典型值12uS。

請問如何理解數據手冊中的12uS建立時間這個參數呢

2024-12-09 08:33:21

有沒有人遇到在DC綜合后分析建立時間時序,關鍵路徑時序違例是因為起始點是在時鐘的下降沿開始驅動的,但是設計中都是時鐘上升沿觸發的。在線等待各位大牛解惑!很急 求大神幫忙!

2015-01-04 15:17:16

在DQ的中間位置,這樣建立時間或者保持時間的裕量就會變小。先簡單的來看一張圖圖9 延時偏差對時序的影響上圖中,T_vb與T_va表示的是主控芯片在輸出數據時時鐘與數據之間的時序參數。在理想情況下,時鐘

2018-09-20 10:29:55

。和上面分析時鐘與地址信號一樣,如果DQ與DQS之間等長做的不好,DQS的時鐘邊沿就不會保持在DQ的中間位置,這樣建立時間或者保持時間的裕量就會變小。 先簡單的來看一張圖 圖9 延時偏差對時序

2018-09-20 10:59:44

我的PGA281增益由1變128時,建立時間Settling time過長有800uS左右(增益切換后延時1ms也沒用),可數據手冊明明是40us

2024-08-22 06:14:39

PLL jitter 對建立時間和保持時間有什么樣的影響?哪位大神給解答下

2015-10-30 11:16:30

VGA驅動接口時序設計之4建立和保持時間分析本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 下面我們可以

2019-04-10 06:33:34

什么是同步邏輯和異步邏輯?同步電路和異步電路的區別在哪?為什么觸發器要滿足建立時間和保持時間?

2021-09-28 08:51:33

什么是同步邏輯和異步邏輯?同步電路和異步電路的區別在哪?為什么觸發器要滿足建立時間和保持時間?什么是亞穩態?為什么兩級觸發器可以防止亞穩態傳播?

2021-08-09 06:14:00

什么叫建立時間,保持時間,和恢復時間

2017-04-08 16:52:35

1、FPGA中的時序約束--從原理到實例 基本概念 建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。 電路中的建立時間和保持時間其實跟生活中的紅綠燈很像

2022-11-15 15:19:27

。這種方法把準確性和精確度建立在波形生成器和采樣保持電路的相對速度上。 受測器件的步進輸入 本文中,建立時間是指使用某個理想步進輸入,到受測器件(DUT)進入并維持在某個規定誤差范圍(終值對稱)內

2012-07-30 17:36:20

關于數字IC的建立時間以及保持時間你想知道的都在這

2021-09-18 07:24:40

多路復用器輸入端的建立瞬變(由多路復用器輸出端的大尺度開關瞬變引起)導致需要較長采集時間,使得多通道數據采集系統的整體吞吐量顯著降低。然后,文中將著重闡述使輸入建立時間最小化以及提高數據吞吐量和系統

2018-10-29 17:06:48

的建立時間和保持時間。 1、建立時間的分析如圖 7所示,建立時間的分析是以第一個launch Edge為基準,在Latch Edge查看結果。建立時間的裕量(T為時鐘周期):Setup Stack

2018-04-03 11:19:08

密度。本文將說明多路復用器輸入端的建立瞬變(由多路復用器輸出端的大尺度開關瞬變引起)導致需要較長采集時間,使得多通道數據采集系統的整體吞吐量顯著降低。然后,本文將著重闡述使輸入建立時間最小化以及提高數據吞吐量和系統效率所需的設計權衡。

2020-12-28 07:30:52

建立時間測量的采樣保持方法測試裝置存在哪些局限性?

2021-04-09 06:08:05

建立時間(Setup Time)是指觸發器的時鐘信號上升沿到來之前,數據保持穩定不變的時間。 輸入信號應該提前時鐘上升沿(如上升沿有效)Tsu時間到達芯片,這個 Tsu就是建立時間。如果不滿足建立時間

2021-07-26 07:36:01

請問,對于觸發器的時鐘信號,建立時間和保持時間有要求嗎?剛看到一個門控時鐘產生毛刺的反例,(如下圖)想到了這個問題。若此時鐘信號毛刺極小,有沒有可能被觸發器忽略呢?為什么呢?如果有可能小到什么程度會被忽略呢?

2012-01-27 18:44:58

上引起的差異,為了更好地說明這些Skew對時序的具體影響,下面我們還是通過時序圖分析的方法來計算一下源同步時鐘系統中信號的建立時間裕量和保持時間裕量。首先考慮建立時間裕量:和普通時序分析的方法一下,我們也是從

2014-12-30 14:05:08

參考運放的datasheet。但如果是兩級運算放大器電路呢,此時總的建立時間又該如何估算?同樣以ADA4897組成兩級運算放大電路為例說明,級聯后總的0.01%建立時間該是多少?可能的答案:(1)總

2018-11-13 15:08:15

可以參考運放的datasheet。

但如果是兩級運算放大器電路呢,此時總的建立時間又該如何估算?

同樣以ADA4897組成兩級運算放大電路為例說明,級聯后總的0.01%建立時間該是多少?

可能

2023-11-27 06:54:56

16444_[。只有降低SPI頻率到20MHz才ok。(2)問題分析:通過示波器測量,發現DM9051的cs建立時間和保持時間很緊張,其它信號質量和時序ok,需要增加cs的建立時間和保持時間來試試。(3

2023-02-15 06:55:16

)問題分析:

通過示波器測量,發現DM9051的cs建立時間和保持時間很緊張,其它信號質量和時序ok,需要增加cs的建立時間和保持時間來試試。

(3)問題解決:

根據

2024-06-18 07:31:22

T2max,最小為T2min。問,觸發器D2的建立時間T3和保持時間應滿足什么條件

2019-09-09 17:19:55

在PCB走線的延時,因此上圖只是一個理想過程,即沒有考慮PCB走線的延時,而我們的時序分析工具確實將其考慮在內了,所以,我們的FPGA建立時間,除了包括數據保持穩定的時間外,還應加上這段走線延時的時間

2015-03-31 10:35:18

的FPGA器件,時鐘偏斜相對固定,所以我們可以改變的就是Tco,怎么改變呢,就是添加我們的時序約束,讓綜合工具按照我們的要求尋找符合我們約束的路徑,從而滿足建立保持時間的要求。二、輸入輸出模型以及I/O

2015-03-31 10:20:00

計算開關電容ADC的建立時間:很多C8051F器件具有片內模/數轉換器ADC這些ADC使用一個采樣電容該電容被充電到輸入信號電壓由SAR邏輯進行數據轉換由于存在ADC采樣電容輸入阻抗和外部輸

2008-10-30 18:25:08 24

24 該文簡要討論了環路性能(建立時間,相位噪聲和雜散信號)和環路參數(帶寬,相位裕度等)的相互關系。提出并分析了一種自適應的具有快速建立時間的鎖相環結構及其關鍵模塊(鑒相

2010-04-23 08:33:53 20

20 基本概念:線與邏輯、鎖存器、緩沖器、建立時間、緩沖時間

基本概念:線與邏輯、鎖存器、緩沖器、建立時間、緩沖時間

標簽/分類:

2007-08-21 15:17:27 1607

1607 時延和建立時間setup在ADC電路中的區別:對于大多數 ADC 用戶來說,“時延”和“建立時間”這兩個術語有時可以互換。但對于 ADC 設計人員而言,他們非常清楚

2007-11-22 23:33:07 1940

1940 為實現高速DAC的最佳性能,必須滿足一定的建立和保持時間要求。在200 MSPS至250 MSPS的時鐘速率下,FPGA/ASIC/DAC的全部時序預算并不是一件小事。客戶若要完成時序驗證,必須清楚列出并

2011-11-24 14:20:35 33

33 本文將介紹一種新方法,其經過證明可以有效地完成這些測量工作。它是一種相對低成本、簡單的建立時間測量方法。這種方法把準確性和精確度建立在波形生成器和采樣保持電路的相

2012-07-27 10:25:16 1810

1810

建立時間和保持時間貫穿了整個時序分析過程。只要涉及到同步時序電路,那么必然有上升沿、下降沿采樣,那么無法避免setup-time 和 hold-time這兩個概念。 1. 什么是setup-time

2017-02-08 14:48:11 7008

7008 今天,我們將介紹兩種相關的動態參數 — 壓擺率與建立時間。如欲了解更多有關靜態和動態參數的不同之處,敬請參閱本文。

2018-07-10 16:14:00 6586

6586

建立時間;保持時間;建立時間裕量;保持時間裕量

2018-12-01 08:20:57 4312

4312

FPGA中的時序問題是一個比較重要的問題,時序違例,尤其喜歡在資源利用率較高、時鐘頻率較高或者是位寬較寬的情況下出現。建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

2019-12-23 07:02:00 4742

4742

FPGA中的時序問題是一個比較重要的問題,時序違例,尤其喜歡在資源利用率較高、時鐘頻率較高或者是位寬較寬的情況下出現。建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

2019-12-23 07:01:00 2671

2671

時鐘是FPGA設計中最重要的信號,FPGA系統內大部分器件的動作都是在時鐘的上升沿或者下降沿進行。

2019-06-19 15:04:17 6698

6698

首先來看什么是時序約束,泛泛來說,就是我們告訴軟件(Vivado、ISE等)從哪個pin輸入信號,輸入信號要延遲多長時間,時鐘周期是多少,讓軟件PAR(Place and Route)后的電路能夠

2020-01-28 17:34:00 4750

4750

建立和保持時間的話,那么DFF將不能正確地采樣到數據,將會出現metastability 的情況。如果數據信號在時鐘沿觸發前后持續的時間均超過建立和保持時間,那么超過量就分別被稱為建立時間裕量和保持時間裕量。

2020-10-27 16:26:00 11

11 本篇仿真介紹放大器的建立時間,也稱為上升時間。它是高速放大電路、或在SARADC驅動電路設計時,需要謹慎評估的參數。

2021-02-15 16:37:00 7260

7260

AN-359:運算放大器的建立時間

2021-04-29 15:28:46 4

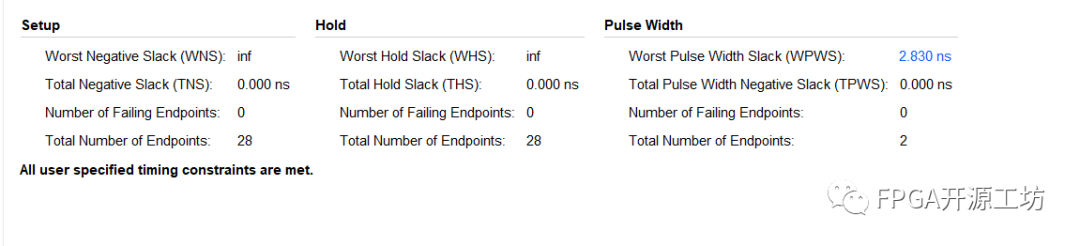

4 時間裕量包括建立時間裕量和保持時間裕量(setup slack和hold slack)。從字面上理解,所謂“裕量”即富余的、多出的。什么意思呢?即保持最低要求的建立時間或保持時間所多出的時間,那么“裕量”越多,意味著時序約束越寬松。

2022-08-04 17:45:04 1079

1079 前言 在上篇文章里《時序分析基本概念(一)——建立時間》,我們向大家介紹了建立時間的基本概念和計算方法。

2022-10-09 11:59:45 5211

5211 對于建立時間和保持時間本文就不再過多敘述,可參考【FPGA】幾種時序問題的常見解決方法-------3,可以說在數字高速信號處理中最基本的概念就是建立時間和保持時間,而我們要做的就是解決亞穩態問題和傳輸穩定問題。

2022-12-13 11:03:58 707

707 時間裕量包括建立時間裕量和保持時間裕量(setup slack和hold slack)。從字面上理解,所謂“裕量”即富余的、多出的。

2023-02-06 11:06:03 793

793 本篇通過仿真介紹放大器的建立時間,也稱為上升時間。它是高速放大電路、或在SAR ADC驅動電路設計時,需要謹慎評估的參數。

2023-02-22 11:29:31 1919

1919

的本質,而且不需要再記復雜的公式了。 我們的分析從下圖開始,下圖是常用的靜態分析結構圖,一開始看不懂公式不要緊,因為我會在后面給以非常簡單的解釋: 這兩個公式是一個非常全面的,準確的關于建立時間和保持時間的公式。

2023-03-14 19:10:03 1476

1476 個風險(時序報告是按照工藝、電壓以及溫度的上下限給出的結果)。當違例數較多,也就意味著設計在實際環境中出現問題的概率也會越大。? ? ? 時間裕量包括建立時間裕量和保持時間裕量(setup slack和hold slack)。從字面上理解,所謂“裕量”即富余的、多出的。什

2023-03-17 03:25:03 2014

2014 時序電路講究建立時間、保持時間需要留有裕量。這也說明了,在電路中信號的順序以及之間的時序關系十分重要。

2023-06-06 11:51:02 5360

5360

運算放大器建立時間是保證數據采集系統性能的關鍵參數。為了實現精確的數據采集,運算放大器輸出必須在A/D轉換器能夠準確數字化數據之前建立。然而,建立時間通常不是一個容易測量的參數。

2023-06-17 10:37:54 1635

1635

??本文主要介紹了建立時間和保持時間。

2023-06-21 14:38:26 4826

4826

在時序電路設計中,建立時間/保持時間可以說是出現頻率最高的幾個詞之一了,人們對其定義已經耳熟能詳,對涉及其的計算(比如檢查時序是否正確,計算最大頻率等)網上也有很多。

2023-06-27 15:43:55 18883

18883

建立時間和保持時間是SOC設計中的兩個重要概念。它們都與時序分析有關,是確保芯片正常工作的關鍵因素。

2023-08-23 09:44:55 1828

1828 信號經過傳輸線到達接收端之后,就牽涉到建立時間和保持時間這兩個時序參數,它們表征了時鐘邊沿觸發前后數據需要在鎖存器的輸入持續時間,是接收器本身的特性。簡而言之,時鐘邊沿觸發前,要求數據必須存在一段時間,這就是器件需要的建立時間;

2023-09-04 15:16:19 1610

1610

文件提到兩種setup/hold測量方式:10% push-up和pass/fail,按照TSMC說法,前者會更樂觀一些,因此如果是采用前者(10% push-up)的測量方式得到建立時間和保持時間,需要十份小心時序裕量是否足夠,最好人為添加margin。

2023-12-05 11:19:38 3630

3630

建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

2024-08-06 11:40:18 2366

2366

電子發燒友App

電子發燒友App

評論