添加約束的目的是為了告訴FPGA你的設(shè)計(jì)指標(biāo)及運(yùn)行情況。在上面的生成約束之后,在Result àxx.sdc中提供約束參考(請注意該文件不能直接添加到工程中,需要熱復(fù)制到別的指定目錄或者新建自己的SDC文件添加到工程)。

2024-04-28 18:36:19 3513

3513

,后者指定了管腳對應(yīng)的電平標(biāo)準(zhǔn)。 在vivado中,使用如下方式在xdc中對管腳進(jìn)行約束。 set_property -dict {PACKAGE_PIN AJ16 IOSTANDARD

2020-10-30 16:08:13 17476

17476

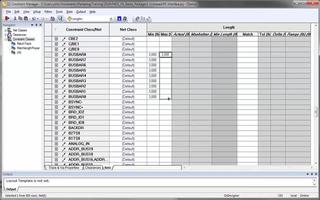

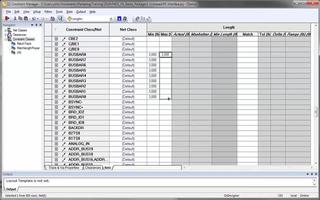

對話框的約束部分下,選擇默認(rèn)約束設(shè)置作為活動約束設(shè)置;包含在Xilinx設(shè)計(jì)約束(XDC)文件中捕獲的設(shè)計(jì)約束的一組文件,可以將其應(yīng)用于設(shè)計(jì)中。兩種類型的設(shè)計(jì)約束是: 1) 物理約束:這些約束定義引腳

2020-11-23 14:16:36 6673

6673

時序約束的目的就是告訴工具當(dāng)前的時序狀態(tài),以讓工具盡量優(yōu)化時序并給出詳細(xì)的分析報(bào)告。一般在行為仿真后、綜合前即創(chuàng)建基本的時序約束。Vivado使用SDC基礎(chǔ)上的XDC腳本以文本形式約束。以下討論如何進(jìn)行最基本時序約束相關(guān)腳本。

2022-03-11 14:39:10 11064

11064 引言:本文我們簡單介紹下Xilinx FPGA管腳物理約束,包括位置(管腳)約束和電氣約束。

2022-07-25 10:13:44 5970

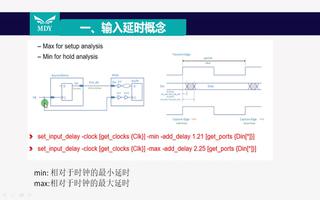

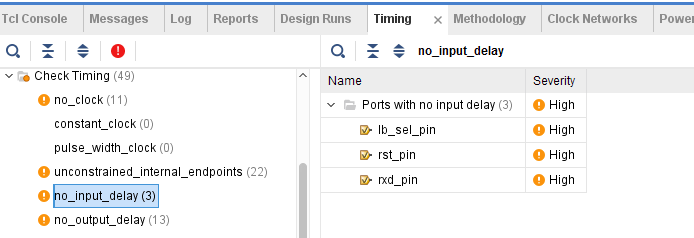

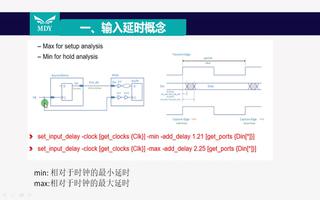

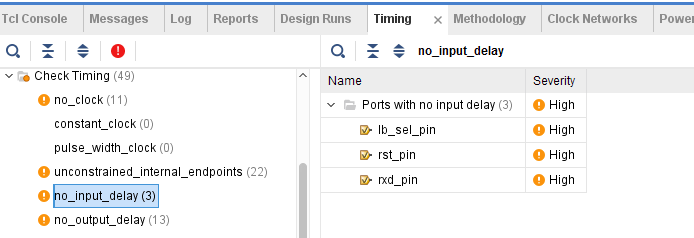

5970 ??set_input_delay屬于時序約束中的IO約束,我之前的時序約束教程中,有一篇關(guān)于set_input_delay的文章,但里面寫的并不是很詳細(xì),今天我們就來詳細(xì)分析一下,這個約束應(yīng)該如何使用。

2022-09-06 09:22:02 2908

2908 在高速系統(tǒng)中FPGA時序約束不止包括內(nèi)部時鐘約束,還應(yīng)包括完整的IO時序約束和時序例外約束才能實(shí)現(xiàn)PCB板級的時序收斂。因此,F(xiàn)PGA時序約束中IO口時序約束也是一個重點(diǎn)。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 2395

2395 在FPGA設(shè)計(jì)中,時序約束的設(shè)置對于電路性能和可靠性都至關(guān)重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時序約束的基礎(chǔ)知識。

2023-06-06 18:27:13 12758

12758

在FPGA設(shè)計(jì)中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 4234

4234 前面講解了時序約束的理論知識FPGA時序約束理論篇,本章講解時序約束實(shí)際使用。

2023-08-14 18:22:14 3030

3030

時鐘周期約束是用于對時鐘周期的約束,屬于時序約束中最重要的約束之一。

2023-08-14 18:25:51 1777

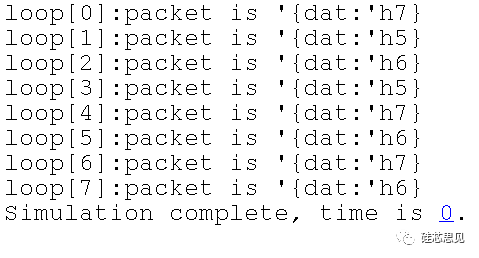

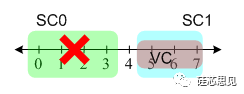

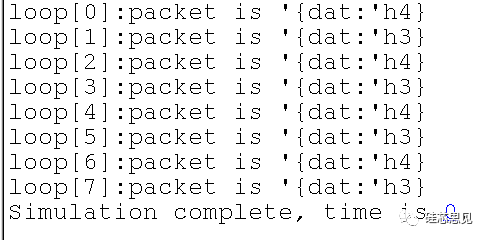

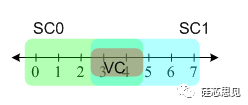

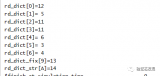

1777 systemverilog constraint中的foreach可以對數(shù)組進(jìn)行遍歷和約束,常用于普通數(shù)組,隊(duì)列或者動態(tài)數(shù)組。

2023-08-21 09:31:07 1872

1872

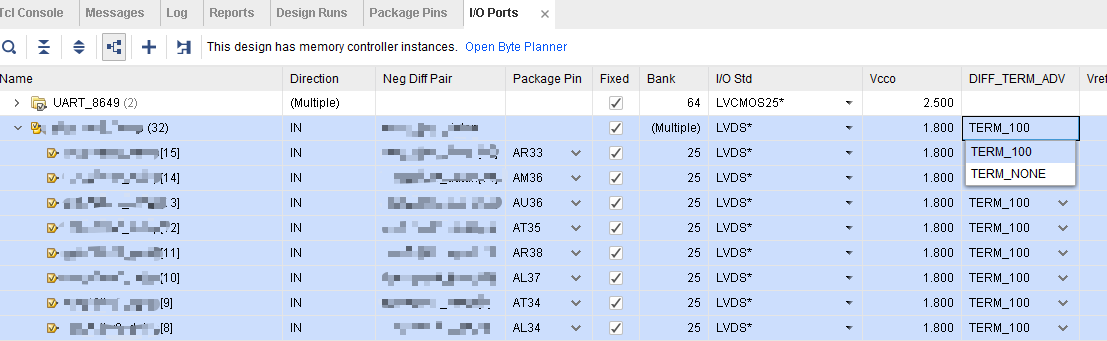

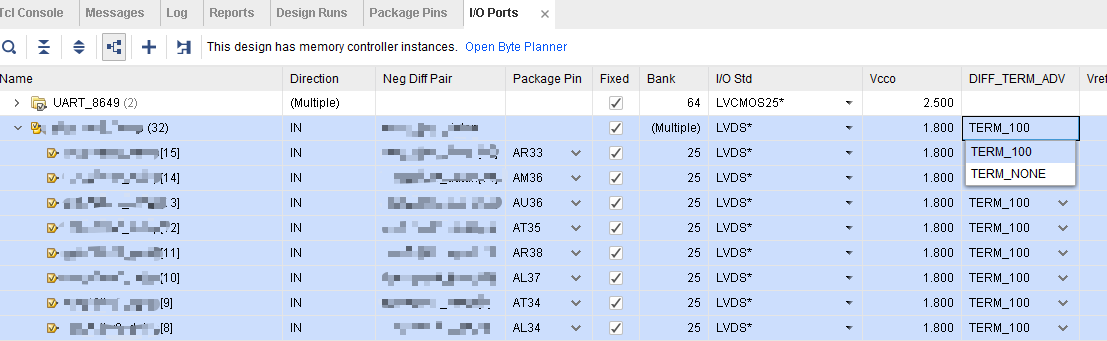

I/O約束(I/O Constraints)包括I/O標(biāo)準(zhǔn)(I/OStandard)約束和I/O位置(I/O location)約束。

2023-11-18 16:42:28 2442

2442

在進(jìn)行布局約束前,通常會對現(xiàn)有設(shè)計(jì)進(jìn)行設(shè)計(jì)實(shí)現(xiàn)(Implementation)編譯。在完成第一次設(shè)計(jì)實(shí)現(xiàn)編譯后,工程設(shè)計(jì)通常會不斷更新迭代,此時對于設(shè)計(jì)中一些固定不變的邏輯,設(shè)計(jì)者希望它們的編譯結(jié)果

2024-01-02 14:13:53 2363

2363

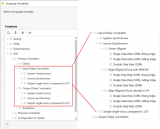

Vivado的時序約束是保存在xdc文件中,添加或創(chuàng)建設(shè)計(jì)的工程源文件后,需要創(chuàng)建xdc文件設(shè)置時序約束。時序約束文件可以直接創(chuàng)建或添加已存在的約束文件,創(chuàng)建約束文件有兩種方式:Constraints Wizard和Edit Timing Constraints,在綜合后或?qū)崿F(xiàn)后都可以進(jìn)行創(chuàng)建。

2025-03-24 09:44:17 4561

4561

,請告知我們對輸入時鐘的約束是足夠的,并且將通過兩個DCM組件轉(zhuǎn)換為DCM輸出clk_int,clk90_int和clk180_int上的新PERIOD約束。我檢查了DCM輸出約束的時序約束用戶指南但是無法獲得多個或更多的示例級聯(lián)DCM謝謝

2020-05-01 15:08:50

在設(shè)計(jì)以太網(wǎng)中繼器時,因?yàn)闆]有配置時鐘約束,導(dǎo)致中繼器工作不正常。后面根據(jù)手冊配置時鐘約束解決了此問題。

2016-10-07 18:51:24

;TNM_NET = "SysCLk";TIMESPEC是一個基本時序相關(guān)約束,TS_xxxxx由關(guān)鍵字TS和用戶定義的xxxx表示,兩者共同構(gòu)成一個時序,可以再約束文件中任意的引用

2015-09-05 21:13:07

我的用戶約束永遠(yuǎn)不會從我第一次輸入用戶約束文件時更新。示例:這是我的新用戶約束文件。NET“CLK”LOC =“P43”| IOSTANDARD = LVTTL;NET“CLK”TNM_NET

2020-03-09 08:43:49

嗨,大家好,據(jù)我所知,OFFSET約束強(qiáng)加于所有輸入PAD。在我的設(shè)計(jì)中,使用了兩個時鐘輸入。因此,PAD上的輸入信號應(yīng)分組為:1.需要OFFSET約束時間值#1,參考時鐘輸入#12.需要

2019-05-29 13:51:12

表示使用 ISE 的文本編輯器編輯約束文件。可以通過選擇 ISE 的菜單項(xiàng) Edit|Preferences,在 Preferences 設(shè)置對話框的 Editor 選項(xiàng)卡中設(shè)定約束編輯工具,如圖

2018-09-29 09:18:05

什么是硬判決和軟判決Viterbi 譯碼算法 ?接收到的符號首先經(jīng)過解調(diào)器判決,輸出0、1 碼,然后再送往譯碼器的形式,稱為硬判決譯碼。即編碼信道的輸出是0、1 的硬判決信息。我們選擇似然概率P

2008-05-30 16:11:37

”;################################################## ##############################物理界面約束#以下約束是正確操作所必需的,并且已經(jīng)過調(diào)整#為此示例設(shè)計(jì)。它們應(yīng)該根據(jù)您的設(shè)計(jì)進(jìn)行修改

2020-06-13 16:00:24

此版只討論時序約束約束理論約束方法約束結(jié)果時鐘約束(Clock Specification): 約束所有時鐘(包括你的設(shè)計(jì)中特有的時鐘)對準(zhǔn)確的時序分析結(jié)果而言是必不可少的。Quartus II

2013-05-16 18:51:50

create_clock -name sysclk -period 10 [get_ports clkin]1. 輸入延遲約束set_input_delay-clock sysclk -max 4

2018-09-21 12:50:15

數(shù)。 set_multicycle_path2 -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]2. 偽路徑約束 存在于設(shè)計(jì)中的拓?fù)浣Y(jié)構(gòu),但沒有起到作用或

2018-09-21 12:55:34

好的時序是設(shè)計(jì)出來的,不是約束出來的時序就是一種關(guān)系,這種關(guān)系的基本概念有哪些?這種關(guān)系需要約束嗎?各自的詳細(xì)情況有哪些?約束的方法有哪些?這些約束可分為幾大類?這種關(guān)系僅僅通過約束來維持嗎?1

2018-08-01 16:45:40

文章目錄1、時鐘約束的概念2、 DC中的時序約束參考文章時間又拖拖拖,隨著追尋DFT的進(jìn)度,DC的進(jìn)度在經(jīng)歷了.dynopsys_dc.setup后,就停滯不前了,接下來本文就來介紹DC的約束篇目

2021-11-17 06:56:34

1. 單元布局約束set_property BELGTHE2_CHANNEL[get_cellsswitch_v2_i/srio_0/srio_gen2_0_inst

2018-09-26 15:32:20

喜我對我的設(shè)計(jì)中的關(guān)鍵路徑以及如何約束它們有疑問。我正在使用ISE 14.1進(jìn)行實(shí)施。我有一個設(shè)計(jì),其中關(guān)鍵路徑(從源FD到目的地FD)給出-3.3ns的松弛(周期約束為10ns)。現(xiàn)在有沒有其他

2019-04-08 08:58:57

網(wǎng)上找到一個介紹,偏移約束也是一類基本時序約束,規(guī)定了外部時鐘和數(shù)據(jù)輸入輸出引腳之間的相對時序關(guān)系,只能用于端口信號,不能應(yīng)用于內(nèi)部信號我現(xiàn)在將一個輸入時鐘clk0經(jīng)過一個DCM產(chǎn)生clk1 ,然后

2017-04-27 16:12:30

我是一個FPGA初學(xué)者,關(guān)于時序約束一直不是很明白,時序約束有什么用呢?我只會全局時鐘的時序約束,如何進(jìn)行其他時序約束呢?時序約束分為哪幾類呢?不同時序約束的目的?

2012-07-04 09:45:37

嗨,我在我的項(xiàng)目中使用Zynq 7000TEMAC核心。設(shè)計(jì)工具是ISE。根據(jù)核心的示例設(shè)計(jì),除了約束控制LED之外,我已經(jīng)得到了所需的約束。我使用的板是Digilent的Zybo。現(xiàn)在,由Zybo提供并由xilinx IP核提供的約束是不兼容的。如何編輯TEMAC IP內(nèi)核提供的約束?問候,索菲亞

2020-05-14 08:33:43

時序約束文件SDC支持哪些約束?

2023-08-11 09:27:15

設(shè)計(jì)約束描述了設(shè)計(jì)的目標(biāo),這里所說的設(shè)計(jì)目標(biāo)主要包括時延目標(biāo)和面積目標(biāo)兩部分,相應(yīng)的,設(shè)計(jì)約束也由時延約束和面積約束兩部分組成。

2009-11-19 11:59:59 15

15 時序約束與時序分析 ppt教程

本章概要:時序約束與時序分析基礎(chǔ)常用時序概念QuartusII中的時序分析報(bào)告

設(shè)置時序約束全局時序約束個別時

2010-05-17 16:08:02 0

0 時序約束用戶指南包含以下章節(jié): ?第一章“時序約束用戶指南引言” ?第2章“時序約束的方法” ?第3章“時間約束原則” ?第4章“XST中指定的時序約束” ?第5章“Synplify中指定的時

2010-11-02 10:20:56 0

0 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 約束規(guī)則,好資料,有需要的朋友可以下來看看。

2016-02-22 16:21:51 0

0 偏移約束。 這里先說一下周期約束:周期約束是為了達(dá)到同步組件的時序要求。如果相鄰?fù)皆辔幌喾矗敲囱舆t就會是時鐘約束值的一半,一般不要同時使用上升沿和下降沿。注意:在實(shí)際工程中,附加的約束時間為期望值的

2017-02-09 02:56:06 918

918 xilinx 約束實(shí)現(xiàn)

2017-03-01 13:12:47 15

15 最近有些朋友在ISE中做的V7項(xiàng)目需要切換到vivado來,但導(dǎo)入代碼后,導(dǎo)入約束時,發(fā)現(xiàn)vivado不再支持UCF文件,如果手抄UCF約束到 VIVADO 的 XDC 約束,不僅浪費(fèi)時間,而且容易出錯,這里介紹一種方法可以實(shí)現(xiàn)兩種約束的切換。

2017-03-24 13:54:36 9459

9459

下面這個gif就是我們想去實(shí)現(xiàn)的效果。 藍(lán)圖應(yīng)該在右邊滑出,然后黃圖相應(yīng)地充斥整個屏幕 設(shè)置基本約束 一開始,我在IB上拖出視圖,拉上約束。這個時候倆視圖都是可見的。 黃圖有五個約束:左邊相對父視圖

2017-09-26 16:12:02 0

0 一個好的FPGA設(shè)計(jì)一定是包含兩個層面:良好的代碼風(fēng)格和合理的約束。時序約束作為FPGA設(shè)計(jì)中不可或缺的一部分,已發(fā)揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實(shí)現(xiàn)時序收斂。時序收斂作為

2017-11-17 07:54:36 2967

2967

從UCF到XDC的轉(zhuǎn)換過程中,最具挑戰(zhàn)的可以說便是本文將要討論的I/O約束了。 I/O 約束的語法 XDC 中可以用于 I/O 約束的命令包括 set_input_delay / set_output_delay 和set_max_delay / set_min_delay 。

2017-11-17 18:54:01 13590

13590

XDC中的I/O約束雖然形式簡單,但整體思路和約束方法卻與UCF大相徑庭。加之FPGA的應(yīng)用特性決定了其在接口上有多種構(gòu)建和實(shí)現(xiàn)方式,所以從UCF到XDC的轉(zhuǎn)換過程中,最具挑戰(zhàn)的可以說便是本文將要

2017-11-17 19:01:00 8139

8139

摘要:本文主要通過一個實(shí)例具體介紹ISE中通過編輯UCF文件來對FPGA設(shè)計(jì)進(jìn)行約束,主要涉及到的約束包括時鐘約束、群組約束、邏輯管腳約束以及物理屬性約束。 Xilinx定義了如下幾種約束類型

2017-11-25 01:27:02 7029

7029

一般來講,添加約束的原則為先附加全局約束,再補(bǔ)充局部約束,而且局部約束比較寬松。其目的是在可能的地方盡量放松約束,提高布線成功概率,減少ISE 布局布線時間。典型的全局約束包括周期約束和偏移約束

2017-11-25 09:14:46 3015

3015 在網(wǎng)絡(luò)視頻和實(shí)時通信應(yīng)用中需要研究帶長度約束的K端網(wǎng)絡(luò)可靠性分析問題,即任意兩端點(diǎn)之間在給定時間延遲D約束內(nèi)的K端網(wǎng)絡(luò)可靠性。對帶長度約束的K端網(wǎng)絡(luò)可靠性問題進(jìn)行了研究,主要是在傳統(tǒng)不帶路徑約束的雙

2017-12-06 14:03:03 0

0 約束優(yōu)化進(jìn)化算法主要研究如何利用進(jìn)化計(jì)算方法求解約束優(yōu)化問題,是進(jìn)化計(jì)算領(lǐng)城的一個重要研究課題.約束優(yōu)化問題求解存在約束區(qū)域離散、等式約束、非線性約束等挑戰(zhàn),其問題的本質(zhì)是,如何處理可行解與不可行解

2017-12-28 11:45:49 0

0 針對約束差分進(jìn)化算法中單一約束處理技術(shù)無法適合所有優(yōu)化問題的情況,提出了一種混合多種約束處理技術(shù)的并行約束差分進(jìn)化算法。該算法將種群分成多個子種群,各子種群采用不同的約束處理技術(shù)并行地獨(dú)立進(jìn)化,在

2018-01-02 16:40:16 0

0 針對協(xié)同設(shè)計(jì)沖突無法準(zhǔn)確全面檢測的問題,提出了一種基于約束的沖突檢測模型。在分析了協(xié)同設(shè)計(jì)中約束分層和約束滿足問題的基礎(chǔ)上,該檢測模型將約束劃分為已知約束關(guān)系集合和未知約束關(guān)系集合兩部分,分別對其

2018-01-05 11:30:08 1

1 在簡單電路中,當(dāng)頻率較低時,數(shù)字信號的邊沿時間可以忽略時,無需考慮時序約束。但在復(fù)雜電路中,為了減少系統(tǒng)中各部分延時,使系統(tǒng)協(xié)同工作,提高運(yùn)行頻率,需要進(jìn)行時序約束。通常當(dāng)頻率高于50MHz時,需要考慮時序約束。

2018-03-30 13:42:59 15212

15212

介紹FPGA約束原理,理解約束的目的為設(shè)計(jì)服務(wù),是為了保證設(shè)計(jì)滿足時序要求,指導(dǎo)FPGA工具進(jìn)行綜合和實(shí)現(xiàn),約束是Vivado等工具努力實(shí)現(xiàn)的目標(biāo)。所以首先要設(shè)計(jì)合理,才可能滿足約束,約束反過來檢查

2018-06-25 09:14:00 7199

7199 這個Xilinx Quick Take Video我們將討論Constraint Explosion。

在本次會議中,我們將研究導(dǎo)致時序約束爆炸的原因,然后是如何調(diào)試和修復(fù)異常約束問題。

2018-11-20 06:23:00 2467

2467 了解時序約束向?qū)绾斡糜凇巴耆?b class="flag-6" style="color: red">約束您的設(shè)計(jì)。

該向?qū)ё裱璘ltraFast設(shè)計(jì)方法,定義您的時鐘,時鐘交互,最后是您的輸入和輸出約束。

2018-11-29 06:47:00 3509

3509

觀看視頻,了解和學(xué)習(xí)有關(guān)XDC約束,包括時序,以及物理約束相關(guān)知識。

2019-01-07 07:10:00 7145

7145

了解如何將Altera的SDC約束轉(zhuǎn)換為Xilinx XDC約束,以及需要更改或修改哪些約束以使Altera的約束適用于Vivado設(shè)計(jì)軟件。

2018-11-27 07:17:00 5883

5883 了解如何輕松快捷地在設(shè)計(jì)周期中隨時完成一次性設(shè)計(jì)約束的導(dǎo)入,并且有信心自己的產(chǎn)品設(shè)計(jì)全程完全遵守這些約束。

2019-05-21 06:00:00 1800

1800

本視頻將會概述基本的約束管理概念,并演示如何為密集的高約束 PCB 設(shè)計(jì)創(chuàng)建和管理約束。

2019-05-17 06:01:00 2958

2958

約束有很多,并且總是有先后的,先約束哪些,再約束哪些,都有講究。按工程需要,定義好步驟,這樣就能一步一步約束,逐個思考,最終完成。

2019-12-20 07:07:00 2202

2202

這個視頻概述基本約束管理的概念和演示了如何創(chuàng)建和管理約束密集、高度受限的PCB設(shè)計(jì)。

2019-11-07 07:08:00 3618

3618 墊標(biāo)準(zhǔn)+和墊專業(yè)使用的強(qiáng)大和易于使用的約束管理系統(tǒng)創(chuàng)建、評審和驗(yàn)證PCB設(shè)計(jì)約束。

2019-11-04 07:02:00 2448

2448 增加你的效率和生產(chǎn)率。創(chuàng)造和捕捉設(shè)計(jì)約束與無壓力墊約束管理標(biāo)準(zhǔn)。

2019-11-01 07:09:00 2682

2682 Timing Report中提示warning,并不會導(dǎo)致時序錯誤,這也會讓很多同學(xué)誤以為這個約束可有可無。 但其實(shí)這種想法是不對的,比如在很多ADC的設(shè)計(jì)中,輸出的時鐘的邊沿剛好是數(shù)據(jù)的中心位置,而如果我們不加延遲約束,則Vivado會默認(rèn)時鐘和數(shù)據(jù)是對齊的。 對

2020-11-14 10:34:35 4075

4075

偽路徑約束 在本章節(jié)的2 約束主時鐘一節(jié)中,我們看到在不加時序約束時,Timing Report會提示很多的error,其中就有跨時鐘域的error,我們可以直接在上面右鍵,然后設(shè)置兩個時鐘的偽路徑

2020-11-14 11:28:10 3628

3628

有人希望能談?wù)勗谧鯢PGA設(shè)計(jì)的時候,如何理解和使用過約束。我就以個人的經(jīng)驗(yàn)談?wù)劊?什么是過約束; 為什么會使用過約束; 過約束的優(yōu)點(diǎn)和缺點(diǎn)是什么; 如何使用過約束使自己的設(shè)計(jì)更為健壯。 什么是過

2021-03-29 11:56:24 6892

6892

時序約束中的? set_input_delay/set_output_delay?約束一直是一個難點(diǎn),無論是概念、約束值的計(jì)算,還是最終的路徑分析,每一次都要費(fèi)一番腦子。Vivado為方便用戶創(chuàng)建

2021-04-10 09:38:50 2664

2664

引言:本文我們簡單介紹下Xilinx FPGA管腳物理約束,包括位置(管腳)約束和電氣約束。

2021-04-27 10:36:59 6127

6127

A 時序約束的概念和基本策略 時序約束主要包括周期約束(FFS到FFS,即觸發(fā)器到觸發(fā)器)和偏移約束(IPAD到FFS、FFS到OPAD)以及靜態(tài)路徑約束(IPAD到OPAD)等3種。通過附加

2021-09-30 15:17:46 5927

5927 使得問題更加復(fù)雜,比如一個設(shè)計(jì)使用了不同的IP核或者由不同團(tuán)隊(duì)開發(fā)的模塊。不管設(shè)計(jì)者在設(shè)計(jì)中,使用了一個還是多個XDC文件,Xilinx推薦設(shè)計(jì)者使用下面的順序來組織約束。XDC文件的約束順序如下

2021-10-13 16:56:54 7908

7908 上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 2166

2166

XDC約束可以用一個或多個XDC文件,也可以用Tcl腳本實(shí)現(xiàn);XDC文件或Tcl腳本都要加入到工程的某個約束集(set)中;雖然一個約束集可以同時添加兩種類型約束,但是Tcl腳本不受Vivado工具管理,因此無法修改其中的約束;

2022-06-30 11:27:23 5420

5420 時鐘周期約束:?時鐘周期約束,顧名思義,就是我們對時鐘的周期進(jìn)行約束,這個約束是我們用的最多的約束了,也是最重要的約束。

2022-08-05 12:50:01 5047

5047 概述 ? 對設(shè)計(jì)中的信號施加DONT_TOUCH約束,可以避免這些信號在綜合編譯過程中被優(yōu)化掉。例如,有些信號節(jié)點(diǎn)在綜合或布局布線編譯過程中可能會被優(yōu)化掉,但是我們希望在后期調(diào)試過程中能夠監(jiān)控到這些

2022-11-12 14:14:52 4733

4733 約束文件是FPGA設(shè)計(jì)中不可或缺的源文件。那么如何管理好約束文件呢? 到底設(shè)置幾個約束文件? 通常情況下,設(shè)計(jì)中的約束包括時序約束和物理約束。前者包括時鐘周期約束、輸入/輸出延遲約束、多周期路徑約束

2022-12-08 13:48:39 2150

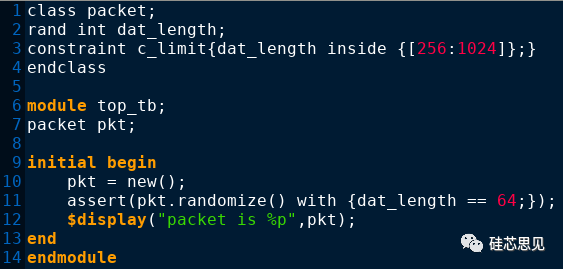

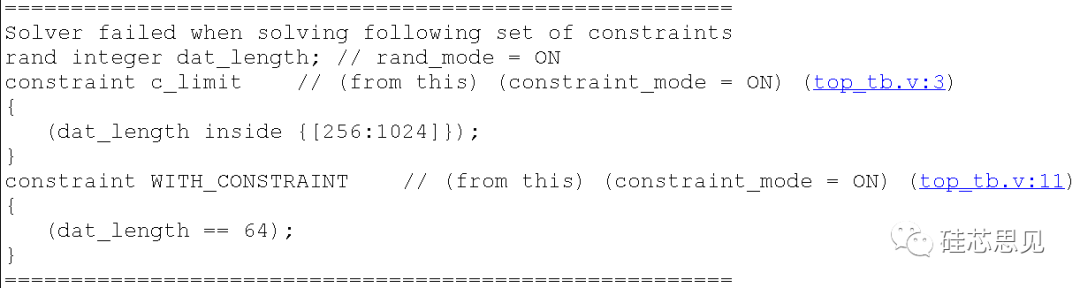

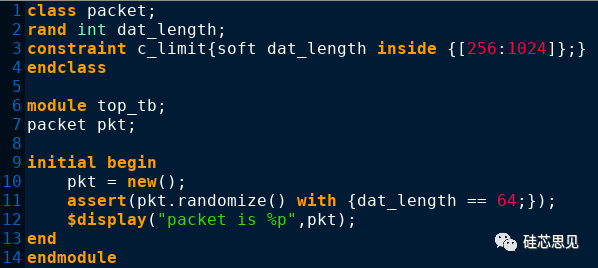

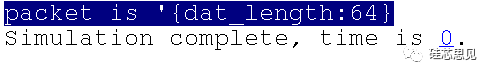

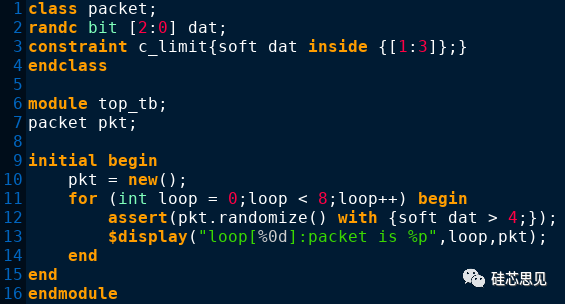

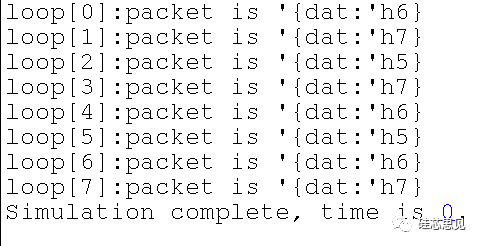

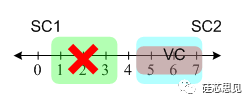

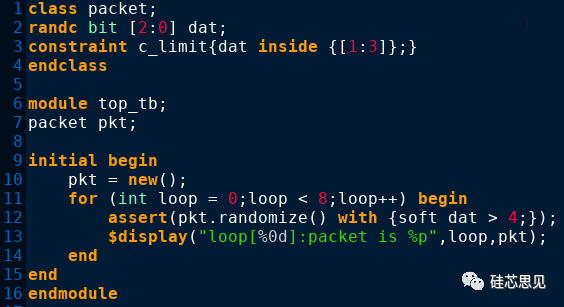

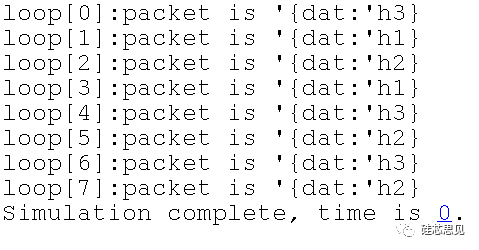

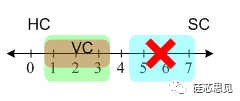

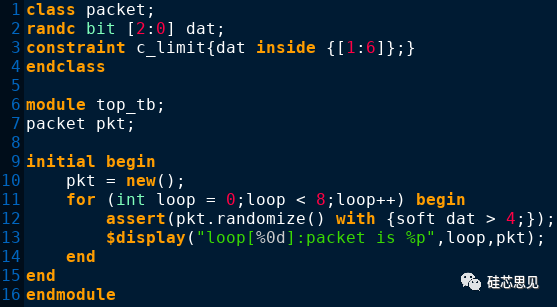

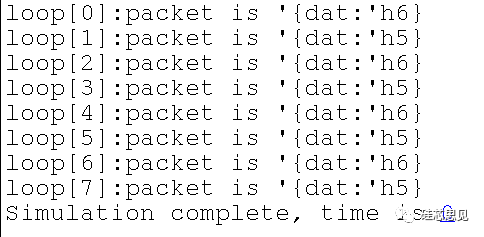

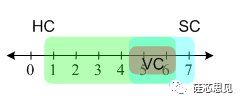

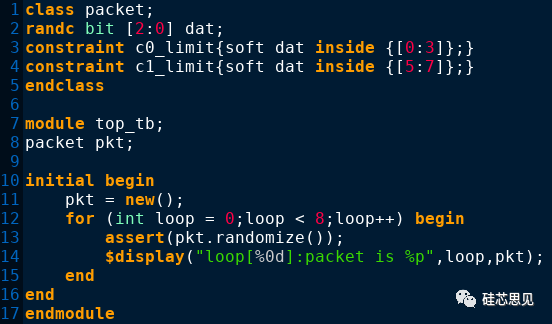

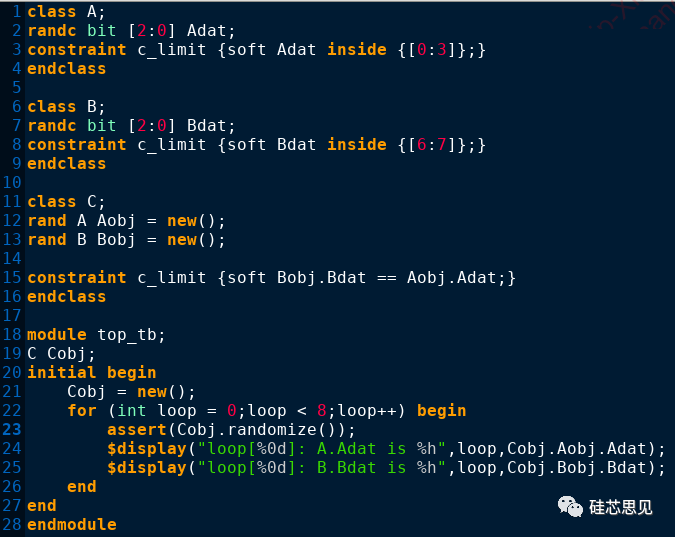

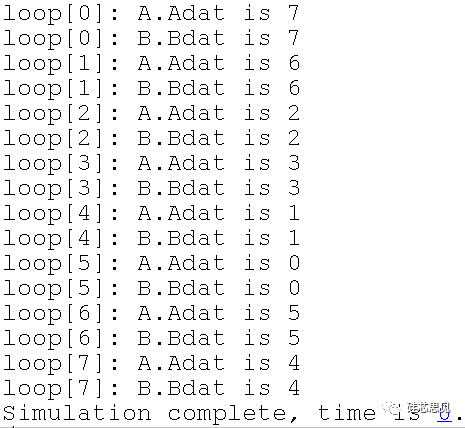

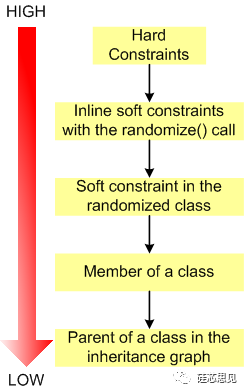

2150 上一篇文章介紹了SystemVerilog的各種隨機(jī)化方法,本文將在其基礎(chǔ)上引入SystemVerilog的隨機(jī)約束方法(constraints)。通過使用隨機(jī)約束,我們可以將隨機(jī)限制在一定的空間內(nèi),有針對性地提高功能覆蓋率。

2023-01-21 17:03:00 3203

3203 數(shù)字設(shè)計(jì)中的時鐘與約束 本文作者 IClearner 在此特別鳴謝 最近做完了synopsys的DC workshop,涉及到時鐘的建模/約束,這里就來聊聊數(shù)字中的時鐘(與建模)吧。主要內(nèi)容如下所示

2023-01-28 07:53:00 4179

4179

數(shù)獨(dú)是一種非常流行的游戲,數(shù)獨(dú)本質(zhì)上也是一個約束問題,所以我們可以讓SystemVerilog的約束求解器來幫助我們解決。 約束求解器的精妙之處就是,我們只描述約束限制,繁重的數(shù)值生成工作由工具來幫我們完成。 你只需“既要...又要...”,其他的讓下人干吧。

2023-03-08 14:06:00 2286

2286 我們在工作中常常會針對數(shù)組施加各式的約束,下面列舉一下有趣的Systemverilog數(shù)組約束示例。

2023-03-08 13:12:00 1720

1720 《XDC 約束技巧之時鐘篇》中曾對 I/O 約束做過簡要概括,相比較而言,XDC 中的 I/O 約束雖然形式簡單,但整體思路和約束方法卻與 UCF 大相徑庭。加之 FPGA 的應(yīng)用特性決定了其在接口

2023-04-06 09:53:30 2523

2523 繼《XDC 約束技巧之 I/O 篇(上)》詳細(xì)描述了如何設(shè)置 Input 接口 約束后,我們接著來聊聊怎樣設(shè)置 Output 接口約束,并分析 UCF 與 XDC 在接口約束上的區(qū)別。

2023-04-10 11:00:42 2374

2374 上面是最先想到的寫法,但是會報(bào)錯,因?yàn)镾V約束語法不允許使用size()或任何其他隨機(jī)值作為索引。

2023-05-04 17:35:19 1862

1862 很多人詢問關(guān)于約束、時序分析的問題,比如:如何設(shè)置setup,hold時間?如何使用全局時鐘和第二全局時鐘(長線資源)?如何進(jìn)行分組約束?如何約束某部分組合邏輯?如何通過約束保證異步時鐘域之間

2023-05-29 10:06:56 1538

1538

我們在工作中常常會針對數(shù)組施加各式的約束,下面列舉一下有趣的**Systemverilog數(shù)組約束**示例

2023-05-30 11:13:21 1421

1421 前面幾篇文章已經(jīng)詳細(xì)介紹了FPGA時序約束基礎(chǔ)知識以及常用的時序約束命令,相信大家已經(jīng)基本掌握了時序約束的方法。

2023-06-23 17:44:00 4087

4087

FPGA設(shè)計(jì)中,時序約束對于電路性能和可靠性非常重要。

2023-06-26 14:53:53 6881

6881

今天介紹一下,如何在Vivado中添加時序約束,Vivado添加約束的方法有3種:xdc文件、時序約束向?qū)В–onstraints Wizard)、時序約束編輯器(Edit Timing Constraints )

2023-06-26 15:21:11 6084

6084

很多小伙伴開始學(xué)習(xí)時序約束的時候第一個疑惑就是標(biāo)題,有的人可能會疑惑很久。不明白時序約束是什么作用,更不明白怎么用。

2023-06-28 15:10:33 2626

2626

??本文主要介紹了時序設(shè)計(jì)和時序約束。

2023-07-04 14:43:52 2391

2391 本小節(jié)對時序約束做最終的總結(jié)

2023-07-11 17:18:57 1252

1252

本文將詳細(xì)介紹輸出延時的概念、場景分類、約束參數(shù)獲取方法以及約束方法

2023-07-11 17:12:50 4481

4481

上一篇文章《暗藏玄機(jī)的SV隨機(jī)化》介紹了SystemVerilog的各種隨機(jī)化方法,本文將在其基礎(chǔ)上引入SystemVerilog的隨機(jī)約束方法(constraints)。通過使用隨機(jī)約束,我們可以將隨機(jī)限制在一定的空間內(nèi),有針對性地提高功能覆蓋率。

2023-09-24 12:15:30 3513

3513 LOC約束是FPGA設(shè)計(jì)中最基本的布局約束和綜合約束,能夠定義基本設(shè)計(jì)單元在FPGA芯片中的位置,可實(shí)現(xiàn)絕對定位、范圍定位以及區(qū)域定位。

2024-04-26 17:05:05 2426

2426

建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

2024-08-06 11:40:18 2370

2370

電路的兩類約束通常指的是電氣約束和物理約束。這兩類約束在電路設(shè)計(jì)和分析中起著至關(guān)重要的作用。 一、電氣約束 電氣約束的概念 電氣約束是指在電路設(shè)計(jì)和分析中,需要遵循的電氣原理和規(guī)律。這些原理和規(guī)律

2024-08-25 09:34:51 2556

2556 本文重點(diǎn)PCBlayout約束管理在設(shè)計(jì)中的重要性Layout約束有助避免一些設(shè)計(jì)問題設(shè)計(jì)中可以使用的不同約束在PCB設(shè)計(jì)規(guī)則和約束管理方面,許多設(shè)計(jì)師試圖采用“一刀切”的方法,認(rèn)為同樣的規(guī)則設(shè)定

2025-05-16 13:02:47 901

901

電子發(fā)燒友App

電子發(fā)燒友App

評論