了解時(shí)序約束向?qū)绾斡糜凇巴耆奔s束您的設(shè)計(jì)。 該向?qū)ё裱璘ltraFast設(shè)計(jì)方法,定義您的時(shí)鐘,時(shí)鐘交互,最后是您的輸入和輸出約束。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

賽靈思

+關(guān)注

關(guān)注

33文章

1798瀏覽量

133425 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1971瀏覽量

134985 -

設(shè)計(jì)

+關(guān)注

關(guān)注

4文章

826瀏覽量

71318

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

Vivado時(shí)序約束中invert參數(shù)的作用和應(yīng)用場(chǎng)景

在Vivado的時(shí)序約束中,-invert是用于控制信號(hào)極性的特殊參數(shù),應(yīng)用于時(shí)鐘約束(Clock Constraints)和延遲約束(Delay Constraints)中,用于指定

RGB時(shí)序燈條的工作原理講解

圖文配合講解了RGB時(shí)序燈條的應(yīng)用場(chǎng)景、什么是RGB時(shí)序燈條、信號(hào)格式與傳輸規(guī)則、燈珠芯片的工作流程、顏色與動(dòng)態(tài)效果控制方式等

發(fā)表于 02-06 11:36

?0次下載

輸入引腳時(shí)鐘約束_Xilinx FPGA編程技巧-常用時(shí)序約束詳解

基本的約束方法

為了保證成功的設(shè)計(jì),所有路徑的時(shí)序要求必須能夠讓執(zhí)行工具獲取。最普遍的三種路徑以及異常路徑為:

輸入路徑(Input Path),使用輸入約束

寄存器到寄存器路徑

發(fā)表于 01-16 08:19

移植E203到Genesys2開發(fā)板時(shí)遇到時(shí)序問(wèn)題的常見原因

-clk_out2 to clk_out1的setup違例,看block design發(fā)現(xiàn)違例太大和時(shí)序約束無(wú)關(guān),其實(shí)是axi_interconnect一側(cè)的端口時(shí)鐘需要保持一致。這里e203核時(shí)鐘16M,而

發(fā)表于 10-29 07:04

時(shí)序約束問(wèn)題的解決辦法

Time 是否滿足約束。

我們要留意的是 WNS 和 WHS 兩個(gè)數(shù)值,如果這兩個(gè)數(shù)值為紅色,就說(shuō)明時(shí)序不滿足約束。下面將解釋怎么解決這個(gè)問(wèn)題。

1. Setup Time 違例

Setup

發(fā)表于 10-24 09:55

關(guān)于綜合保持時(shí)間約束不滿足的問(wèn)題

1、將 nuclei-config.xdc 和 nuclei-master.xdc 加入到項(xiàng)目工程中,綜合得到時(shí)序約束報(bào)告如下:

保持時(shí)間約束不滿足,分析原因,發(fā)現(xiàn)所有不滿足均出現(xiàn)在

發(fā)表于 10-24 07:42

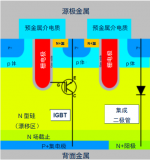

高效反向?qū)?/b>通IGBT的原理詳解

在先進(jìn)的反向?qū)?/b>通絕緣柵雙極晶體管(RCIGBT)中,低導(dǎo)通電壓降(Vce(sat))和集成二極管正向電壓(VF)對(duì)于有效減少導(dǎo)通損耗至關(guān)重要。

技術(shù)資訊 I Allegro 設(shè)計(jì)中的走線約束設(shè)計(jì)

本文要點(diǎn)在進(jìn)行時(shí)序等長(zhǎng)布線操作的時(shí)候,在布線操作的時(shí)候不管你是走蛇形線還是走折線,約束管理器會(huì)自動(dòng)幫你計(jì)算長(zhǎng)度、標(biāo)偏差,通過(guò)精確控制走線長(zhǎng)度,來(lái)實(shí)現(xiàn)信號(hào)的時(shí)序匹配。約束設(shè)計(jì)就是一套精準(zhǔn)

技術(shù)資訊 I 圖文詳解約束管理器-差分對(duì)規(guī)則約束

本文要點(diǎn)你是否經(jīng)常在Layout設(shè)計(jì)中抓瞎,拿著板子無(wú)從下手,拿著鼠標(biāo)深夜狂按;DDR等長(zhǎng)沒(méi)做好導(dǎo)致系統(tǒng)不穩(wěn)定,PCIe沒(méi)設(shè)相位容差造成鏈路訓(xùn)練失敗……這些都是血淚教訓(xùn),關(guān)鍵時(shí)刻需要靠約束管理器救命

西門子再收購(gòu)EDA公司 西門子宣布收購(gòu)Excellicon公司 時(shí)序約束工具開發(fā)商

精彩看點(diǎn) 此次收購(gòu)將幫助系統(tǒng)級(jí)芯片 (SoC) 設(shè)計(jì)人員通過(guò)經(jīng)市場(chǎng)檢驗(yàn)的時(shí)序約束管理能力來(lái)加速設(shè)計(jì),并提高功能約束和結(jié)構(gòu)約束的正確性 ? 西門子宣布 收購(gòu) Excellicon 公司

PCB Layout 約束管理,助力優(yōu)化設(shè)計(jì)

本文重點(diǎn)PCBlayout約束管理在設(shè)計(jì)中的重要性Layout約束有助避免一些設(shè)計(jì)問(wèn)題設(shè)計(jì)中可以使用的不同約束在PCB設(shè)計(jì)規(guī)則和約束管理方面,許多設(shè)計(jì)師試圖采用“一刀切”的方法,認(rèn)為同

FPGA時(shí)序約束之設(shè)置時(shí)鐘組

Vivado中時(shí)序分析工具默認(rèn)會(huì)分析設(shè)計(jì)中所有時(shí)鐘相關(guān)的時(shí)序路徑,除非時(shí)序約束中設(shè)置了時(shí)鐘組或false路徑。使用set_clock_groups命令可以使

一文詳解Vivado時(shí)序約束

Vivado的時(shí)序約束是保存在xdc文件中,添加或創(chuàng)建設(shè)計(jì)的工程源文件后,需要?jiǎng)?chuàng)建xdc文件設(shè)置時(shí)序約束。時(shí)序

如何使用時(shí)序約束向?qū)?/h1>

如何使用時(shí)序約束向?qū)?/h1>

評(píng)論