本視頻將會概述基本的約束管理概念,并演示如何為密集的高約束 PCB 設計創建和管理約束。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

pcb

+關注

關注

4412文章

23919瀏覽量

425511 -

設計

+關注

關注

4文章

827瀏覽量

71428

發布評論請先 登錄

相關推薦

熱點推薦

電壓放大器在主動約束層阻尼板研究測試中的應用

主動約束層阻尼結構采用壓電或其他智能材料取代經典約束層阻尼結構中的約束層,并通過引入主動控制系統,進一步增強約束阻尼層對振動能量的耗散能力。即使在主動控制系統關閉或失效的情況下,仍能保

Vivado時序約束中invert參數的作用和應用場景

在Vivado的時序約束中,-invert是用于控制信號極性的特殊參數,應用于時鐘約束(Clock Constraints)和延遲約束(Delay Constraints)中,用于指定信號的有效邊沿或邏輯極性。

輸入引腳時鐘約束_Xilinx FPGA編程技巧-常用時序約束詳解

基本的約束方法

為了保證成功的設計,所有路徑的時序要求必須能夠讓執行工具獲取。最普遍的三種路徑以及異常路徑為:

輸入路徑(Input Path),使用輸入約束

寄存器到寄存器路徑

發表于 01-16 08:19

時序約束問題的解決辦法

Time 是否滿足約束。

我們要留意的是 WNS 和 WHS 兩個數值,如果這兩個數值為紅色,就說明時序不滿足約束。下面將解釋怎么解決這個問題。

1. Setup Time 違例

Setup

發表于 10-24 09:55

關于綜合保持時間約束不滿足的問題

1、將 nuclei-config.xdc 和 nuclei-master.xdc 加入到項目工程中,綜合得到時序約束報告如下:

保持時間約束不滿足,分析原因,發現所有不滿足均出現在

發表于 10-24 07:42

技術資訊 I Allegro 設計中的走線約束設計

本文要點在進行時序等長布線操作的時候,在布線操作的時候不管你是走蛇形線還是走折線,約束管理器會自動幫你計算長度、標偏差,通過精確控制走線長度,來實現信號的時序匹配。約束設計就是一套精準的導航系統

技術資訊 I 圖文詳解約束管理器-差分對規則約束

本文要點你是否經常在Layout設計中抓瞎,拿著板子無從下手,拿著鼠標深夜狂按;DDR等長沒做好導致系統不穩定,PCIe沒設相位容差造成鏈路訓練失敗……這些都是血淚教訓,關鍵時刻需要靠約束管理器救命

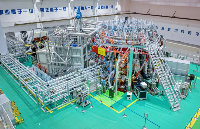

再創新高,“中國環流三號”實現百萬安培億度高約束模

近日,由核工業西南物理研究院(簡稱“西物院”)研制的新一代人造太陽“中國環流三號”再次創下我國聚變裝置運行新紀錄——實現百萬安培億度高約束模(H模),即裝置同時實現等離子體電流100萬安培、離子溫度

PCB設計,輕松歸檔,效率倍增!

PCB設計一鍵歸檔簡化流程,提升效率,一鍵歸檔,盡在掌握!在電子產品設計領域,PCB設計工作完成后,需要輸出不同種類的文件給到PCB生產商,產線制造部門,測試部門,同時還需將設計文件進行歸檔管

西門子再收購EDA公司 西門子宣布收購Excellicon公司 時序約束工具開發商

精彩看點 此次收購將幫助系統級芯片 (SoC) 設計人員通過經市場檢驗的時序約束管理能力來加速設計,并提高功能約束和結構約束的正確性 ? 西門子宣布 收購 Excellicon 公司

PanDao:實際約束條件下成像系統的初始結構的生成

,受限于手機內部嚴苛的長度約束,使用高非球面化透鏡就成為了必然選擇。下文將展示幾個FTR技術應用的案例,并將生成的光學設計結果與生產信息進行權重整合。為此,采用最新研發的PanDao軟件 [3-5

發表于 05-07 08:57

FPGA時序約束之設置時鐘組

Vivado中時序分析工具默認會分析設計中所有時鐘相關的時序路徑,除非時序約束中設置了時鐘組或false路徑。使用set_clock_groups命令可以使時序分析工具不分析時鐘組中時鐘的時序路徑,使用set_false_path約束則會雙向忽略時鐘間的時序路徑

智慧路燈的數據管理和使用是否有相關法規約束?

。隨著其功能的不斷拓展,一個關鍵問題浮現出來:智慧路燈的數據管理和使用,是否有相關法規約束呢?答案是肯定的。 從國家層面來看,我國已出臺多項標準對智慧路燈的數據相關操作進行規范。2021 年 2 月 1 日正式實施的《城市公

如何為密集的高約束PCB設計創建和管理約束

如何為密集的高約束PCB設計創建和管理約束

評論