高速數字電路的仿真

介紹了專用于高速數字電路的仿真工具Hyperlynx,并使用它對高速數字電路中的阻抗匹配、傳輸線長度

2009-03-20 14:11:39 1649

1649

本文介紹了EDA技術主要特點和功能,并對將EDA技術引入到數字電路設計工作方案進行了探討。##EDA技術在數字系統中應用以基于AlteraEPM7128SLC84-15芯片和MAX PlusII 10.0軟件平臺數字鐘設計為例,討論EDA技術在數字系統中具體應用。

2014-01-24 14:38:14 4020

4020

本帖最后由 lee_st 于 2017-11-30 12:35 編輯

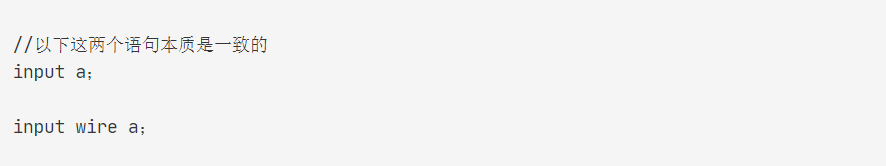

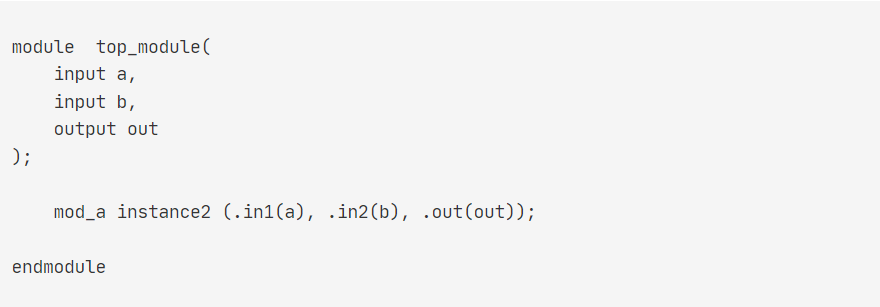

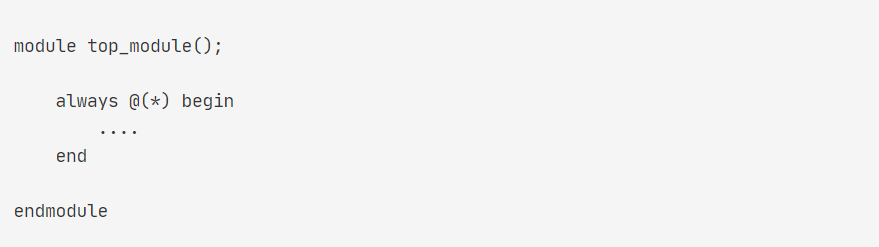

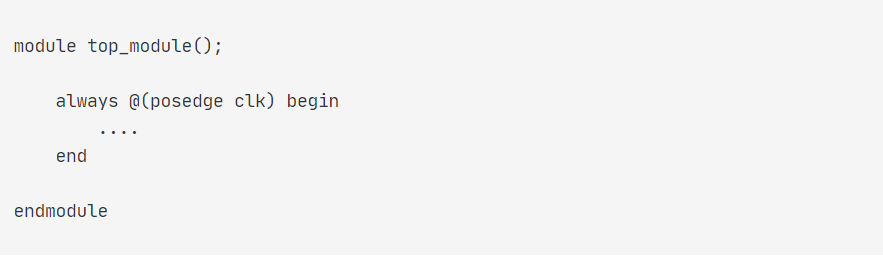

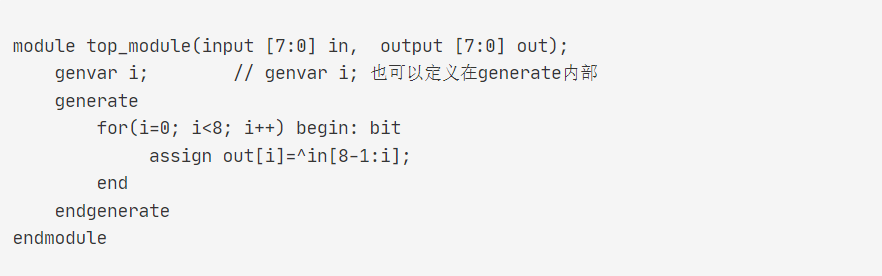

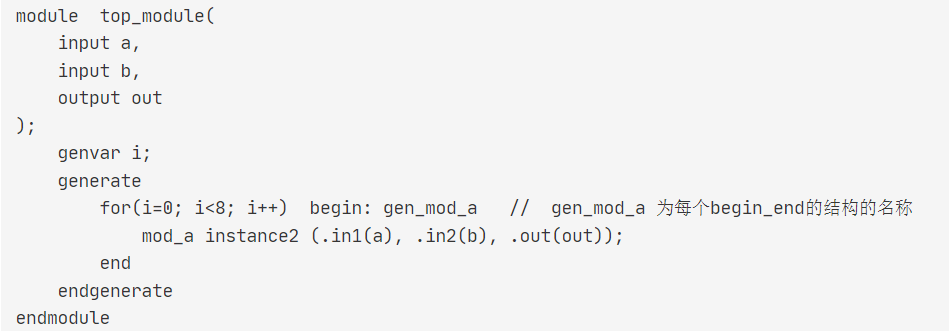

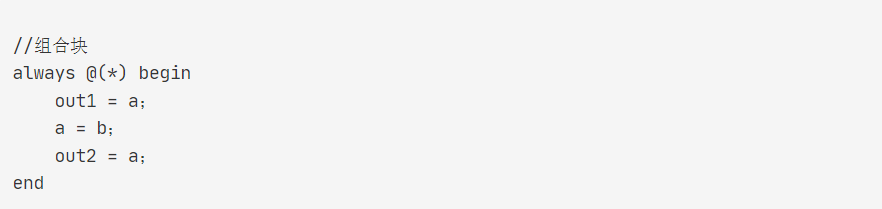

講授內容EDA設計方法學;Verilog HDL語言;數字電路與系統設計;高級描述語言及工具使用;

2017-11-30 12:33:55

講授內容EDA設計方法學;Verilog HDL語言;數字電路與系統設計;高級描述語言及工具使用;

2017-11-30 12:36:07

講授內容EDA設計方法學;Verilog HDL語言;數字電路與系統設計;高級描述語言及工具使用;

2017-11-30 12:38:44

本帖最后由 lee_st 于 2017-11-30 12:42 編輯

講授內容EDA設計方法學;Verilog HDL語言;數字電路與系統設計;高級描述語言及工具使用;

2017-11-30 12:41:35

講授內容EDA設計方法學;Verilog HDL語言;數字電路與系統設計;高級描述語言及工具使用;

2017-11-30 12:44:09

講授內容EDA設計方法學;Verilog HDL語言;數字電路與系統設計;高級描述語言及工具使用;

2017-11-30 12:46:17

講授內容EDA設計方法學;Verilog HDL語言;數字電路與系統設計;高級描述語言及工具使用;

2017-11-30 12:48:48

Verilog數字系統設計十二復雜數字電路設計2文章目錄Verilog數字系統設計十二前言一、什么是FIFO控制器?二、編程1.要求:2.設計思路:3.FIFO控制器實現:總結前言隨著人工智能

2022-02-09 07:23:50

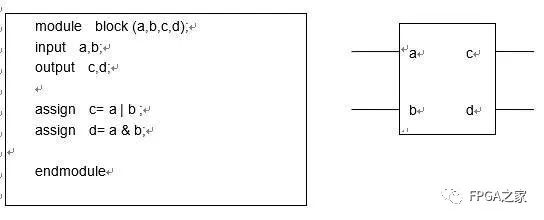

、韓國、美國等區域應用很普遍。本文簡要地介紹國內數字電路設計普遍使用的Verilog語言。verilog是什么。Verilog HDL是一種硬件描述語言,以文本形式來描述數字系統硬件的結構和行為的語言

2021-07-26 06:39:56

數字電路-數字時鐘電路設計 希望大家喜歡。

2016-12-06 09:46:39

兩種類型,這里又以CMOS集成數字電路為主,因它功耗低、工作電壓范圍寬、扇出能力強和售價低等,很適合電子愛好者選用。 介紹應用時,以實用為主,特別介紹一些家電產品和娛樂產品中的數字電路。這樣可使

2018-08-28 15:36:27

數字電路設計與Verilog HDL

2015-07-16 16:21:19

在數字電子技術基礎課程中,數字電路設計的數學基礎是布爾函數,并利用卡諾圖進行化簡。卡諾圖只適用于輸入比較少的邏輯函數的化簡。數字電路的設計方法是:組合電路設計:提出問題→確定邏輯關系→列真值表→邏輯

2019-02-27 11:55:00

答案,以助你在電路設計軟件學習之路上更進一步。騷年,抱著以上的疑問,一起來看看吧。在電子設計輔助軟件中,Protel是最常用的軟件,新版本的Protel軟件增加了電路仿真功能,能夠對設計的電路進行模擬

2019-09-24 07:30:00

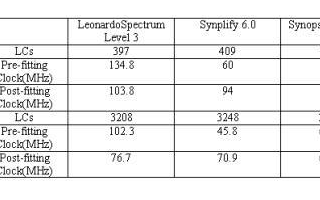

FPGA CPLFPGA CPLD 數字電路設計經驗分享FPGA/CPLD數字電路設計經驗分享摘要:在數字電路的設計中,時序設計是一個系統性能的主要標志,在高層次設計方法中,對時序控制的抽象度也相應

2012-08-11 10:17:18

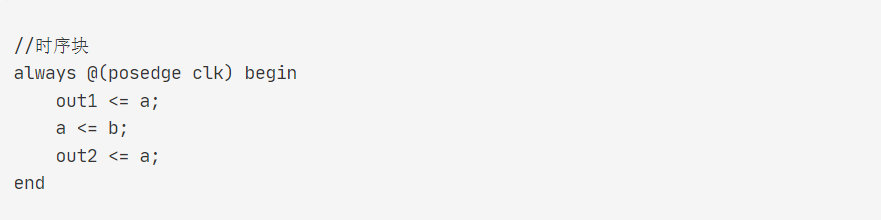

在數字電路的設計中,時序設計是一個系統性能的主要標志,在高層次設計方法中,對時序控制的抽象度也相應提高,因此在設計中較難把握,但在理解RTL電路時序模型的基礎上,采用合理的設計方法在設計復雜數字系統

2012-03-05 16:33:30

FPGACPLD數字電路設計經驗分享

2012-08-07 21:46:49

Perl語言在電路設計中的應用實用提取和報表語言是由Perl語言在電路設計中的應用 開發并不斷更新,用于Perl語言在電路設計中的應用 環境下編程的一種模塊化的、可擴展的高級語言。在集成電路后端

2012-01-11 15:19:01

關于數字電路設計的一些經驗

2015-03-17 21:27:38

基本的了解,自己買了更詳細的夏聞宇的書,如果有誰需要電子稿的我可以發給他,留郵箱Verilog的語法覆蓋的方面比C語言更加多,可使用的靈活性更強,一定要貫徹的是數字電路的設計,不要用C語言的思想來做三

2016-09-02 19:13:29

數據的數字電路。從整體上看,數字電路可以分為組合邏輯電路和時序邏輯電路兩大類。一、數字電路的發展與分類 從前面的介紹,大家已經了解到數字電路是以二值數字邏輯為基礎的,其工作信號是離散的數字信號。電路

2009-04-06 23:45:00

求一款基于VHDL的異步串行通信電路設計分享

2021-04-08 06:16:42

分享一款不錯的基于可編程邏輯器件PLD的數字電路設計方案

2021-04-30 06:34:54

華為《高速數字電路設計教材》這本書是專門為電路設計工程師寫的。主要描述模擬電路原理在高速數字電路設計中的分析應用

2014-09-01 23:09:11

華為《高速數字電路設計教材》這本書是專門為電路設計工程師寫的。主要描述模擬電路原理在高速數字電路設計中的分析應用

2014-09-01 23:20:19

FPGA芯片是由哪些部分組成的?如何去實現一種基于FPGA芯片的可重構數字電路設計?

2021-11-05 08:38:57

射頻和數字電路設計的區別是什么?

2021-05-18 06:05:19

;MMICAD等。下面簡單介紹前三個軟件。 (1)SPICE:由美國加州大學推出的電路分析仿真軟件,現在用得較多的是PSPICE6.2,在同類產品中是功能最為強大的模擬和數字電路混合仿真 EDA軟件

2018-10-17 11:48:12

設計工具軟件、數字電路系統設計實踐”的體系結構編寫。為了讓讀者更容易掌握Verilog HDL知識,本書在介紹數字電路設計的過程中列舉了Verilog HDL的很多例程,并假定讀者沒有任何數字邏輯

2022-04-19 14:40:04

怎么實現基于可編程邏輯器件的數字電路設計?

2021-05-06 08:36:18

大家好,我是電子愛好者新手,現在想學點數字電路設計。剛把數字電路這么課程學完。我想學電路設計,不知道如何下手。比如FPGA什么的,這些都怎么開始學習啊。請知情者指點下。謝謝

2013-08-02 08:17:31

數字集成電路設計ASIC設計/驗證經驗;2.熟悉邏輯/時序電路的原理和設計;3.精通verilog語言;熟練使用Cadence,Modelsim,NC-Verilog,DC等設計驗證工具;4.有較強的責任心

2015-02-27 10:52:58

及基本邏輯器件的硬件描述語言引入各個章節中。《新編數字電路與數字邏輯》可作為高等院校計算機、電子、通信、自動化、機電一體化等專業本科和專科的教材,也可作為自學考試和從事電子技術工程人員的自學用書。注 本資料來源于網絡資源 出處電子愛好者論壇

2018-10-28 21:36:01

請求大佬分享一款用于物體探測與統計的電路設計

2021-04-14 06:42:37

等。下面簡單介紹前三個軟件。(1)SPICE:由美國加州大學推出的電路分析仿真軟件,現在用得較多的是PSPICE6.2,在同類產品中是功能最為強大的模擬和數字電路混合仿真 EDA軟件,它可以進行

2020-06-28 10:49:47

群主好,我想請教數字電路的系統級設計驗證工具及流程?即系統工程師常用的硬件描述語言,系統驗證工具以及設計驗證的基本流程,多謝!

2012-09-05 15:11:23

【簡介】本書從高速數字電路的定義談起,介紹了傳輸線的基本理論,并涉及到了如何運用Grounding/Guard降低噪聲等內容,還以高速數字電路電氣特性,如串擾、反射及時鐘脈沖不對稱等為例,闡述了一

2017-12-12 08:51:55

《高速數字電路設計及EMC設計》分享。

2015-08-04 11:50:33

高速數字電路設計的幾個基本概念高速數字電路設計的基本要求是什么

2021-04-27 06:19:05

基于LabVIEW的數字電路設計和仿真

數字電路設計和仿真是電子工程領域的基本技術。介紹了基于LabV IEW的數字電路設計和仿真的原理和方法,比較了其與專業EDA軟

2010-03-30 16:09:49 125

125 本書是專門為電路設計師工程師寫的

它主要描述模擬電路原理在高速數字電路設計中的分析應用

1-3章分別介紹了模擬電路術語、邏輯門高速特性和標準高速電路測量

2010-06-23 18:02:57 64

64 流水線技術在高速數字電路設計中的應用

2010-07-17 16:37:21 6

6 這本書是專門為電路設計工程師寫的。它主要描述了模擬電路原理在高速數字電路設計中的分析應用。通過列舉很多的實例,作者詳細分析了一直困擾高速電路路設計工程師的鈴

2010-11-08 16:49:54 0

0 高速數字電路設計

關于高速數字電路的電氣特性,設計重點大略可分為三項 : Ø 正時 (Timing) :由于數字電路大多依據時脈信號來做信號間的同

2007-10-16 17:22:57 3406

3406 數字電路設計

關于高速數字電路的電氣特性,設計重點大略可分為三項:

正時(Timing) :由于數字電路大

2009-08-26 19:08:06 3040

3040 基于可編程邏輯器件的數字電路設計

0 引 言

可編程邏輯器件PLD(Programmable Logic De-vice)是一種數字電路,它可以由用戶來進行編程和進行配置,利用它可以

2009-11-16 10:46:41 1876

1876

《VHDL與數字電路設計》是有盧毅、賴杰主編的,主要介紹涉及數字系統設計的多方面原理、技術及應用,主要內容有數字系統的基本設計思想、設計方法和設計步驟, VHDL 硬件描述語言

2011-07-11 15:54:27 0

0 文章介紹了數字電路設計中的信號完整性問題, 探討了振鈴、邊沿畸變、反射、地彈、串擾和抖動等各種信號完整性問題的成因和抑制措施。針對常見的反射和串擾給出了較為詳細的分

2011-09-07 16:14:58 104

104 主要內容有:第1 章實驗基本知識、第2 章 PROTEUS 仿真軟件快速入門、第3 章數字電路基礎實驗、第4 章數字電路綜合設計實驗、 第5章VHDL 語言基礎、第6 章 數字電路的CPLD/FPGA 實現。在教

2011-09-07 16:29:53 0

0 高速數字電路設計及EMC設計!資料來源網絡,如有侵權,敬請見諒

2015-11-19 14:48:57 0

0 數字電路中的FPGA和verilog教程,好東西,喜歡的朋友可以下載來學習。

2016-01-18 17:44:30 42

42 高速數字電路設計及EMC設計(華為),下來看看。

2016-03-29 15:41:20 54

54 高速數字電路設計大全

2017-01-17 19:54:24 60

60 數字電路設計方案中DSP與FPGA的比較與選擇

2017-01-18 20:39:13 15

15 這本書是專門為電路設計工程師寫的。它主要描述了模擬電路原理在高速數字電路設計中的分析應用。通過列舉很多的實例,作者詳細分析了一直困擾高速電路路設計工程師的鈴流、串擾和輻射噪音等問題。

2018-09-10 08:00:00 64

64 高速數字電路設計跟低速數字電路設計不同的是:他強調組成電路的無源部件對電路的影響。這些無源器件包括導線、電路板和組成數字產品的集成電路。在低速設計中,這些部件單純

的只是電路的一部分,根本不用多做考慮,可是在高速設計中,這些部件對電路的性能有著直接的影響。

2019-04-11 11:38:32 4423

4423

數字電路中學到的邏輯電路功能,使用硬件描述語言(Verilog/VHDL)描述出來,這需要設計人員能夠用硬件編程思維來編寫代碼,以及擁有扎實的數字電路功底。

2019-12-05 07:10:00 4016

4016

雖然在FPGA中,利用綜合工具來可以將VHDL或者Verilog代碼轉化成電路。但是作為FPGA工程師而言,在沒有綜合工具的情況下,如何設計出數字電路呢?如果已經知道需要實現的功能的狀態機,如何將它轉化成數字電路呢?和設計出數字電路呢?

2020-06-17 16:33:38 3746

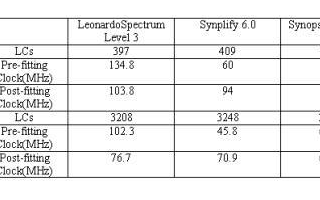

3746 在使用FPGA做數字電路設計的流程中,綜合是其中非常重要的一個步驟。同樣的設計源代碼,無論是VHDL或Verilog HDL,采用不同的綜合工具綜合會產生不同的結果。

2020-07-24 15:47:00 2351

2351

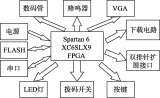

數字電路作為一門專業基礎課,除了介紹數字電路的理論知識外,更需要通過配套的實驗平臺將理論知識和實踐環節相結合,培養學生的動手能力和實踐創新能力。

2020-08-16 12:03:45 8570

8570

在當今電子技術行業發展過程中,對高速電路數字設計十分關注,高速數字電路是利用多個電子元件組成的,可以讓計算機高速數字電路技術進一步提高,因此在計算機中使用高速數字電路設計技術也就更加普遍。

2020-08-21 17:41:10 4223

4223 本文檔的主要內容詳細介紹的是Verilog教程之Verilog HDL數字集成電路設計方法和基礎知識課件

2020-12-09 11:24:19 53

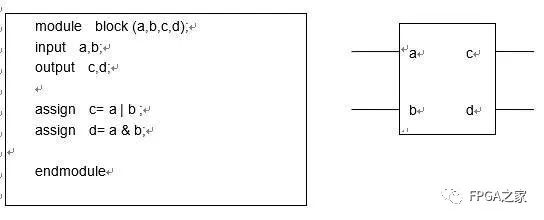

53 在現階段,作為設計人員熟練掌握 Verilog HDL程序設計的多樣性和可綜合性,是至關重要的。作為數字集成電路的基礎,基本數字邏輯電路的設計是進行復雜電路的前提。本章通過對數字電路中基本邏輯電路的erilog HDL程序設計進行講述,掌握基本邏輯電路的可綜合性設計,為具有特定功能的復雜電路的設計打下基礎

2020-12-09 11:24:00 37

37 高速數字電路設計-華為

2021-04-21 15:45:08 0

0 華為高速數字電路設計教材資源下載

2021-06-04 11:06:00 102

102 1. 前言 在數字電路課程中,老師在講組合邏輯的時候,一般都會講競爭與冒險。sky當時也聽的云里霧里,沒有想清楚如下問題: 1) 競爭與冒險究竟是什么東西?有啥物理現象? 2) 在數字電路設計中

2021-08-09 14:43:08 4078

4078

知乎上刷到一個問題,問性能最強的編程語言是什么?看到高贊回答到是Verilog,然后在評論區就引發了一場Verilog到底算不算編程語言的爭論,我覺得比較有意思,所以就也打算嘮嘮這個事情。 趁著最近

2021-08-23 14:30:49 6909

6909 FPGA CPLD數字電路設計經驗分享.(電源技術發展怎么樣)-FPGA CPLD數字電路設計經驗分享? ? ? ? ? ? ? ? ? ??

2021-09-18 10:58:03 52

52 、韓國、美國等區域應用很普遍。本文簡要地介紹國內數字電路設計普遍使用的Verilog語言。verilog是什么。Verilog HDL是一種硬件描述語言,以文本形式來描述數字系統硬件的結構和行為的語言

2021-11-06 09:05:57 15

15 的,呵呵。我們這里只討論數字電路設計。實際上就是如何把我們從課堂上學到的邏輯電路使用原理圖(很少有人用這個拉),或者硬件描述語言(Verilog/VHDL)來實現,或許...

2021-11-06 11:36:01 19

19 Verilog數字系統設計十二復雜數字電路設計2文章目錄Verilog數字系統設計十二前言一、什么是FIFO控制器?二、編程1.要求:2.設計思路:3.FIFO控制器實現:總結前言 隨著人工智能

2021-12-05 15:51:04 9

9 筆試時也很常見。[例1] 一個簡單的狀態機設計--序列檢測器序列檢測器是時序數字電路設計中經典的教學范例,下面我們將用Verilog HDL語言來描述、仿真、并實現它。序列檢測器的邏輯功能...

2021-12-17 18:28:40 16

16 本書系統地介紹了數字電路的基礎知識,組合和時序電路的分析、設計方法,使讀者對數字系統的構成及描述有較深入的了解,達到在具有較堅實的數字電路和數字系統理論知識的基礎上,獨立使用可編程邏輯器件、其他

2022-06-06 16:54:09 12

12 實用電子電路設計與調試數字電路教材資料免費下載。

2022-04-07 14:46:38 40

40 黑魔書 351頁- 高速數字設計PDF版,華為內部數字電路設計教材

2022-06-08 14:33:25 0

0 高速數字電路設計教材-華為

2022-06-13 14:55:54 0

0 數字電路設計是數字電路最為關鍵及重要的一步,今天我們將從各個流程為大家介紹完整的數字電路設計!

2022-07-10 17:14:16 9335

9335 HDLBits 是一組小型電路設計習題集,使用 Verilog/SystemVerilog 硬件描述語言 (HDL) 練習數字硬件設計~

2022-08-31 09:06:59 2676

2676 眼圖醫生(Eye Doctor)是力科于2006年推出的用于高速串行數字電路設計的強大工具,包括了虛擬探測(virtual probing)與接收端均衡(receiver equalization

2022-09-30 09:08:41 2349

2349 Verilog HDL是一種用于數字系統設計的語言。用Verilog HDL描述的電路設計就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語言也是一種結構

2023-05-22 15:52:42 1538

1538

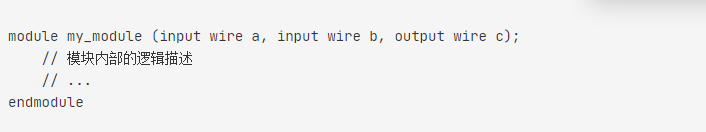

Verilog HDL是一種用于數字系統設計的語言。用Verilog HDL描述的電路設計就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語言也是一種結構

2023-05-22 15:53:23 1468

1468

Verilog 是一種用于數字邏輯電路設計的硬件描述語言,可以用來進行數字電路的仿真驗證、時序分析、邏輯綜合。

2023-06-10 10:04:44 2658

2658

?? ? ? ? 這本書是專門為電路設計工程師寫的。它主要描述了模擬電路原理在高速數字電路設計中 的分析應用。通過列舉很多的實例,作者詳細分析了一直困擾高速電路路設計工程師的鈴流、串 擾和輻射噪音等

2023-08-17 16:57:35 1

1 數字電路用什么儀器測試? 數字電路測試是數字電路設計的重要環節。它是驗證數字電路功能是否按照所期望的方式工作的過程。在數字電路測試過程中,要使用一些專門的儀器來驗證電路是否按照設計預期的方式工作

2023-09-19 16:33:13 2126

2126 高速數字電路設計

2022-12-30 09:22:18 23

23 高速數字電路設計教材-華為

2022-12-30 09:22:18 54

54 電子發燒友網站提供《FPGA/CPLD數字電路設計經驗分享.pdf》資料免費下載

2023-11-21 11:03:12 5

5 數字電路設計的仿真驗證流程是確保設計能夠正確運行的重要步驟之一。在現代電子設備中,數字電路被廣泛應用于各種應用領域,如計算機、通信設備、汽車電子等等。因此,設計師必須通過仿真驗證來確保電路能夠按照

2024-01-02 17:00:43 3470

3470 Verilog語言是一種硬件描述語言(HDL),用于描述數字邏輯電路和系統。它是一種非常強大且廣泛使用的語言,在數字電路設計中扮演著重要的角色。其中, inout 是Verilog中的一種信號類型

2024-02-23 10:15:48 4944

4944 Verilog是一種硬件描述語言,用于描述數字電路的行為和結構。與其他編程語言相比,Verilog具有與硬件緊密結合的特點,因此其接口機制也有一些與眾不同之處。本文將詳細介紹Verilog與其他編程

2024-02-23 10:22:37 1488

1488 使用Verilog進行數字電路設計是一個復雜但有序的過程,它涉及從概念設計到實現、驗證和優化的多個階段。以下是一個基本的步驟指南,幫助你理解如何使用Verilog來設計數字電路: 1. 明確設計需求

2024-12-17 09:47:12 1861

1861 在現代電子設計自動化(EDA)領域,Verilog作為一種硬件描述語言,已經成為數字電路設計和驗證的標準工具。它允許設計師以高級抽象的方式定義電路的行為和結構,從而簡化了從概念到硅片的整個設計流程

2024-12-17 09:53:28 1690

1690 文本形式描述電路的行為和結構。 并行性和并發性 :數字電路編程語言支持并行和并發操作的描述,這是數字電路設計中的基本特性。 模塊化 :這些語言支持模塊化設計,允許設計師將復雜的電路分解為更小、更易于管理的部分。 仿真和驗證 :數字電路

2025-01-24 09:39:18 1480

1480 本文介紹了數字電路設計中“前端”和“后端”的區別。 數字電路設計中“前端”和“后端”整個過程可類比蓋一棟大樓:前端好比建筑師在圖紙上進行功能和布局的抽象設計,后端則是工程隊把圖紙變成實體建筑的過程

2025-02-12 10:09:55 1502

1502

電子發燒友App

電子發燒友App

評論