數(shù)字電路設(shè)計(jì)全流程解析來啦!

數(shù)字電路設(shè)計(jì)是數(shù)字電路最為關(guān)鍵及重要的一步,今天我們將從各個(gè)流程為大家介紹完整的數(shù)字電路設(shè)計(jì)!

1總述

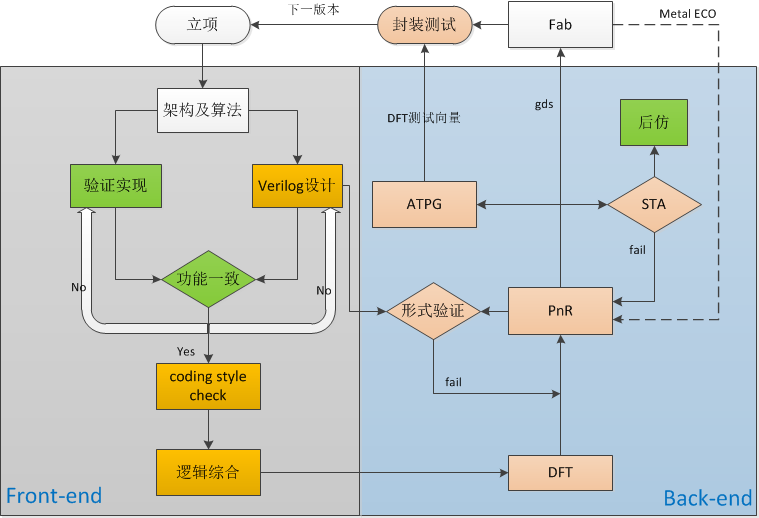

數(shù)字電路設(shè)計(jì)的基本流程如下圖。大致可以分為立項(xiàng),架構(gòu)和算法,設(shè)計(jì)/驗(yàn)證,代碼風(fēng)格檢查、綜合、DFT設(shè)計(jì)、后端PnR,靜態(tài)時(shí)序分析STA,后仿,流片,封裝測(cè)試。之后根據(jù)測(cè)試的結(jié)果又會(huì)反饋給下一代的項(xiàng)目形成一個(gè)良性的循環(huán)。

理論上,流片過程中必須的環(huán)節(jié)是Verilog設(shè)計(jì)、邏輯綜合和后端布局布線,因?yàn)橹灰羞@三步,我們就能夠把一個(gè)行為級(jí)的Verilog代碼轉(zhuǎn)換成門級(jí)網(wǎng)表,再通過PnR轉(zhuǎn)換成版圖GDS(Fab所需的版圖二進(jìn)制文件),再把版圖GDS release給Fab完成流片過程。除此之外其他所有的工序和步驟都是為了保證所設(shè)計(jì)代碼的功能和時(shí)序是符合要求的。畢竟在隨著制造工藝越來越先進(jìn)到如今的3nm時(shí)代,一次流片的成本需要幾千萬美金。流片失敗的代價(jià)是非常大的。不僅錯(cuò)過了產(chǎn)品的市場(chǎng)窗口,同時(shí)也對(duì)資金的損失非常大。所以我們需要越來越多額外的工序、需要越來越復(fù)雜的驗(yàn)證方法學(xué)保證設(shè)計(jì)的正確性。

2數(shù)字電路設(shè)計(jì)流程分步驟解析

立項(xiàng):從市場(chǎng)調(diào)研確定需要做一顆什么樣的芯片,芯片的功能是哪些。具體指標(biāo)要達(dá)到什么程度,市面的競(jìng)爭(zhēng)對(duì)手有哪些。成功流片能夠拿到多少市場(chǎng)份額,能夠?qū)井a(chǎn)生多少利潤(rùn),現(xiàn)金流等等

確定需要投入到這顆芯片的人力、物力和財(cái)力。規(guī)劃好芯片的流片時(shí)間,制定項(xiàng)目計(jì)劃和進(jìn)度表。安排所有人員的工作以及schedule并隨時(shí)跟蹤

架構(gòu)計(jì)算法:算法部門通過仿真建模確定每個(gè)部分的計(jì)算精度,量化控制,以及采用的計(jì)算方式等等

Architecture部門確定芯片的整體布局和架構(gòu),確定芯片最頂層的工作模式,子模塊之間如何聯(lián)動(dòng)工作,芯片的性能,功耗,面積等各種參數(shù)

Verilog 設(shè)計(jì):本課程的重點(diǎn)內(nèi)容。

課程詳情及試聽課進(jìn)入小程序查看:

通過Verilog這種硬件描述語言實(shí)現(xiàn)所需的各種功能。

注意設(shè)計(jì)中所有的代碼必須是可綜合代碼

驗(yàn)證:另一門驗(yàn)證課程的重點(diǎn)內(nèi)容

課時(shí)介紹:

課程詳情及試聽課進(jìn)入小程序查看:

如何用system Verilog以及UVM對(duì)被測(cè)RTL進(jìn)行邏輯功能的驗(yàn)證

主要集中考慮如何創(chuàng)建更多的測(cè)試用例保證所有的輸入組合都能夠遍歷到,同時(shí)在所有遍歷輸入時(shí)輸出都是符合預(yù)期的

通過代碼覆蓋率、功能覆蓋率等保證驗(yàn)證的完備性

同時(shí)考慮驗(yàn)證平臺(tái)的自動(dòng)化,可移植性和可復(fù)用性等等

Coding Style check:一般采用spyglass工具。檢查電路中的代碼是否有潛在的問題。比如多個(gè)數(shù)相加導(dǎo)致的潛在溢出問題。異步復(fù)位信號(hào)又被當(dāng)成邏輯信號(hào)使用,某一個(gè)信號(hào)即被當(dāng)成異步復(fù)位,又被當(dāng)成異步置位、賦值位寬對(duì)不上、實(shí)例化時(shí)信號(hào)對(duì)應(yīng)不上等等

同時(shí)也會(huì)檢查設(shè)計(jì)中所有的異步設(shè)計(jì)是否有防止亞穩(wěn)態(tài)傳播的電路

邏輯綜合:本課程后續(xù)會(huì)講解邏輯綜合的基本流程

目的是在時(shí)序和面積等約束下把RTL的行為級(jí)Verilog代碼轉(zhuǎn)換成對(duì)應(yīng)工藝的門級(jí)網(wǎng)表。同時(shí)產(chǎn)生約束文件并一起給后端進(jìn)行布局布線

DFT和ATPG:DFT和ATPG本身和芯片的功能是沒有任何相關(guān)性的。

目的主要是為了能夠檢查出Fab在制造過程中意外引入的缺陷。尤其是Fab良率不高時(shí)尤其重要

DFT的原理是通過把設(shè)計(jì)中的每一個(gè)觸發(fā)器轉(zhuǎn)換成帶掃描鏈端口的觸發(fā)器,從而能夠給設(shè)計(jì)中的每一個(gè)觸發(fā)器都賦一個(gè)初值。然后通過不同的初值能夠遍歷電路內(nèi)部每一條線的狀態(tài),從而確定版圖中的每一條在制造過程中是否有缺陷

ATPG則是根據(jù)DFT的掃描鏈產(chǎn)生出這些測(cè)試所需要的測(cè)試向量。并把測(cè)試向量以及期望輸出結(jié)果一起給ATE。ATE由此可以對(duì)每一個(gè)芯片進(jìn)行篩選判斷其是否有制造缺陷

布局布線PnR:

課程詳情及試聽課進(jìn)入小程序查看:

目的是在約束文件的控制下,把綜合產(chǎn)生的門級(jí)網(wǎng)表生成對(duì)應(yīng)工藝的物理版圖。并完成版圖直接的連線

其中主要步驟有FloorPlan,CTS, Placement, Route, DFM等

一般由專門的后端人員負(fù)責(zé)。尤其是對(duì)于IP眾多,連線以及DRC規(guī)則復(fù)雜的芯片

形勢(shì)驗(yàn)證:目的是比較兩個(gè)待測(cè)設(shè)計(jì)的邏輯是否完全一直

其中比較的點(diǎn)主要集中在所有的輸出端和觸發(fā)器端

常用case1:比較綜合后的網(wǎng)表和RTL網(wǎng)表是否一致,防止綜合工具引入的意外錯(cuò)誤

常用case2:比較綜合后網(wǎng)表和后端網(wǎng)表是否一致,防止后端工具引入錯(cuò)誤

常用case3:比較ECO后網(wǎng)表和同樣ECO后RTL功能是否一致,保證網(wǎng)表的ECO功能是符合預(yù)期的

靜態(tài)時(shí)序分析STA:主要應(yīng)用于所有的同步電路設(shè)計(jì),檢查其中時(shí)序是否符合要求,對(duì)異步電路是不起作用的。

實(shí)際的制造過程中離子注入摻雜等不可能完全均勻,芯片在工作中溫度和電壓也不可能完全不變,為了保證芯片的時(shí)序在合理范圍內(nèi)都能正常。需要通過STA工具保證芯片在每一種PVT(工藝,電壓,溫度)組合下時(shí)序都能通過

同時(shí)STA工具在發(fā)現(xiàn)時(shí)序問題后還可以進(jìn)行時(shí)序修復(fù)

后仿:速度非常慢,比前仿慢數(shù)十倍,所以一般只跑幾個(gè)典型的工作場(chǎng)景

理論上STA和形勢(shì)驗(yàn)證已經(jīng)能夠保證電路中所有同步電路都能正常工作,但有兩種情況還是需要后仿的輔助:一是設(shè)計(jì)中時(shí)序的約束意外寫錯(cuò)了,只能通過后仿發(fā)現(xiàn)。二是設(shè)計(jì)中異步電路的問題也只能通過后仿才能發(fā)現(xiàn)

流片 Tape Out:把后端生成的GDS二進(jìn)制文件發(fā)送給Fab

一般需要2~3個(gè)月完成

掩膜版是流片中最貴的部分。一般Fab會(huì)把制造過程大致分為兩個(gè)階段。第一階段是基礎(chǔ)Base layer掩膜版制造階段。此時(shí)若設(shè)計(jì)發(fā)現(xiàn)問題,可以通過修改metal解決,那么metal層的掩膜版可以直接用新的。節(jié)省資金。第二階段是metal層掩膜版制造。此時(shí)如果發(fā)現(xiàn)問題并可以通過修改metal解決,那么只能重新制造掩膜版,但相比完整重新流片還是可以節(jié)省不少時(shí)間和資金

ECO:如前所述,芯片在制造或者測(cè)試過程中發(fā)現(xiàn)問題,如果流程從頭開始走一遍來修復(fù)該問題,費(fèi)時(shí)長(zhǎng)同時(shí)消耗資金。

如果發(fā)現(xiàn)的問題比較簡(jiǎn)單。能夠使用電路中預(yù)留的冗余單元,并修改一些金屬連線就能修復(fù)該問題,那么就可以極大的節(jié)省時(shí)間和開支

此過程修改只能直接基于網(wǎng)表,為了保證網(wǎng)表修改沒有錯(cuò)誤,需要用形勢(shì)驗(yàn)證工具保證修改后的網(wǎng)表功能和直接改RTL功能是一致的

封裝與測(cè)試:根據(jù)芯片的速度、功耗等要求可以進(jìn)行Flip-chip,BGA等各種封裝

一般先由ATE進(jìn)行芯片篩選。篩選后通過的片子再進(jìn)行進(jìn)一步的功能測(cè)試

測(cè)試發(fā)現(xiàn)的問題需要設(shè)計(jì)和驗(yàn)證人員進(jìn)行復(fù)現(xiàn)。確定能夠復(fù)現(xiàn)問題后再?zèng)Q定是否需要修改,或者可以在軟件層面繞過

審核編輯:湯梓紅

-

電路設(shè)計(jì)

+關(guān)注

關(guān)注

6745文章

2738瀏覽量

219990 -

Verilog

+關(guān)注

關(guān)注

30文章

1374瀏覽量

114640 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1662瀏覽量

83491

原文標(biāo)題:【干貨】數(shù)字電路設(shè)計(jì)全流程是什么樣的?

文章出處:【微信號(hào):feifeijiehaha,微信公眾號(hào):電路和微電子考研】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

數(shù)字電路和模擬電路的差異解析

有源邏輯探頭的具體應(yīng)用

掌握數(shù)字設(shè)計(jì)基礎(chǔ):邁向芯片設(shè)計(jì)的第一步

SOSET索斯特分享:無源晶振電路設(shè)計(jì)指南

高速數(shù)字電路設(shè)計(jì)與安裝技巧

數(shù)字電路設(shè)計(jì)

華大九天Empyrean Liberal工具助力數(shù)字集成電路設(shè)計(jì)

老工程師分享的模電設(shè)計(jì)經(jīng)驗(yàn)

如何學(xué)好電路設(shè)計(jì)?(文末分享電路設(shè)計(jì)資料合集)

數(shù)字電路設(shè)計(jì)的基本流程

數(shù)字電路設(shè)計(jì)的基本流程

評(píng)論