1. 前言

在數(shù)字電路課程中,老師在講組合邏輯的時(shí)候,一般都會(huì)講競(jìng)爭(zhēng)與冒險(xiǎn)。sky當(dāng)時(shí)也聽的云里霧里,沒有想清楚如下問題:

1) 競(jìng)爭(zhēng)與冒險(xiǎn)究竟是什么東西?有啥物理現(xiàn)象?

2) 在數(shù)字電路設(shè)計(jì)中,什么時(shí)候需要關(guān)心(分析)競(jìng)爭(zhēng)與冒險(xiǎn)?

3) 如何避免競(jìng)爭(zhēng)與冒險(xiǎn)導(dǎo)致的問題呢?

經(jīng)過多年實(shí)際工作的實(shí)踐與理解,在此文略作分析。

2. 競(jìng)爭(zhēng)與冒險(xiǎn)的產(chǎn)生

在數(shù)字電路中,調(diào)用一個(gè)AND gate,用verilog可以如下描述:

assign out = in0 & in1;

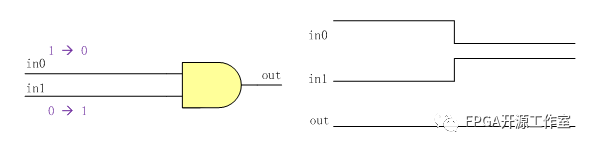

其綜合后對(duì)應(yīng)的電路與波形如下:

如果in0/in1分別有1--》0/0--》1的變化,如果同時(shí)滿足如下兩個(gè)條件:

1) in0/in1同時(shí)變化;

2) 從in0/in1的driver到AND gate的delay絕對(duì)匹配;

則,AND gate的輸出端不會(huì)有毛刺,一直穩(wěn)定的輸出logic 0。

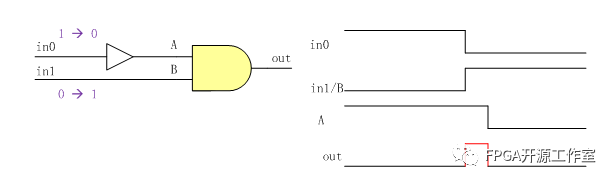

但是在實(shí)際電路中,經(jīng)過place & route后,如上兩個(gè)條件基本不能滿足。抽象簡(jiǎn)化后,實(shí)際電路和波形如下:

可以看到,由于in0/in1到AND gate輸入pin上delay的不匹配,導(dǎo)致AND的輸出out出現(xiàn)一個(gè)logic 1的小脈沖,一般也叫毛刺(glitch)。

對(duì)于一個(gè)簡(jiǎn)單的AND gate,就會(huì)產(chǎn)生毛刺;那么對(duì)于一個(gè)更復(fù)雜的電路,比如:加法器,乘法器,glitch更是起起伏伏,直到一定的時(shí)間后,才會(huì)輸出穩(wěn)定的值。

這就是信號(hào)的競(jìng)爭(zhēng)與冒險(xiǎn):邏輯上(真值表)輸入的變化本來不會(huì)導(dǎo)致組合邏輯輸出的變化;但是因?yàn)樵谳斎脒壿媑ate的PIN上,輸入信號(hào)變化時(shí)間上的差異,導(dǎo)致組合邏輯的輸出端產(chǎn)生一些不必要的0--》1/1--》0變化,出現(xiàn)glitch。

3. 競(jìng)爭(zhēng)與冒險(xiǎn)分析

A. 對(duì)于同步電路(比如DFF的clk是同一個(gè)信號(hào)),我們需要分析(關(guān)心)競(jìng)爭(zhēng)與冒險(xiǎn)嗎?

答案是不需要。

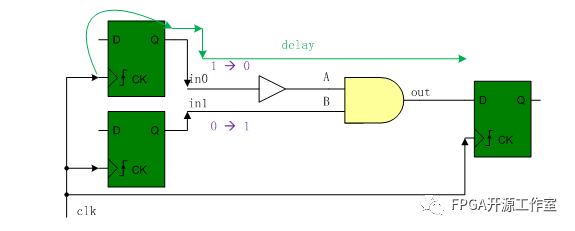

在實(shí)際同步數(shù)字電路中,組合邏輯通常伴隨時(shí)序邏輯(DFF等),其結(jié)構(gòu)如下圖:

因?yàn)樵谕诫娐分校覀儠?huì)做STA時(shí)序分析,計(jì)算每條path的delay(如上圖綠色線)。AND gate在各條path的最大delay后,out PIN上的信號(hào)是穩(wěn)定不變的。再分析后級(jí)DFF是否滿足setup/hold timing需求,則后級(jí)DFF一定采樣到out PIN上穩(wěn)定的輸出值,而非中間的glitch。

也就是說:在同步電路中,我們利用STA分析,已經(jīng)把out PIN產(chǎn)生glitch的期間給濾除(mask)掉了;只要后級(jí)DFF的setup/hold timing分析pass,則后級(jí)DFF肯定采樣到正確的邏輯計(jì)算值,不會(huì)采樣到毛刺。

B. 對(duì)于異步電路(比如DFF的clk不是同一個(gè)信號(hào)),我們需要分析(關(guān)心)競(jìng)爭(zhēng)與冒險(xiǎn)嗎?

答案是需要。

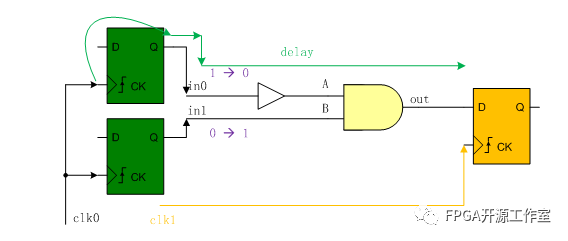

在實(shí)際異步數(shù)字電路中,組合邏輯也通常伴隨時(shí)序邏輯(DFF等),其結(jié)構(gòu)如下圖:

在異步電路中,我們?cè)谧鯯TA時(shí)序分析,會(huì)有困難。雖然我們?nèi)匀荒軠?zhǔn)確計(jì)算每條path的delay(如上圖綠色線),但是我們無法預(yù)知clk0/clk1的相位(phase)關(guān)系,導(dǎo)致無法分析后級(jí)DFF的setup/hold time,即:我準(zhǔn)確計(jì)算out PIN在glitch產(chǎn)生期間是否會(huì)有clk1的上升沿。在工程實(shí)踐中,一般是設(shè)置:set_flase_path -from clk0 -to clk1。這樣,后級(jí)DFF(圖中橙色DFF)可能會(huì)采樣到毛刺。

這時(shí),我們就得關(guān)心glitch了,即競(jìng)爭(zhēng)與冒險(xiǎn)。

不是說了不能計(jì)算了嗎?那怎么“關(guān)心”呢?

既然不能計(jì)算,就從電路結(jié)構(gòu)上解決問題:

通過增加一個(gè)clk0 domain的DFF,讓clk0--》clk1的數(shù)據(jù)交互是DFF輸出,是不是就肯定不會(huì)有g(shù)litch啦 ^_^。“out_reg”PIN是DFF輸出,不會(huì)有g(shù)litch的。

啊,講到這兒,是否突然明白,老師講:跨時(shí)鐘域時(shí),信號(hào)一定要DFF的Q端直接輸出。

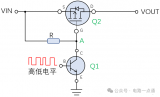

C. 還有哪兒需要分析(關(guān)心)競(jìng)爭(zhēng)與冒險(xiǎn)嗎?

當(dāng)然是有的。

比如:chip IO上的異步信號(hào)。比如IIC接口的SCL/SDA。這2信號(hào)在chip輸出時(shí),是不是應(yīng)該(必須)用DFF輸出呢?不能搞組合邏輯輸出,否則接收方chip可能看到SCL上的glitch,導(dǎo)致功能錯(cuò)誤。

4. 總結(jié)

綜上:

1) 在同步電路中,我們并不關(guān)心競(jìng)爭(zhēng)與冒險(xiǎn),因?yàn)橛蠸TA做保障;

2) 在異步電路中,我們關(guān)心競(jìng)爭(zhēng)與冒險(xiǎn)(從電路結(jié)構(gòu)解決問題),因?yàn)闆]有STA做保障;

編輯:jq

-

同步電路

+關(guān)注

關(guān)注

1文章

61瀏覽量

13778 -

STA

+關(guān)注

關(guān)注

0文章

52瀏覽量

19615 -

SCL

+關(guān)注

關(guān)注

1文章

244瀏覽量

18060

原文標(biāo)題:數(shù)字IC/FPGA設(shè)計(jì)基礎(chǔ)_競(jìng)爭(zhēng)與冒險(xiǎn)

文章出處:【微信號(hào):bianpinquan,微信公眾號(hào):變頻圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

數(shù)字電路和模擬電路的差異解析

門控時(shí)鐘(Clock-gating)介紹

有源邏輯探頭的具體應(yīng)用

飛凌嵌入式ElfBoard-文件I/O的了解探究之競(jìng)爭(zhēng)冒險(xiǎn)

掌握數(shù)字設(shè)計(jì)基礎(chǔ):邁向芯片設(shè)計(jì)的第一步

高速數(shù)字電路設(shè)計(jì)與安裝技巧

在NUC505中選擇從內(nèi)部SPI閃存模式啟動(dòng)時(shí),電路設(shè)計(jì)需要注意什么呢?

數(shù)字電路設(shè)計(jì)

最全的硬件工程師筆試試題集

如何學(xué)好電路設(shè)計(jì)?(文末分享電路設(shè)計(jì)資料合集)

數(shù)字電路設(shè)計(jì)中什么時(shí)候需要分析競(jìng)爭(zhēng)與冒險(xiǎn)

數(shù)字電路設(shè)計(jì)中什么時(shí)候需要分析競(jìng)爭(zhēng)與冒險(xiǎn)

評(píng)論