使用 C 語言的OpenCL 2a并行編程擴(kuò)展來補(bǔ)充基于 FPGA 的 CNN 加速應(yīng)用程序的開發(fā)。適用于卷積神經(jīng)網(wǎng)絡(luò)的 FPGA 器件的一個示例是英特爾可編程解決方案集團(tuán) (PSG)的Arria 10系列器件,其正式名稱為Altera。

2022-08-02 15:13:16 3248

3248

一個叫做GUNNESS的全新的開源工具,可以幫助用戶通過SDSoC 開發(fā)環(huán)境很輕松的將二值化神經(jīng)網(wǎng)絡(luò)(BNNs)實(shí)現(xiàn)在Zynq SoC芯片和Zynq UltraScale+ MPSoC芯片上。GUINNESS基于GUI工具而開發(fā),內(nèi)部實(shí)現(xiàn)利用深度學(xué)習(xí)框架來訓(xùn)練一個二值的CNN。

2017-10-17 09:49:08 11295

11295 近來卷積神經(jīng)網(wǎng)絡(luò)(CNN)的研究十分熱門。CNN發(fā)展的一個瓶頸就是它需要非常龐大的運(yùn)算量,在實(shí)時性上有一定問題。而FPGA具有靈活、可配置和適合高并行度計算的優(yōu)點(diǎn),十分適合部署CNN。 快速開始

2020-11-09 17:28:59 2979

2979

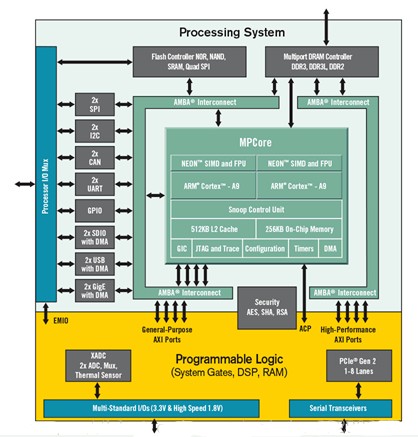

在Zynq MPSoC的器件里,PS (Processing System )集成了三個看門狗,分別是CSU SWDT,LPD SWDT和FPD SWDT。

2023-06-30 09:47:22 2983

2983

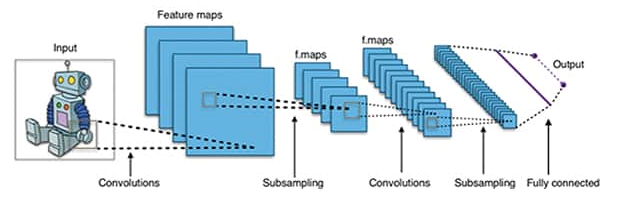

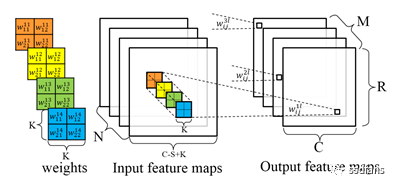

CNN算法簡介

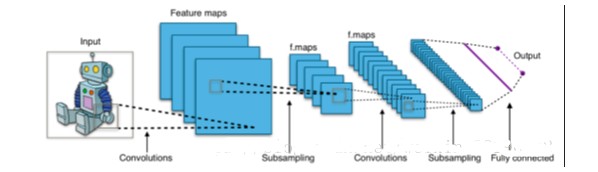

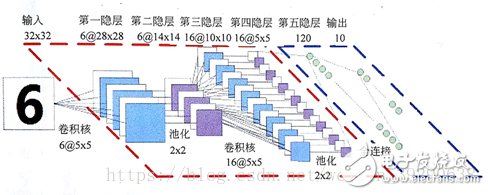

我們硬件加速器的模型為Lenet-5的變型,網(wǎng)絡(luò)粗略分共有7層,細(xì)分共有13層。包括卷積,最大池化層,激活層,扁平層,全連接層。下面是各層作用介紹:

卷積層:提取特征。“不全

2025-10-29 07:49:25

?如何使用 Zynq-7000 SoC?Zynq-7000SoC 設(shè)計和開發(fā)高層次綜合Zynq-7000 SoC 上的操作系統(tǒng)教育、研究和培訓(xùn)

2014-09-04 11:37:18

你好,我想在VADJ(2.5V)和GPIO引腳之間連接6mA負(fù)載(LED)。 Zynq 7020有可能嗎?Zynq上GPIO引腳的最大電流是多少?謝謝。以上來自于谷歌翻譯以下為原文Hello,I

2019-03-11 12:50:20

是怎樣實(shí)現(xiàn)對自己的配置? 這也是本文將要和大家共同討論的問題。 Zynq的啟動流程 在無 JTAG 的模式下,Zynq 是通過片上CPU完成對芯片的配置,也就是PS和PL的配置是通過 PS 處理器

2021-01-08 16:33:01

各位i大神,小弟最近遇到了zynq上無法啟動linux的問題,不知道哪里的錯誤都是按照xilinx官網(wǎng)做的。。thanks

2014-07-07 12:40:30

你好我想制作一個具有中斷信號的自定義IP。我正在尋找這個中斷信號的規(guī)格。我在哪里可以找到這個規(guī)格?例如水平或邊緣檢測器如果它是水平檢測器,它應(yīng)該停留多長時間?我正在使用ZYNQ ZC706板。如果你

2019-04-10 11:49:23

在zynq7000上使用rtt,來移植SD卡驅(qū)動和文件系統(tǒng),出現(xiàn)問題

2022-03-30 13:45:02

在FPGA上加速過winograd嗎,有沒有和arm端做過加速結(jié)果比較

2022-09-21 11:28:56

TF之CNN:CNN實(shí)現(xiàn)mnist數(shù)據(jù)集預(yù)測 96%采用placeholder用法+2層C及其max_pool法+隱藏層dropout法+輸出層softmax法+目標(biāo)函數(shù)cross_entropy法+

2018-12-19 17:02:40

TF之CNN:Tensorflow構(gòu)建卷積神經(jīng)網(wǎng)絡(luò)CNN的嘻嘻哈哈事之詳細(xì)攻略

2018-12-19 17:03:10

在TensorFlow中實(shí)現(xiàn)CNN進(jìn)行文本分類(譯)

2019-10-31 09:27:55

Vivado HLS視頻庫加速Zynq-7000 All Programmable SoC OpenCV應(yīng)用加入賽靈思免費(fèi)在線研討會,了解如何在Zynq?-7000 All Programmable

2013-12-30 16:09:34

因為最近要用到zynq芯片,我希望能在zynq芯片上使用freeRTOS,但是弄不明白怎么移植進(jìn)去。一般xillinx sdk在工程里面添加操作系統(tǒng)的方法是,在repository里先安裝相應(yīng)的庫

2020-06-11 04:35:29

大家好,我使用zynq 7020開發(fā)板,其自定義架構(gòu)不支持SD卡,但支持QSPI閃存。我通過在SDK中使用以下bif文件創(chuàng)建zynq啟動映像來構(gòu)建.msc文件 [bootloader] zynq

2020-07-30 16:24:39

項目名稱:基于ZYNQ的圖像算法加速試用計劃:本人在FPGA設(shè)計有三年多的工作經(jīng)驗,對zynq,做過petalinux移植、非petalinux的Ubuntu移植、基于lwip的數(shù)據(jù)處理系統(tǒng)、ps

2019-09-18 14:17:42

項目名稱:基于ZYNQ的人臉識別系統(tǒng)試用計劃:申請理由本人為某學(xué)校博士生,從事計算機(jī)視覺,深度學(xué)習(xí),及其硬件加速的研究。有一定FPGA編程經(jīng)驗(VHDL),和嵌入式ARM,Arduino版的開發(fā)經(jīng)驗

2019-10-30 17:03:42

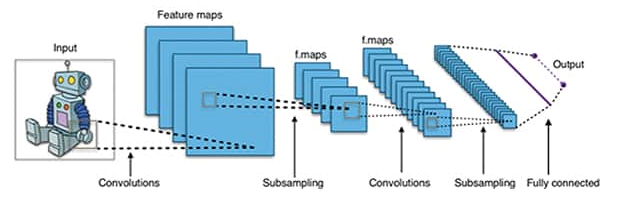

連接層、卷積層、池化層、激活層等。

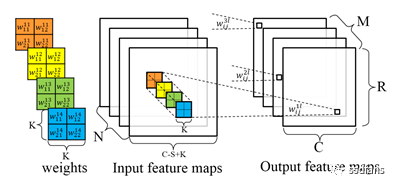

多層感知器包含全連接層和激活層,CNN在多層感知器的基礎(chǔ)上加入了卷積層(池化層其實(shí)也是卷積運(yùn)算,用來減少數(shù)據(jù)規(guī)模的)

2.1 Dense層(全連接層)

全連接層

2023-08-18 06:56:34

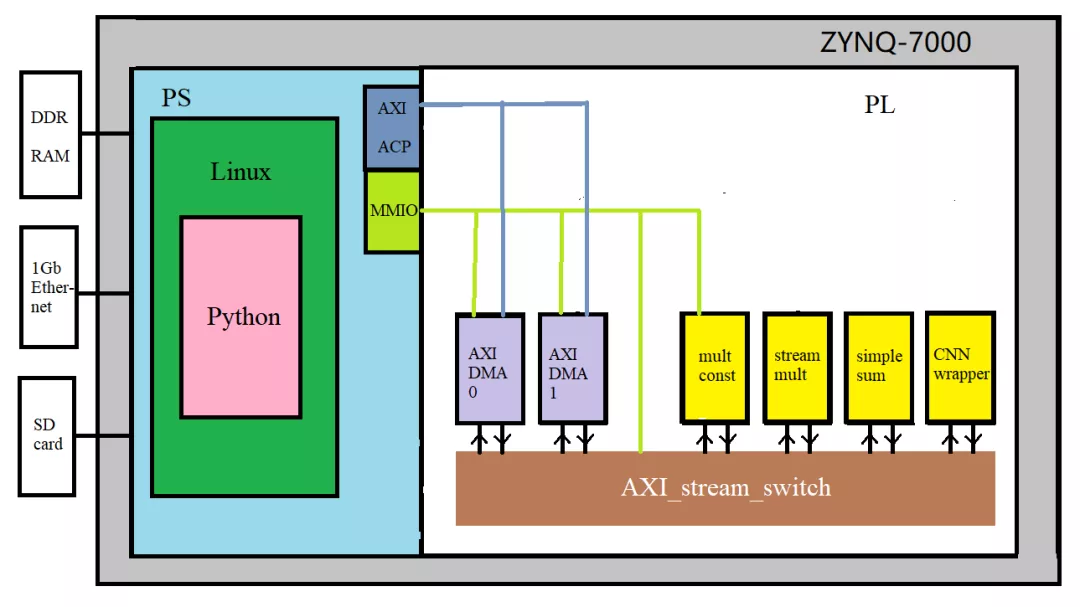

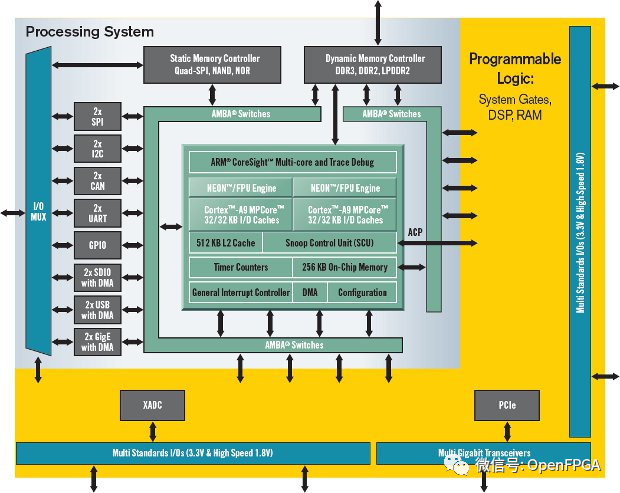

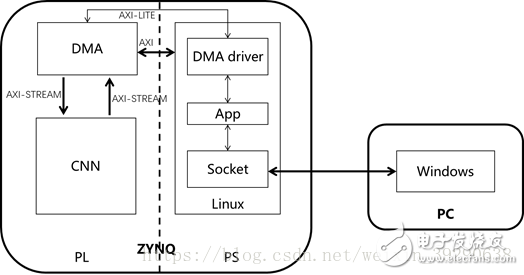

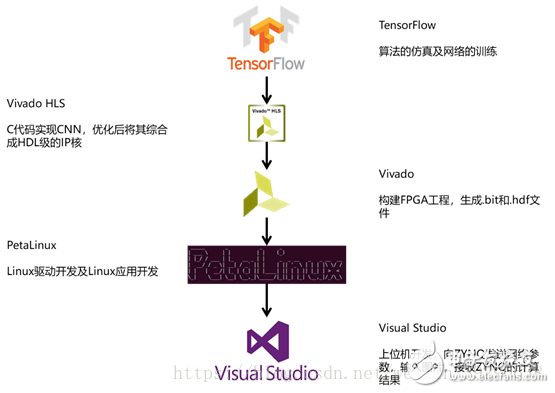

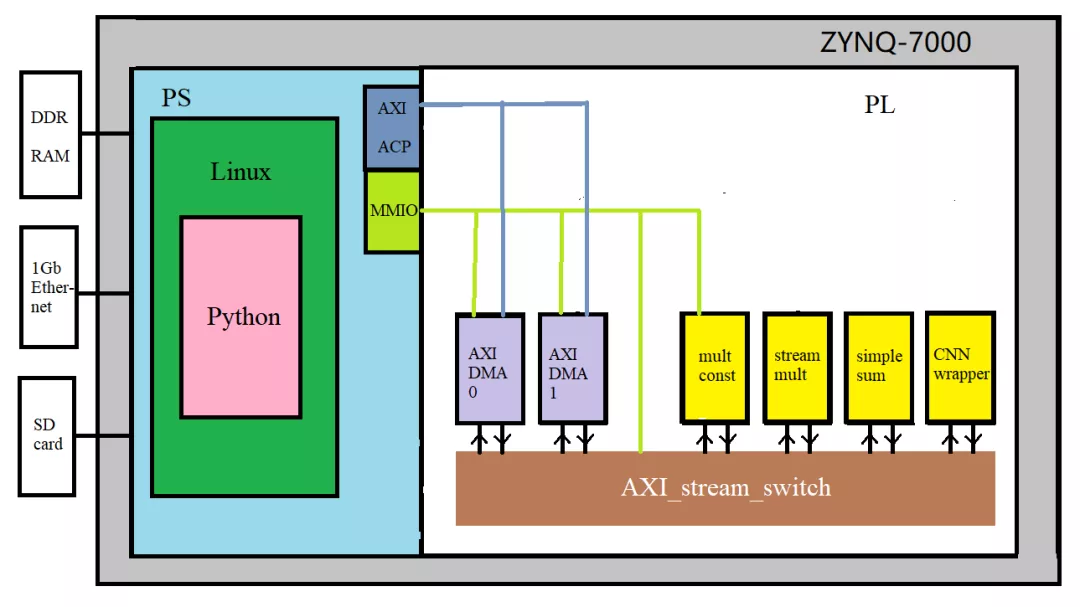

識別網(wǎng)絡(luò)LeNet5(圖3)為例,提出一種在ZYNQ上加速CNN的工程方法。LeNet5在兩層CNN后加入了全連接層和softmax分類器,實(shí)現(xiàn)了對10種數(shù)字手寫體的分類。 系統(tǒng)框架 ZYNQ上

2021-01-15 17:09:15

你好我使用 STM32CUBE-AI v5.1.2 ApplicationTemplate 將簡單的 CNN 導(dǎo)入到 STM32L462RCT我發(fā)現(xiàn)壓縮模型對推理時間沒有影響。aiRun 程序在 8

2023-01-29 06:24:08

了對 HLS 的理解,開始初步掌握使用 HLS 進(jìn)行并行性編程的方法。我們學(xué)習(xí)了 PYNQ 框架,在 PYNQ-Z2 上實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)加速 電路,有了軟硬件協(xié)同開發(fā)的經(jīng)歷。除此之外,我們還學(xué)習(xí)了

2023-06-20 19:45:12

基于數(shù)字CNN與生物視覺的仿生眼設(shè)計在充分研究第一代視覺假體功能的基礎(chǔ)上,利用細(xì)胞神經(jīng)網(wǎng)絡(luò)(CNN)的圖像處理能力,結(jié)合生物視覺中信息加工與編碼的原理,設(shè)計了一款符合第一代視覺假體功能的仿生眼

2009-09-19 09:35:15

【技術(shù)綜述】為了壓榨CNN模型,這幾年大家都干了什么

2019-05-29 14:49:27

如何使用Windows在Zynq 7000主板上啟動linux?在Linux中我有終端可以請你建議是否有任何Windows終端以上來自于谷歌翻譯以下為原文How can I boot linux

2019-04-09 13:12:21

賽靈思和 DornerWorks 的系統(tǒng)軟件團(tuán)隊在賽靈思的 Zynq? Ultrascale+? MPSoC 上啟動 Xen Project 管理程序時,我們發(fā)現(xiàn)可通過運(yùn)行當(dāng)年叱詫一時的流行電子游戲

2019-10-09 06:21:21

。 但是要了解CNN的工作原理,我們需要了解如何將圖像存儲在計算機(jī)中。 上面的向我們展示了如何以數(shù)組形式存儲圖像。 但是,這些只是灰度圖像。因此,RGB或彩色圖像是3個這樣的矩陣彼此堆疊

2020-07-16 18:13:11

MIMRTX1064(SDK2.13.0)的KWS demo中放置了ds_cnn_s.tflite文件,提供demo中使用的模型示例。在 read.me 中,聲明我可以找到腳本,但是,該文檔中的腳本

2023-04-19 06:11:51

訓(xùn)練一個神經(jīng)網(wǎng)絡(luò)并移植到Lattice FPGA上,通常需要開發(fā)人員既要懂軟件又要懂?dāng)?shù)字電路設(shè)計,是個不容易的事。好在FPGA廠商為我們提供了許多工具和IP,我們可以在這些工具和IP的基礎(chǔ)上做

2020-11-26 07:46:03

嗨,我正在嘗試在Zynq設(shè)備上實(shí)現(xiàn)一些簡單的加法器,但是當(dāng)我玩不同的代碼時,我注意到并不總是推斷進(jìn)位鏈,例如:分配{cout,c} = a + b;其中a,b,c是相同寬度的信號。但是,如果聲明c要

2020-03-13 09:42:21

有沒有辦法在Debian上加速Chromium加載和運(yùn)行時間(9)在BBB上拉伸?它在Stretch上的運(yùn)行速度比在相同的BBB H / W上使用Jessie慢得多。以上來自于谷歌翻譯以下為原文

2018-10-22 14:23:16

你好我在Zynq 7010設(shè)計上添加了一個UART 16550 IP,中斷直接連接到Zynq INTC。在petalinux中導(dǎo)入硬件設(shè)計后,pl.dtsi結(jié)構(gòu)似乎沒問題,但是當(dāng)我編譯圖像并啟動板

2020-04-08 07:50:34

玩轉(zhuǎn)Zynq,再深入其中。本實(shí)例,我們要搭建第一個Zynq系統(tǒng)工程,并且在這個Zynq系統(tǒng)的Cortex A9上在線跑一個通過UART打印“HelloZynq!”的軟件程序。當(dāng)然了,重點(diǎn)不是Hello

2019-09-30 12:57:32

我使用SIMULINK中的系統(tǒng)生成器設(shè)計了我的PID控制器浮點(diǎn)。我們可以使用生成的代碼在Zynq 7020 FPGA上實(shí)現(xiàn)設(shè)計嗎?或者我們需要在處理單元(ARM Cortex)上實(shí)現(xiàn)它?換句話說,我可以在FPGA上實(shí)現(xiàn)浮點(diǎn)而不是PS(處理器)嗎?謝謝。丹尼爾·穆罕

2019-09-03 10:14:00

你好我的設(shè)計在zcu 102的PL側(cè)有一個以太網(wǎng)mac。我可以使用zynq板上的Phy嗎?

2019-10-21 10:04:04

led幾次,我發(fā)現(xiàn)無線網(wǎng)絡(luò)連接失敗。換句話說,我只是在整個實(shí)驗中的GPIO操作。為了排除u***無線lan適配器移植的問題,當(dāng)我在zedboard上按照相同的方法,無論gpio操作多少次,無線網(wǎng)絡(luò)連接仍然正常,我想知道我的zynq是否在zc702板上壞了!期待您的幫助!謝謝?布里米

2019-11-06 09:41:45

XAPP1251說明顯示,可以在Zynq ARM處理器上運(yùn)行XVC服務(wù)器來控制FPGA中的JTAG端口。但是,我不清楚,是否可以在同一個FPGA中控制PL JTAG?可以使用運(yùn)行在設(shè)備PS部分上

2020-07-30 13:51:19

高層次綜合設(shè)計最常見的的使用就是為CPU創(chuàng)建一個加速器,將在CPU中執(zhí)行的代碼移動到FPGA可編程邏輯去提高性能。本文展示了如何在Zynq AP SoC設(shè)計中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 4244

4244

,Zynq SoC還大量用于SoM(系統(tǒng)模塊)中,據(jù)安富利高管介紹,安富利的SoM銷量很好,它可以大大加速產(chǎn)品的開發(fā),甚至直接用于量產(chǎn)產(chǎn)品中,下面列出了27款賽靈思合作伙伴的 SoM,這些SoM有各種尺寸和形狀,采用多種賽靈思Zynq型號,而且板上RAM和ROM都

2017-02-09 02:35:13 995

995 為期 ?1? 天的加速器開發(fā)流程介紹主要講解如何測量系統(tǒng)性能、確定什么軟件功能應(yīng)該移至硬件,如何使用 ?Vivado? HLS? 工具裝配一款定制加速器,如何將該定制加速器添加至 ?Zynq SoC? 設(shè)計,以及如何測量加速性能。 了解更多 ??

2017-02-09 06:23:11 557

557 在我的上一篇博客中我介紹了利用Zynq SoC上的兩個ARM Cortex-A9 MPCore處理器執(zhí)行不同的任務(wù)程序,實(shí)現(xiàn)非對稱的多進(jìn)程處理模式的概念。

2017-02-11 10:08:38 3202

3202

人工智能現(xiàn)在是最熱門的技術(shù),已經(jīng)估值10億美元的深鑒科技在2016年的Hot Chip大會上推出了一個卷積神經(jīng)網(wǎng)絡(luò)(CNN)加速器,命名為Aristotle,它是基于Xilinx Zynq All Programmable SoC器件實(shí)現(xiàn)的。

2018-07-10 03:36:00 3040

3040 基于FPGA的通用CNN加速器整體框架如下,通過Caffe/Tensorflow/Mxnet等框架訓(xùn)練出來的CNN模型,通過編譯器的一系列優(yōu)化生成模型對應(yīng)的指令;同時,圖片數(shù)據(jù)和模型權(quán)重數(shù)據(jù)按照優(yōu)化規(guī)則進(jìn)行預(yù)處理以及壓縮后通過PCIe下發(fā)到FPGA加速器中

2017-10-27 14:09:58 10619

10619

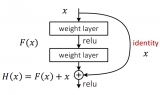

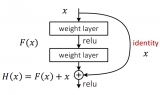

據(jù)帶來的歷史機(jī)遇,CNN在12年迎來了歷史突破。12年之后,CNN的演化路徑可以總結(jié)為四條:1)更深的網(wǎng)絡(luò),2)增強(qiáng)卷積模的功能以及上訴兩種思路的融合,3)從分類到檢測,4)增加新的功能模塊。 開始-LeNet 1998年,LeCun提出LeNet,并成功應(yīng)用于美國手寫數(shù)字識別。

2017-11-15 11:10:09 3064

3064

之前在網(wǎng)上搜索了好多好多關(guān)于CNN的文章,由于網(wǎng)絡(luò)上的文章很多斷章取義或者描述不清晰,看了很多youtobe上面的教學(xué)視頻還是沒有弄懂,最后經(jīng)過痛苦漫長的煎熬之后對于神經(jīng)網(wǎng)絡(luò)和卷積有了粗淺的了解

2017-11-16 13:18:40 59199

59199

熟悉運(yùn)行在賽靈思 Zynq UltraScale+ MPSoC 上的 Xen 管理程序。 賽靈思和 DornerWorks 的系統(tǒng)軟件團(tuán)隊在賽靈思的 Zynq? Ultrascale+? MPSoC

2017-11-16 20:17:53 3872

3872

本教程介紹了如何使用μC/ OS BSP建立在ZYNQ基本應(yīng)用程序?使用Vivado -7000 ? IDE和賽靈思? SDK。在本教程中,您將使用Vivado IP集成器配置ZYNQ處理器系統(tǒng)以及

2017-11-17 15:06:01 9296

9296 通過這篇有趣的教程,熟悉運(yùn)行在賽靈思 Zynq UltraScale+ MPSoC 上的 Xen 管理程序。 賽靈思和 DornerWorks 的系統(tǒng)軟件團(tuán)隊在賽靈思的 Zynq

2017-11-18 18:39:25 3104

3104

。該開發(fā)板加載了Linux Ubuntu操作系統(tǒng),可以在CPU上運(yùn)行現(xiàn)有的Python CNN架構(gòu)如Caffe和Theano。本設(shè)計旨在用PYNQ加載的ZYNQ FPGA對于CNN核心計算進(jìn)行硬件加速

2018-06-29 07:55:00 5289

5289

近日KORTIQ公司推出了一款Xilinx FPGA的CNN加速器IP——AIScale,它能夠利用實(shí)現(xiàn)訓(xùn)練好的CNN網(wǎng)絡(luò),比如行業(yè)標(biāo)準(zhǔn)的ResNet、AlexNet、Tiny Yolo和VGG-16等,并將它們進(jìn)行壓縮輸出二進(jìn)制描述文件,可以部署到Xilinx全系列可編程邏輯器件上。

2018-01-09 08:45:41 10582

10582

通過這篇有趣的教程,熟悉運(yùn)行在賽靈思 Zynq UltraScale+ MPSoC 上的 Xen 管理程序。 賽靈思和 DornerWorks 的系統(tǒng)軟件團(tuán)隊在賽靈思的 Zynq

2018-02-01 01:38:53 1628

1628 掩模(mask)。和前兩個輸出不同,這個新輸出需要提取更精細(xì)的空間布局,為此,Mask R-CNN在Faster-RCNN上添加一個分支網(wǎng)絡(luò):Fully Convolution Networ(FCN)。

2018-07-20 08:53:24 68826

68826 )。這里還要強(qiáng)調(diào)軟件要求避免緩存一致性問題。 在Zynq CPU和HLS加速模塊之間Streaming Data Step 1: 產(chǎn)生HLS IP 這里會產(chǎn)生兩個

2018-10-02 07:25:11 1614

1614 之前在網(wǎng)上搜索了好多好多關(guān)于CNN的文章,由于網(wǎng)絡(luò)上的文章很多斷章取義或者描述不清晰,看了很多youtobe上面的教學(xué)視頻還是沒有弄懂,最后經(jīng)過痛苦漫長的煎熬之后對于神經(jīng)網(wǎng)絡(luò)和卷積有了粗淺的了解

2018-10-02 07:41:01 930

930 這種自動駕駛演示運(yùn)行了當(dāng)今自動系統(tǒng)中常用的三種主要復(fù)雜算法,即卷積神經(jīng)網(wǎng)絡(luò)(CNN),密集光流和立體視覺,所有這些都在一個Zynq Ultrascale + MPSoC器件中。

2018-11-28 07:00:00 2567

2567 ADI公司在Embedded World 2015上展示了采用Zynq SDR套件的DDS HLS IP

2018-11-30 06:44:00 3814

3814 iVeia演示了將Android操作系統(tǒng)移植到Zynq UltraScale + MPSoC上,以獲取角落和邊緣檢測濾波器的實(shí)時視頻和控制系數(shù)。

結(jié)果是使用軟件仿真器QEMU實(shí)現(xiàn)更快的從PS到PL的算法

2018-11-26 06:57:00 6007

6007 該演示展示了Zynq-7000 All Programmable SoC及其使用NEON引擎或硬件加速來加速軟件的能力。

查看Zynq-7000 SoC的靈活性,以加速軟件和利用......

2018-11-26 06:56:00 5750

5750 Xilinx展示了在QEMU軟件仿真器上運(yùn)行的Zynq UltraScale + MPSoC。

四核ARM Cortex-A53在SMP模式下運(yùn)行4個Linux應(yīng)用程序,在雙核ARM Cortex-R5上運(yùn)行裸機(jī)應(yīng)用程序。

2018-11-26 06:46:00 7221

7221 Xilinx展示Zynq UltraScale + MPSoC在由6個FPGA組成的硬件仿真板上運(yùn)行,以實(shí)現(xiàn)四核ARM Cortex-A53,雙核ARM Cortex-R5,核心交換機(jī)互連,圖形控制器,內(nèi)存控制器......

2018-11-26 06:44:00 3947

3947 在本演示中,Intelliprop演示了在Xilinx Zynq UltraScale + MPSoC中實(shí)現(xiàn)的NVMe主機(jī)加速器。

2018-11-26 06:18:00 6966

6966 Kortiq提供易于使用,可擴(kuò)展且小巧的CNN加速器。

該設(shè)備支持所有類型的CNN,并動態(tài)加速網(wǎng)絡(luò)中的不同層類型。

2018-11-23 06:28:00 3804

3804 Mask R-CNN是承繼于Faster R-CNN,Mask R-CNN只是在Faster R-CNN上面增加了一個Mask Prediction Branch(Mask預(yù)測分支),并且在ROI

2019-04-04 16:32:07 13837

13837 上新:Zynq UltraScale+ RFSoC ZCU111 評估套件

2019-07-02 12:04:48 5037

5037 在CNN中,轉(zhuǎn)置卷積是一種上采樣(up-sampling)的方法。如果你對轉(zhuǎn)置卷積感到困惑,那么就來讀讀這篇文章吧。

2020-01-31 17:32:00 5323

5323 因為ZYNQ 的PS 和PL 部分的電源有上電順序的要求,在電路設(shè)計中,按照ZYQN 的電源要求設(shè)計,上電依次為1.0V -> 1.8V -> 1.5 V -> 3.3V -> VCCIO,

2020-01-01 17:27:00 13940

13940

在Zynq UltraScale+ MPSoC 和 Zynq-7000 SoC 系列(16nm 和 28nm)上面向 CNN 4 位 XDPU 實(shí)現(xiàn)的低精度加速器。這種加速器通過高效地映射卷積計算,充分發(fā)揮其 DSP 功能。

2020-09-03 10:00:45 8318

8318

關(guān)注、星標(biāo)公眾號,直達(dá)精彩內(nèi)容來源:ZYNQ作者:watchman最近公司開始做一個項目,再一次使用到ZYNQ,今天給大家科普一下ZYNQ是什么,以及ZYNQ在嵌入式系統(tǒng)中的應(yīng)用情況。Z...

2021-11-02 18:35:59 21

21 電子學(xué)報第七期《一種可配置的CNN協(xié)加速器的FPGA實(shí)現(xiàn)方法》

2021-11-18 16:31:06 15

15 IOS論文出自MIT的韓松實(shí)驗室,第一作者為Yaoyao Ding, 這是他在韓松實(shí)驗室實(shí)習(xí)時的成果。現(xiàn)有的CNN推理加速技術(shù)關(guān)注于優(yōu)化算子內(nèi)部的并...

2022-01-25 18:09:36 0

0 這篇博文特別關(guān)注 Zynq SoC 的多用途 IO (MIO, Multipurpose IO) 模塊。

2022-03-30 11:43:29 3049

3049 然而,由于卷積核的離散性,傳統(tǒng)的 CNN 不能跨分辨率使用。當(dāng)考慮具有相同 CNN 的不同維度數(shù)據(jù)時,這兩個問題會進(jìn)一步加劇,例如序列(1D)、視覺(2D)和高維數(shù)據(jù)(3D、4D),因為不同的維度以

2022-07-21 10:15:21 1680

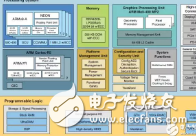

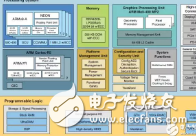

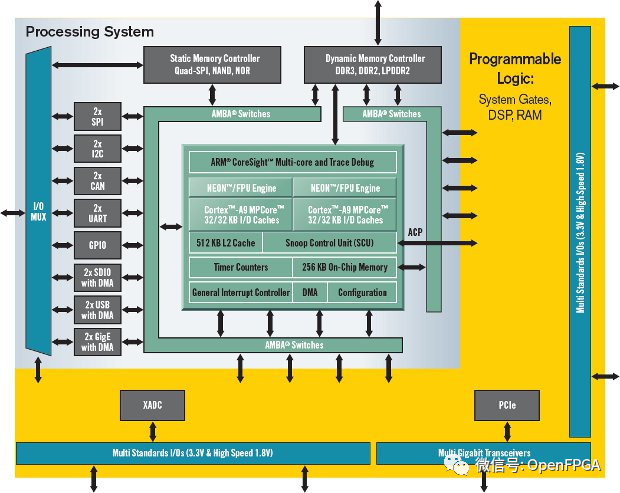

1680 Zynq MPSoC是Zynq-7000 SoC(之后簡稱Zynq)的進(jìn)化版本。Zynq是賽靈思發(fā)布的集成PL(FPGA)和PS設(shè)計的最早的一代產(chǎn)品。如圖2.1所示,在相對較高層次對比了三種器件。Zynq MPSoC的PS部分比Zynq的PS部分面積更大,也更復(fù)雜。本章,將介紹這三種器件的特點(diǎn).

2022-08-15 09:16:38 3750

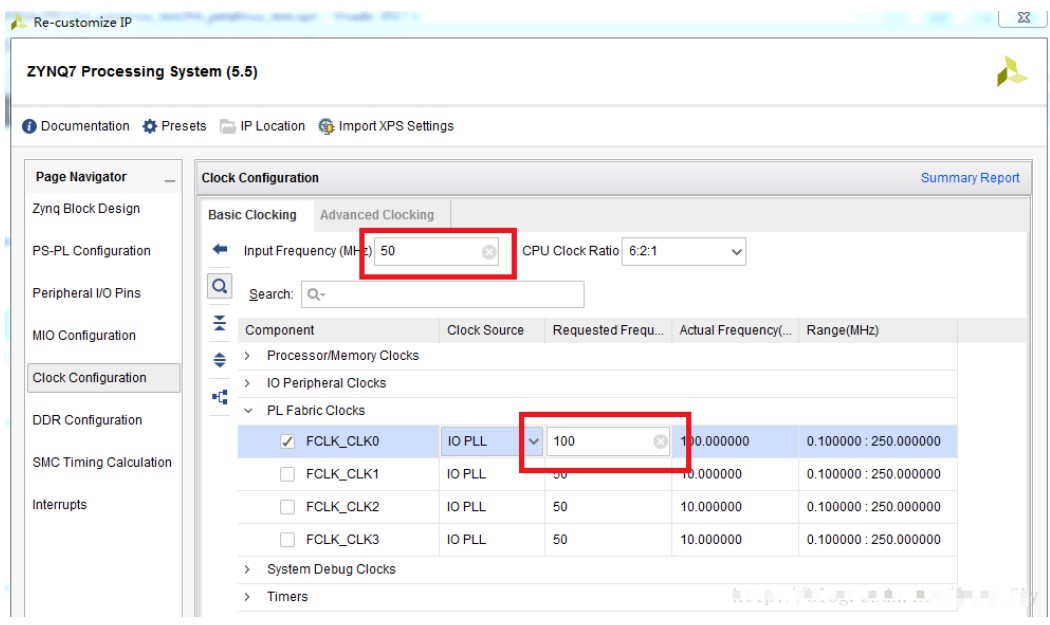

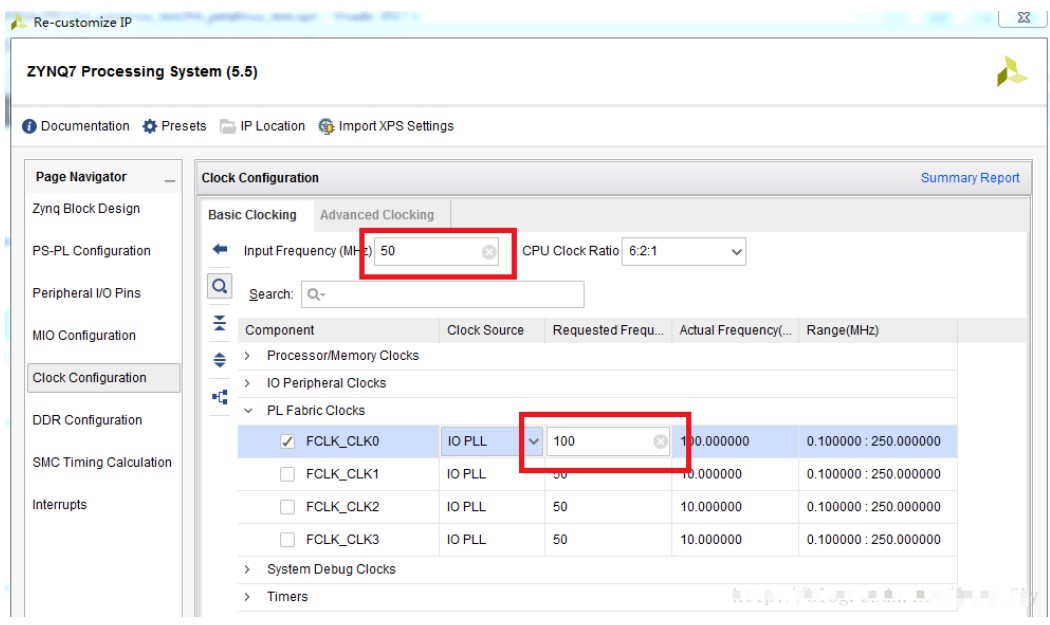

3750 新建工程,并新建一個 BD 文件,然后添加一個ZYNQ Processing system的IP核,并設(shè)置好與硬件相符合的PS和PL時鐘以及DDR型號。

2022-09-06 09:34:29 8331

8331

zynq 中帶有兩個硬核千兆以太網(wǎng)MAC,ENET0,ENET1。與普通SOC 芯片不同,zynq PS 斷地外設(shè)可以通過MIO連接到芯片的引腳上,也可以通過EMIO 接口連接到PL 端。連接到PL端后,帶來了靈活性,可以轉(zhuǎn)換成各種接口。比如設(shè)計一個交換機(jī)。定義端其它的引腳。

2022-09-23 15:19:58 4191

4191 在無 JTAG 的模式下,Zynq 是通過片上CPU完成對芯片的配置,也就是PS和PL的配置是通過 PS 處理器 ARM 核來實(shí)現(xiàn)的。需要注意的是,與傳統(tǒng)的 Xilinx 7 系列 FPGA 芯片不同,Zynq 是不支持從 PL 端進(jìn)行直接啟動配置的,一定要通過 PS 部分來完成。

2022-10-19 09:11:55 2023

2023 電子發(fā)燒友網(wǎng)站提供《Xilinx Zynq上FreeRTOS的Tracealyzer.zip》資料免費(fèi)下載

2022-12-07 14:59:27 5

5 電子發(fā)燒友網(wǎng)站提供《Zynq上使用Vitis的雙ARM Hello World.zip》資料免費(fèi)下載

2022-12-14 10:15:40 3

3 本文重點(diǎn)解釋如何使用硬件轉(zhuǎn)換卷積神經(jīng)網(wǎng)絡(luò)(CNN),并特別介紹使用帶CNN硬件加速器的人工智能(AI)微控制器在物聯(lián)網(wǎng)(IoT)邊緣實(shí)現(xiàn)人工智能應(yīng)用所帶來的好處。 AI應(yīng)用通常需要消耗大量能源,并以

2023-05-16 01:05:03 1905

1905 電子發(fā)燒友網(wǎng)站提供《PyTorch教程14.8之基于區(qū)域的CNN(R-CNN).pdf》資料免費(fèi)下載

2023-06-05 11:09:06 0

0 14.8。基于區(qū)域的 CNN (R-CNN)? Colab [火炬]在 Colab 中打開筆記本 Colab [mxnet] Open the notebook in Colab

2023-06-05 15:44:37 1314

1314

因為CNN的特有計算模式,通用處理器對于CNN實(shí)現(xiàn)效率并不高,不能滿足性能要求。 因此,近來已經(jīng)提出了基于FPGA,GPU甚至ASIC設(shè)計的各種加速器來提高CNN設(shè)計的性能。

2023-06-14 16:03:43 3135

3135

作者:TraptiKalra來源:AI公園,編譯:ronghuaiyang導(dǎo)讀本文分析了常見的紋理數(shù)據(jù)集以及傳統(tǒng)CNN在紋理數(shù)據(jù)集分類上效果不佳的原因。在機(jī)器視覺任務(wù)中,將紋理分析與深度學(xué)習(xí)結(jié)合

2022-09-23 14:26:46 1314

1314

它用TensorFlow.js加載了一個10層的預(yù)訓(xùn)練模型,相當(dāng)于在你的瀏覽器上跑一個CNN模型,只需要打開電腦,就能了解CNN究竟是怎么回事。

2023-06-28 14:47:09 5240

5240

,具有非常強(qiáng)的表征能力。在本文中,我們將詳細(xì)介紹CNN的原理和特點(diǎn)。 一、CNN的原理 1. 卷積操作 CNN最顯著的特點(diǎn)是卷積操作。卷積是一種數(shù)學(xué)運(yùn)算,它通過一個濾波器在原數(shù)據(jù)上滑動,并輸出一個新的特征圖。卷積操作可以提取原始圖像的局部特征信息,同時保留空間關(guān)系和共性特征。

2023-08-21 17:15:25 2508

2508 以解決圖像識別問題為主要目標(biāo),但它的應(yīng)用已經(jīng)滲透到了各種領(lǐng)域,從自然語言處理、語音識別、到物體標(biāo)記以及醫(yī)療影像分析等。在此,本文將對CNN的原理、結(jié)構(gòu)以及基礎(chǔ)代碼進(jìn)行講解。 1. CNN的原理 CNN是一種能夠自動提取特征的神經(jīng)網(wǎng)絡(luò)結(jié)構(gòu),它的每個層次在進(jìn)行特征提取時會自動適應(yīng)輸入數(shù)據(jù)

2023-08-21 17:16:13 3815

3815 電子發(fā)燒友網(wǎng)站提供《隔離Zynq UltraScale+設(shè)備上的關(guān)鍵安全應(yīng)用程序.pdf》資料免費(fèi)下載

2023-09-15 10:33:30 0

0 電子發(fā)燒友網(wǎng)站提供《隔離Zynq UltraScale+設(shè)備上的安全關(guān)鍵應(yīng)用.pdf》資料免費(fèi)下載

2023-09-15 09:36:14 0

0 Step3: 按照“Vivado中進(jìn)行ZYNQ硬件部分設(shè)計”中介紹的,直到在SDK中編寫C代碼步驟。需要使用UART進(jìn)行通行,分為通過UART向外發(fā)送數(shù)據(jù)和通過UART接收數(shù)據(jù)。

2023-09-23 09:25:59 2287

2287

該項目演示如何在 Zynq SoC 上開始使用 FreeRTOS。

2023-10-18 09:44:15 4242

4242

Zynq器件將arm和FPGA結(jié)合,利用了兩者各自的優(yōu)勢,arm可以實(shí)現(xiàn)靈活的控制,而FPGA部分可以實(shí)現(xiàn)算法加速,這大大擴(kuò)展了zynq的應(yīng)用。比如深度學(xué)習(xí)加速,圖像處理等等。PL側(cè)表示FPGA的邏輯部分,PS側(cè)為arm端以及一些AXI接口控制部分,二者實(shí)際上通過AXI接口實(shí)現(xiàn)通信和互聯(lián)。

2023-11-09 11:28:04 3889

3889

CNN是模型還是算法的問題,實(shí)際上它兼具了兩者的特性,但更側(cè)重于作為一種模型存在。本文將從CNN的定義、結(jié)構(gòu)、原理、應(yīng)用等多個方面進(jìn)行深入探討,旨在全面解析CNN的本質(zhì)及其在計算機(jī)視覺領(lǐng)域的重要性。

2024-07-05 17:37:17 7476

7476

電子發(fā)燒友App

電子發(fā)燒友App

評論