該演示展示了Zynq-7000 All Programmable SoC及其使用NEON引擎或硬件加速來加速軟件的能力。 查看Zynq-7000 SoC的靈活性,以加速軟件和利用......

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

dsp

+關注

關注

561文章

8262瀏覽量

367797 -

賽靈思

+關注

關注

33文章

1798瀏覽量

133595 -

soc

+關注

關注

40文章

4608瀏覽量

229895

發布評論請先 登錄

相關推薦

熱點推薦

如何使用 powerquad 加速器中的一些功能以及 CMSIS 原始實現中的一些功能?

)。

如何使用 powerquad 加速器中的一些功能以及 CMSIS 原始實現中的一些功能。

Example: I do not want to call arm_mat_tran

發表于 04-03 06:37

XC7Z020-2CLG484I 雙核異構架構 全能型 SoC

Zynq-7000 系列的核心型號,創新性地將雙核 ARM Cortex-A9 處理器與 7 系列 FPGA 可編程邏輯深度集成,構建起 “軟件可編程 + 硬件可定制” 的異構計算架構,為多領域智能設備提供了一體化

發表于 02-28 23:37

從算法到部署:Enclustra如何用DSP+FPGA/SoC專長,實現功耗與成本雙優化?

DSP技術數字信號處理(DSP)是FPGA和SoC的常見應用領域。為了在此領域為客戶提供最優服務,Enclustra積累了深厚的DSP專業知識,不僅能提供純粹的

探索ADI LTC7000A:高速、多功能的高端NMOS靜態開關驅動器

探索ADI LTC7000A:高速、多功能的高端NMOS靜態開關驅動器 在電子工程師的設計世界里,尋找一款性能卓越、功能豐富的高端NMOS靜態開關驅動器并非易事。ADI的LTC7000

如何在Zynq UltraScale+ MPSoC平臺上通過JTAG啟動嵌入式Linux鏡像

在之前文章中,我們介紹了如何使用 XSCT 工具通過 JTAG 在 Zynq SoC 上啟動嵌入式 Linux 鏡像(從 JTAG 啟動 Zynq-7000 嵌入式 Linux:使用 XSCT 全

Ceva在恩智浦的軟件定義車輛處理器上實現 實時人工智能加速

恩智浦 * S32Z2 和 S32E2 實時處理器集成 Ceva**的* * AI DSP* ,為軟件定義車輛提供預測分析、能量管理和智能控制功能 隨著車輛向軟件定義平臺演進,對實時處

FPGA技術探討:ZYNQ7020核心板的歷程、技術及國產化

Xilinx(現為AMD旗下公司)是FPGA技術的奠基者和全球領導者。 它通過從FPGA到All Programmable SoC(如ZYNQ),再到ACAP(如Versal)的持續創

fpga嵌入e203內核搭建soc如何實現通信功能?

在fpga嵌入e203內核實現以太網,開發板有PHY芯片LAN8720A,怎么搭建soc,如何使用總線,實現通信功能?

發表于 11-10 06:54

RSA加速實現思路

1 關于RSA算法

RSA為非對稱加密算法(也稱為公開密鑰算法),是當前比較普遍使用的非對稱加密算法之一,常用于密鑰交換和數字簽名。RSA是一種較為高級、可基于硬件和軟件實現的加密算法,安全性能高

發表于 10-28 07:28

Zynq7100 BSP移植,MSH終端不能正確顯示是為什么?

由于新版本的RT Thread的BSP不再提供Zynq7000的支持。所以同事從RT Thread(4.0.3)中的Zynq7000移植了一份Zynq 7100的BSP。但是MSH終端和串口輸出

發表于 09-19 06:26

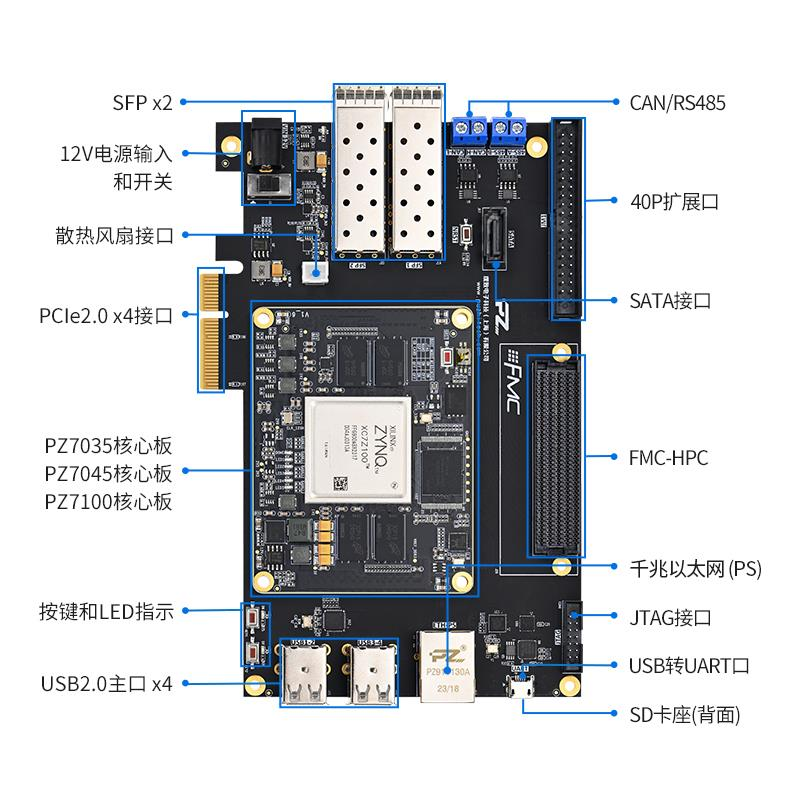

fpga開發板 璞致ZYNQ 7000 系列之 PZ7035/PZ7045/PZ7100-FH 核心板與開發板用戶手冊

本文介紹了Xilinx Zynq-7000系列可擴展處理平臺及其開發板應用。Zynq-7000采用雙核ARM Cortex-A9處理器與28nm FPGA架構,支持高性能嵌入式開發。開發板采用核心板

Zynq-7000 SoC與7系列設備內存接口解決方案數據手冊

技術手冊,適用于使用LogiCORE IP核(如DDR3/DDR2 SDRAM、RLDRAM II、QDRII+)進行存儲器接口設計26。核心功能:IP核配置與時序:詳細說明Xilinx MIG(Memory Interface Generator)IP核的使用方法,包括信號定義、時序約束、物理層(PHY

發表于 07-28 16:17

?3次下載

瑞芯微RK2118 SoC搭載Cadence Tensilica HiFi 4 DSP

Tensilica HiFi 4 DSP 的 Rockchip RK2118 系統級芯片(SoC)已于 2024 年第四季度投入量產。這款尖端的 SoC 有望利用 HiFi 4 DSP

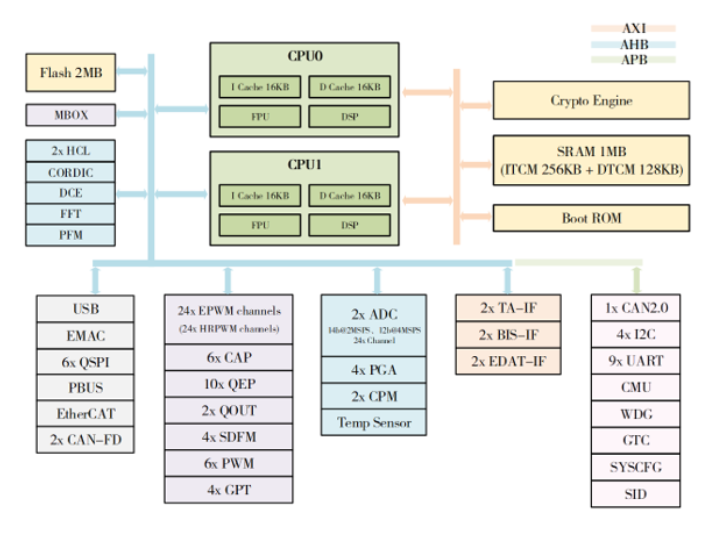

使用Zynq-7000 All Programmable SoC實現DSP功能的軟件加速

使用Zynq-7000 All Programmable SoC實現DSP功能的軟件加速

評論