在高速、高密度的PCB設計項目中,工程師的設計早已邁入了另外一個臺階——從“連通即可”的基礎要求,躍遷至以規(guī)則驅動、以仿真驗證、以工藝為導向的精密設計時代。

本文基于 Allegro X Designer 的核心功能,從規(guī)則管理、布線效率、疊層設計這三個方面入手,剖析貫穿整個設計流程的專業(yè)設計體系。

本文要點

key point

一文看懂 Allegro XDesigner系統(tǒng)級電路設計解法

約束管理器:實現(xiàn)設計的規(guī)則定義與管理,讓你的規(guī)則設計從手動檢查升級為驅動整個設計的自動化管理引擎

智能交互式布線:擁有智能感知、自動優(yōu)化能力,實現(xiàn)布線約束的高效落地。

層疊編輯器:提供疊層設計、阻抗計算與材料管理,解決信號設計中的信號完整性、電源完整性等問題。

問題點1:線寬、間距的定義憑經驗感覺至上,遵循“差不多”原則

在高速數(shù)字電路設計中,工程師常憑經驗設置線寬、間距,但當信號速率攀升至GHz級別、疊層結構復雜時,"差不多"的規(guī)則往往成為信號完整性失效的導火索。更棘手的是,不同網絡(如DDR數(shù)據組、時鐘、差分對)對規(guī)則要求差異極大,手動維護極易出錯;板子的布線常常占據整個項目周期的50%,手動推擠調整已有布線、調整過孔繁瑣且易出錯;疊層設計僅憑工程師的經驗估算可能會導致加工后的板子的阻抗與設計預期偏差較大,導致整塊板子成為廢板。

時鐘線長度超限:PCB走線的時候因板子空間有限常常布線超過一定的長度,未考慮終端匹配以及緩沖問題,導致信號傳播延遲過大,引起反射和過沖,損壞驅動端或接收端的IO電路。

信號線走線之間的線寬過窄:在一定的阻抗下,線距過窄會導致信號反射和功率損耗,長期工作會有PCB板過熱燒毀的風險。

過孔使用不當:高速信號布線時使用了常規(guī)的通孔,存在一部分的過孔殘樁導致阻抗不連續(xù),從而引起信號反射和插入損耗。

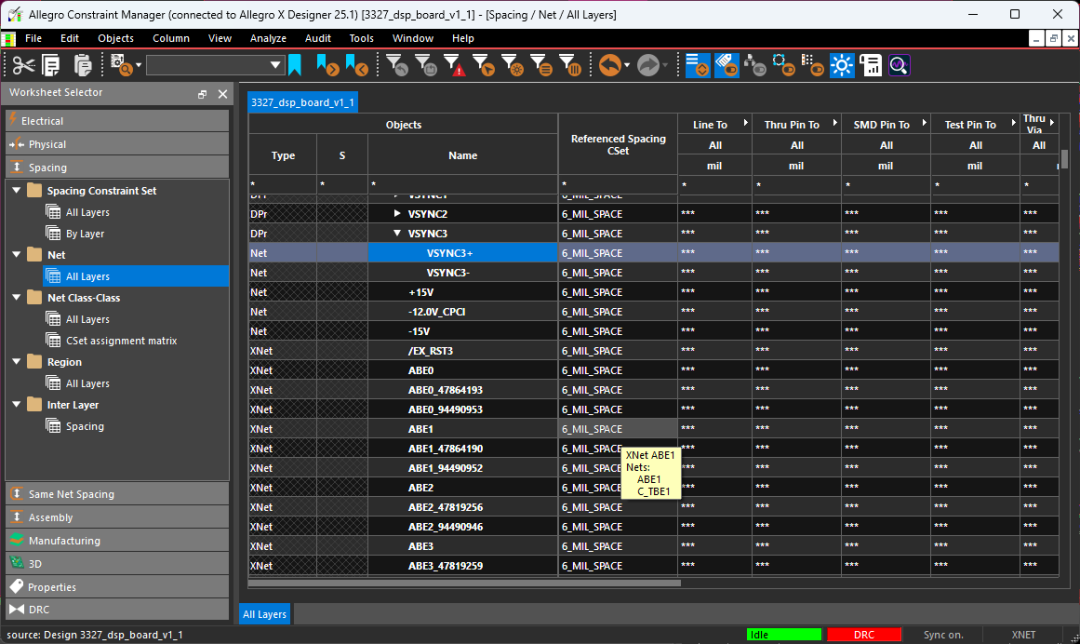

針對電氣、物理、間距這三類約束相關的問題,Allegro X Designer提供了系統(tǒng)級的預防手段——Constraint Manager(約束管理器)。

通過這一集中化的規(guī)則定義中樞,工程師可將信號完整性、制造工藝、安全規(guī)范等多維度要求轉化為層級化的規(guī)則體系,涵蓋電氣約束(線長、等長、延遲)、物理約束(線寬、間距、過孔類型)以及間距約束(不同網絡類之間的安全距離)。

同時,約束管理器與 Sigrity 信號完整性仿真引擎、PCB 制造工藝數(shù)據庫無縫對接,可自動調用基于真實板材參數(shù)和疊層結構的阻抗計算模型,并結合板廠實際工藝能力進行規(guī)則校驗,從而在設計階段就將經驗規(guī)則固化為可執(zhí)行、可復用的設計標準,徹底告別“憑感覺、差不多設規(guī)則”的被動局面。

問題點2:新增、調整布線太過隨意,布線調整效率低

傳統(tǒng)“先布后調”方式:布線時未啟用自動推擠功能,新增走線與相鄰走線之間的距離小于設計規(guī)則要求,形成串擾以及短路風險。

線間間距不均與等長失控:數(shù)據線之間的線距不均導致部分區(qū)域的串擾,差分信號未使用等長布線導致后期后期等長差異過大導致信號衰減嚴重等。

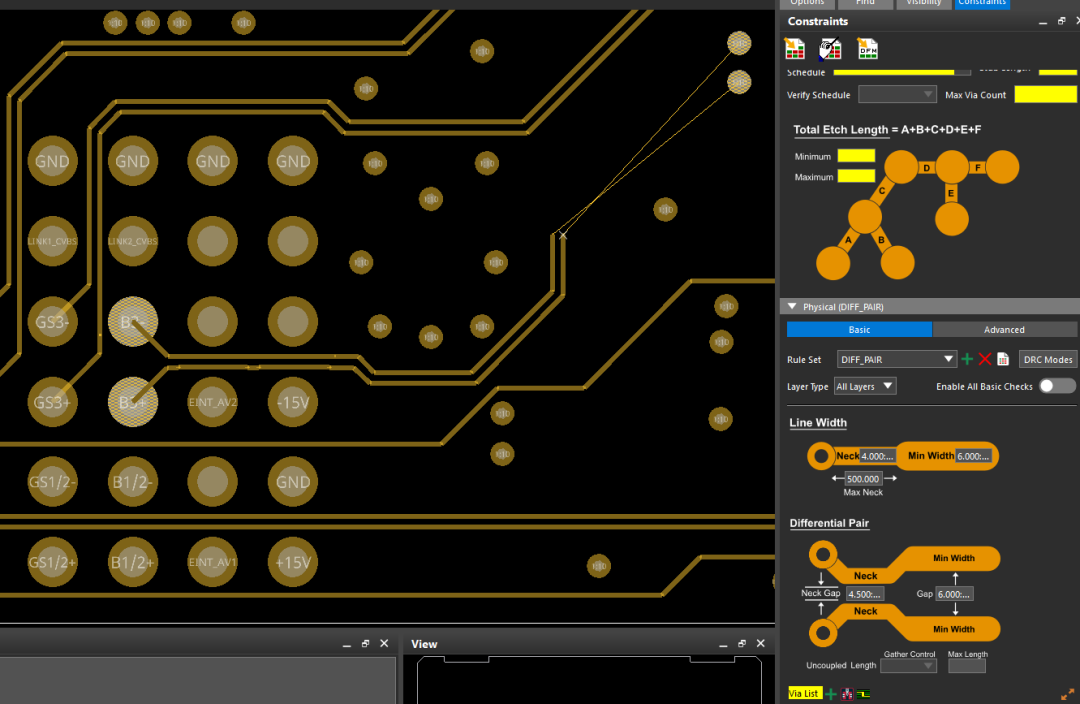

針對提高布線效率、進行間距優(yōu)化等問題,Allegro X Designer 內置一套完整的交互式布線引擎和約束驅動設計環(huán)境。半自動等長繞線功能支持多種繞線模式(波浪形、鋸齒形、階梯形),在布線過程中實時顯示剩余長度,并可一鍵生成符合公差的繞線方案;動態(tài)推擠布線(Push&Shove)則讓新增走線時自動調整周邊線段,始終保持線寬、間距與設計規(guī)則一致,徹底告別“先布后調"帶來的反復修線。自動修線優(yōu)化工具(Auto Gloss)可在布線完成后一鍵消除銳角、直角等不良拐角,并將走線圓滑處理,從而將工程師從“手工推線、目測等長、反復返工”的重復勞動中解放出來,使布線效率提升50%以上,同時確保信號完整性與設計規(guī)范的高度一致性。

問題點3:依靠經驗或簡單工具估算層疊參數(shù),引發(fā)信號反射、串擾

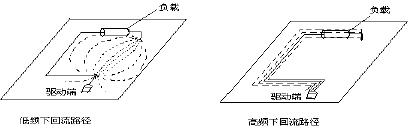

層疊不對稱導致PCB板翹曲:在設計多層板的時候,頂層和底層的銅厚分布不均會導致 PCB 在回流焊過程中受熱時,上下表面膨脹系數(shù)不一致而造成生成出來的 PCB 板子不符合國際標準。

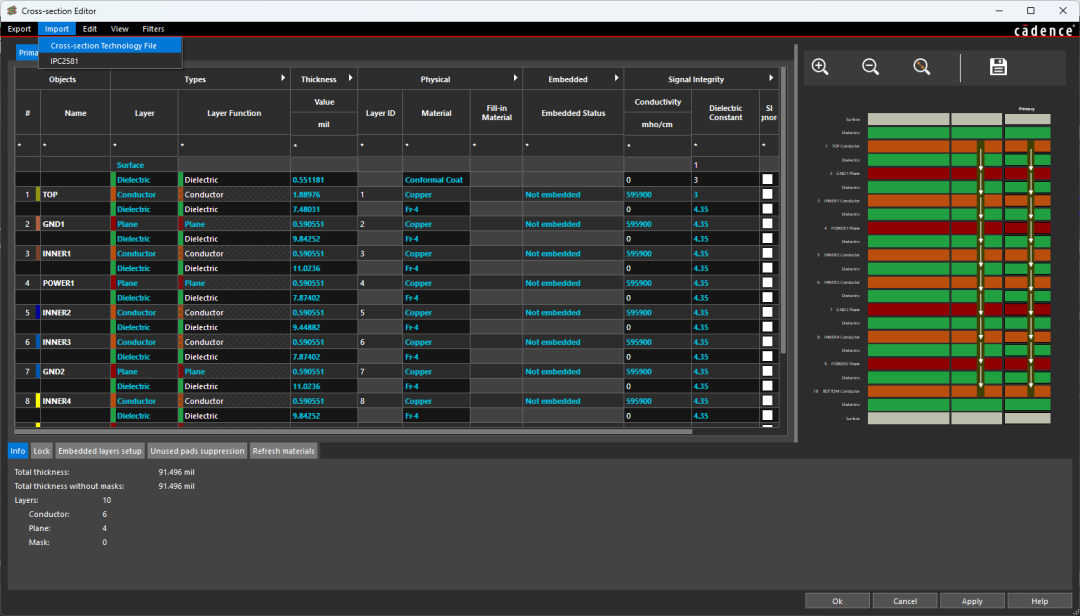

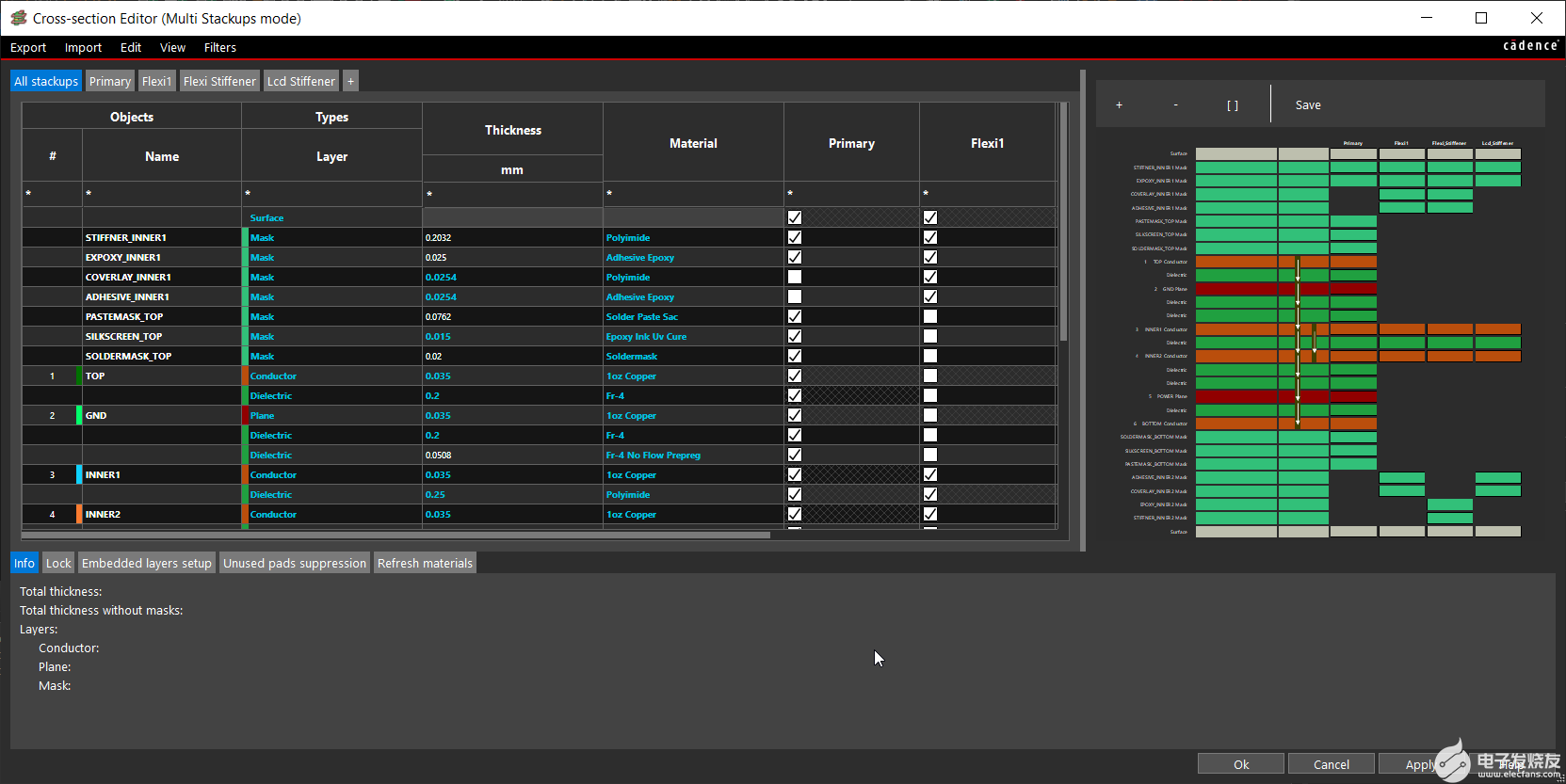

在疊層編輯界面,工程師可直接設定每層的介質厚度、銅厚、介電常數(shù)等參數(shù),系統(tǒng)實時計算微帶線、帶狀線等常見結構的特征阻抗值,并自動關聯(lián)到約束管理器的阻抗規(guī)則中;同時允許工程師預設生產廠家的加工工藝參數(shù)(如蝕刻補償、壓合厚度、銅箔粗糙度等),使阻抗計算與疊層設計更貼近實際制造能力,從源頭減少“設計-制造”偏差。此外,疊層對稱性與平衡性檢查功能可自動檢測疊層結構是否存在翹曲風險,實時提供優(yōu)化建議,確保板廠加工良率。

針對復雜的PCB設計流程,需要嚴格把控每個關鍵環(huán)節(jié),構建系統(tǒng)化的體系。Allegro X Designer 提供了一套深度融合的解決方案,助力工程師在設計源頭筑牢防線:通過Constraint Manager約束管理器建立層級化的電氣、物理、間距規(guī)則體系,將設計意圖轉化為可執(zhí)行的自動化管控;借助智能布線引擎與半自動等長繞線系統(tǒng),將推擠避讓、多線并行、等長匹配等復雜操作融入交互式布線環(huán)境,徹底告別“先布后調、手工修線”的低效模式;利用疊層編輯器(Cross Section) 內置的材料庫、工藝參數(shù)預設及對稱性檢查功能,使疊層設計與阻抗計算精準對齊制造能力,從物理基礎上保障信號完整性與可制造性。幫助每一位深耕技術領域的專家在下一次設計中更加出彩。

-

電路設計

+關注

關注

6743文章

2718瀏覽量

219816 -

PCB設計

+關注

關注

396文章

4925瀏覽量

95517 -

allegro

+關注

關注

42文章

770瀏覽量

150295

發(fā)布評論請先 登錄

Allegro PCB設計技巧 為多層剛性和柔性堆疊指定層信息

Altium Designer中PCB設計規(guī)則設置

推薦自己寫的書《Altium Designer PCB畫板速成(配視頻)》

【視頻教程】Altium designer 6層PCB設計實戰(zhàn)+配demo案例文件

原創(chuàng)|PCB設計中疊層結構的設計建議

PCB設計中,有哪些布線規(guī)則?

OrCAD技術有助縮短PCB設計

pcb設計布局布線原則及規(guī)則

Allegro X 23.11 版本更新 I PCB 設計:DFA_BOUND 用于 DFA 規(guī)則設定

技術資訊 I PCB設計三大頑疾:規(guī)則亂、布線慢、疊層偏——Allegro X Designer 的系統(tǒng)級解法

技術資訊 I PCB設計三大頑疾:規(guī)則亂、布線慢、疊層偏——Allegro X Designer 的系統(tǒng)級解法

評論