CDCVF2509:高性能PLL時鐘驅動器的深度解析

在電子設計領域,時鐘驅動器的性能對整個系統的穩定性和可靠性起著至關重要的作用。今天,我們就來深入探討一款高性能的時鐘驅動器——CDCVF2509,看看它有哪些獨特的特性和優勢。

文件下載:cdcvf2509.pdf

一、CDCVF2509概述

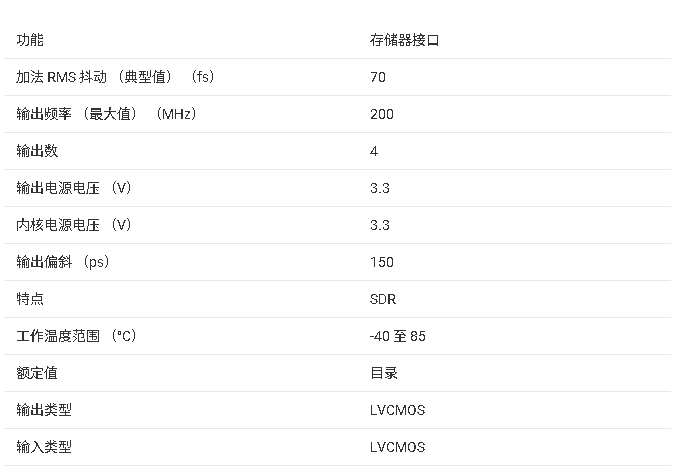

CDCVF2509是一款高性能、低偏斜、低抖動的鎖相環(PLL)時鐘驅動器,專為同步DRAM應用而設計。它采用先進的深亞微米工藝,在功耗、性能等方面都有著出色的表現。

二、關鍵特性剖析

1. 高性能指標

- 頻率范圍:其工作頻率范圍為50MHz至175MHz,能夠滿足多種不同的應用需求。在66MHz至166MHz的頻率范圍內,靜態相位誤差分布為±125ps,周期抖動典型值為70ps,為系統提供了高精度的時鐘信號。

- 低功耗:與當前的PC133設備相比,采用先進工藝使得功耗降低了40%以上,這對于追求低功耗設計的工程師來說是一個非常有吸引力的特性。

2. 靈活的輸出配置

- 輸出分配:該器件可以將一個時鐘輸入分配到一組五個輸出和一組四個輸出,總共九個低偏斜、低抖動的時鐘輸出。每個輸出組都有獨立的輸出使能控制,方便工程師根據實際需求進行靈活配置。

- 內置阻尼電阻:芯片內置25Ω的串聯阻尼電阻,無需外部RC網絡,簡化了設計,降低了成本和電路板空間。

3. 鎖相環功能

- 精確同步:通過PLL將反饋輸出(FBOUT)在頻率和相位上精確對齊到時鐘(CLK)輸入信號,確保輸出信號與輸入信號的同步性。

- 穩定時間:不過,PLL需要一定的穩定時間來實現反饋信號與參考信號的鎖相,這在設計時需要特別注意。

三、應用場景

1. DRAM應用

在DRAM系統中,CDCVF2509可以為DRAM提供精確的時鐘信號,確保數據的準確讀寫,提高系統的性能和穩定性。

2. 時鐘分配器

作為基于PLL的時鐘分配器,它可以將一個時鐘信號分配到多個負載,實現時鐘信號的有效分配。

3. 時鐘緩沖器

即使在非PLL的時鐘緩沖應用中,CDCVF2509也能發揮其低偏斜、低抖動的優勢,為系統提供高質量的時鐘信號。

四、電氣特性與參數

1. 絕對最大額定值

了解器件的絕對最大額定值是確保器件安全工作的關鍵。例如,AVCC的電源電壓范圍不能超過VCC + 0.7V,輸入電壓范圍為 -0.5V至4.6V等。在設計時,必須嚴格遵守這些參數,避免器件因過壓、過流等情況而損壞。

2. 推薦工作條件

推薦工作條件為我們提供了器件正常工作的最佳參數范圍。如VCC和AVCC的電源電壓范圍為3V至3.6V,輸入時鐘頻率范圍為50MHz至175MHz等。在實際應用中,盡量使器件工作在推薦條件下,以保證其性能的穩定性。

3. 開關特性

開關特性包括相位誤差時間、抖動、上升時間、下降時間、傳播延遲時間等參數。這些參數對于評估器件在高速信號處理中的性能至關重要。例如,在66MHz至166MHz的頻率范圍內,靜態相位誤差時間為±125ps,這表明器件在該頻率范圍內能夠保持較好的相位同步性。

五、設計注意事項

1. 穩定時間

由于PLL需要穩定時間來實現鎖相,在電路上電和施加有效CLK信號后,需要等待一段時間,直到PLL完成鎖相。在這段時間內,傳播延遲、偏斜和抖動等參數的規格可能不適用。

2. 輸入信號要求

CLK輸入信號必須具有固定的頻率和相位,否則PLL無法實現鎖相。在設計時,要確保輸入信號的穩定性。

3. 輸出負載

輸出負載的變化會影響器件的性能,特別是在考慮輸出偏斜和抖動時。在設計時,要盡量保證所有輸出的負載均衡,以確保t(sk(0))規格的有效性。

六、總結

CDCVF2509作為一款高性能的PLL時鐘驅動器,具有頻率范圍寬、低功耗、輸出配置靈活等優點,適用于多種DRAM和時鐘分配應用。在設計過程中,我們需要充分了解其特性和參數,注意穩定時間、輸入信號要求和輸出負載等問題,以確保器件能夠發揮最佳性能。希望通過本文的介紹,能幫助各位工程師更好地理解和應用CDCVF2509。大家在實際應用中遇到過哪些問題呢?歡迎在評論區留言分享。

-

高性能

+關注

關注

0文章

511瀏覽量

21415

發布評論請先 登錄

CDCVF2509:高性能PLL時鐘驅動器的深度解析

CDCVF2509:高性能PLL時鐘驅動器的深度解析

評論