TI CDCU877和CDCU877A:高性能1.8V鎖相環時鐘驅動器深度解析

在當今的電子設計領域,時鐘驅動器是確保系統穩定運行的關鍵組件之一。德州儀器(TI)的CDCU877和CDCU877A這兩款1.8V鎖相環(PLL)時鐘驅動器,專為雙倍數據速率(DDR II)應用而設計,具有諸多卓越特性。下面,我們就來詳細了解一下這兩款產品。

文件下載:cdcu877a.pdf

一、產品特性亮點

1. 廣泛兼容性

CDCU877和CDCU877A具備擴頻時鐘(SSC)兼容性,能夠有效降低電磁干擾(EMI),滿足不同系統環境的需求。對于那些對電磁兼容性有嚴格要求的應用場景,這一特性顯得尤為重要。

2. 出色的電氣性能

- 頻率范圍:其工作頻率范圍為10 MHz至400 MHz,可適應多種不同的應用需求。無論是低速系統調試,還是高速數據傳輸系統,都能穩定發揮作用。

- 低功耗:電流消耗小于135 mA,有助于降低系統的整體功耗,提高能源利用效率。在追求綠色節能的今天,低功耗特性可以延長設備的續航時間。

- 低抖動和低偏移:具有極低的周期抖動(±20 ps)、低靜態相位偏移(±50 ps)和低動態相位偏移(±15 ps)。這些特性確保了時鐘信號的準確性和穩定性,對于高速數據傳輸和高精度計時至關重要。

3. 豐富的輸出配置

該驅動器能夠將一個差分時鐘輸入分配到十個差分輸出,同時還提供一個差分反饋時鐘輸出。這種多輸出的配置方式,為系統的時鐘分布提供了極大的靈活性,可滿足不同設備對時鐘信號的需求。

二、產品詳細描述

1. 功能原理

CDCU877是一款高性能、低抖動、低偏移的零延遲緩沖器。它將差分時鐘輸入對(CK,CK)分配到十個時鐘輸出差分對(Yn,Yn)和一個反饋時鐘輸出差分對(FBOUT,FBOUT)。時鐘輸出由輸入時鐘(CK,CK)、反饋時鐘(FBIN,FBIN)、LVCMOS控制引腳(OE,OS)和模擬電源輸入(AVDD)共同控制。

2. 控制邏輯

- OE引腳:當OE為低電平時,除FBOUT/FBOUT外的時鐘輸出被禁用,但內部PLL仍會保持鎖定頻率。

- OS引腳:是一個可編程引腳,必須連接到GND或VDD。當OS為高電平時,OE的功能如上述所述;當OS和OE都為低電平時,OE對Y7/Y7無影響,Y7/Y7可以自由運行。

- AVDD引腳:當AVDD接地時,PLL關閉并旁路,可用于測試目的。

3. 低功耗模式

當兩個時鐘輸入(CK,CK)都為邏輯低電平時,設備會進入低功耗模式。此時,一個獨立于輸入緩沖器的輸入邏輯檢測電路會檢測到低電平,并使設備處于低功耗狀態,所有輸出、反饋和PLL都將關閉。當時鐘輸入從邏輯低電平轉換為差分信號時,PLL重新開啟,輸入和輸出被啟用,PLL會在規定的穩定時間內實現反饋時鐘對(FBIN,FBIN)和時鐘輸入對(CK,CK)之間的相位鎖定。

三、產品選型與訂購信息

1. 封裝形式

CDCU877和CDCU877A提供兩種封裝形式:52球μBGA(MicroStar? Junior BGA,0.65-mm間距)和40引腳MLF。不同的封裝形式適用于不同的應用場景和電路板布局要求。

2. 訂購信息

根據工作溫度范圍(-40°C至85°C),有多種不同的訂購型號可供選擇。例如,52球BGA封裝有CDCU877ZQL、CDCU877AZQL、CDCU877GQL、CDCU877AGQL等;40引腳MLF封裝有CDCU877RHA、CDCU877ARHA、CDCU877RTB、CDCU877ARTB等。具體的封裝和訂購信息可參考文檔末尾的封裝選項附錄或TI官網。

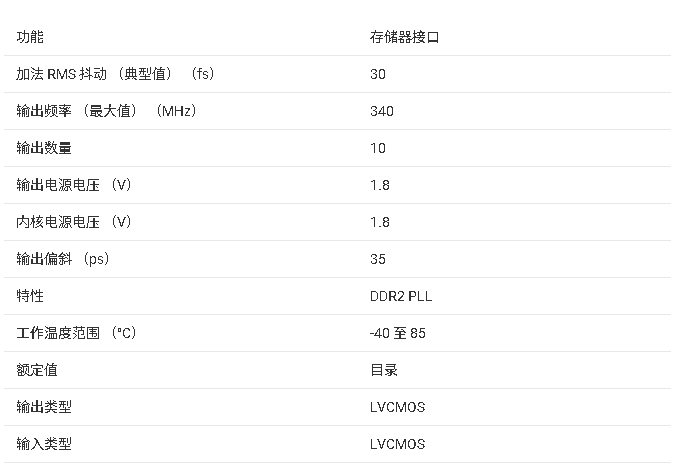

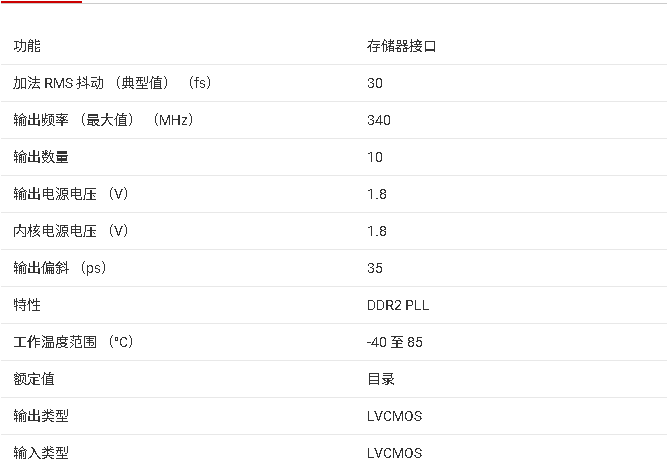

四、電氣特性與參數要求

1. 絕對最大額定值

在使用CDCU877和CDCU877A時,需要注意其絕對最大額定值。例如,電源電壓范圍(VCC)為 -0.5 V至2.5 V,輸入電壓范圍(VI)和輸出電壓范圍(VO)為 -0.5 V至VDDQ + 0.5 V等。超過這些額定值可能會對設備造成永久性損壞。

2. 推薦工作條件

為了確保設備的正常運行和最佳性能,應在推薦工作條件下使用。例如,輸出電源電壓(VDDQ)為1.7 V至1.9 V,模擬電源電壓(AVDD)為1.8 V,輸入電壓和電流等參數也有相應的范圍要求。

3. 電氣特性參數

在推薦的工作自由空氣溫度范圍內,CDCU877和CDCU877A具有一系列特定的電氣特性參數。如高電平輸出電壓(VOH)、低電平輸出電壓(VOL)、輸入電流(II)、電源電流(IDD)等。這些參數對于評估設備的性能和設計電路具有重要意義。

4. 時序要求

- 時鐘頻率:工作時鐘頻率范圍為10 MHz至400 MHz,應用時鐘頻率范圍為160 MHz至340 MHz。在不同的頻率范圍內,PLL的性能和要求也有所不同。

- 占空比:輸入時鐘的占空比要求為40%至60%。

- 穩定時間:集成PLL電路在電源上電后,需要12 μs的穩定時間來實現反饋信號與參考信號的相位鎖定。在正常工作中,當CK和CK進入低功耗模式后再返回有源操作時,也需要相同的穩定時間。

五、開關特性

1. 使能和禁用時間

OE引腳控制時鐘輸出的使能和禁用,使能時間(ten)和禁用時間(tdis)典型值均為8 ns,確保了快速的響應速度。

2. 抖動和偏移參數

- 周期抖動:在不同的頻率范圍內,周期抖動(tjit(cc+)和tjit(cc-))有不同的規格要求。例如,在160 MHz至190 MHz范圍內,周期抖動為±40 ps;在160 MHz至340 MHz范圍內,周期抖動為±30 ps。

- 相位偏移:靜態相位偏移時間(t(ω))為 -50 ps至50 ps,動態相位偏移時間(t(ω)dyn)為 -15 ps至15 ps。

- 輸出時鐘偏移:輸出時鐘偏移(tsk(o))最大為35 ps,保證了輸出時鐘信號的一致性。

3. 壓擺率和其他參數

輸入和輸出時鐘的壓擺率、輸出差分對交叉電壓、SSC調制頻率等參數也都有明確的規定,這些參數對于確保信號的質量和系統的穩定性至關重要。

六、應用建議與注意事項

1. 電源濾波

為了保證PLL的穩定運行,推薦對AVDD進行濾波處理。可以使用一個2200 pF的電容器靠近PLL放置,同時使用寬走線連接PLL的模擬電源和地。建議使用的磁珠型號為Fair-Rite PN 2506036017Y0或等效產品。

2. 靜電防護

由于這些設備內置的ESD保護有限,在存儲或處理過程中,應將引腳短接在一起或把設備放在導電泡沫中,以防止靜電對MOS柵極造成損壞。

3. 輸入時鐘要求

為了消除輸入壓擺率對靜態相位偏移的影響,建議參考時鐘輸入CK和CK以及反饋時鐘輸入FBIN和FBIN的輸入壓擺率盡量相等,推薦的目標壓擺率為2.5 V/ns。

CDCU877和CDCU877A這兩款1.8V鎖相環時鐘驅動器以其出色的性能和靈活的配置,為DDR II應用提供了可靠的時鐘解決方案。在實際設計中,工程師們需要根據具體的應用需求和系統要求,合理選擇和使用這兩款產品,同時注意各項參數和注意事項,以確保系統的穩定運行和高性能表現。大家在使用過程中遇到過哪些類似產品的挑戰呢?歡迎在評論區分享。

發布評論請先 登錄

?CDCU877/CDCU877A 1.8V鎖相環時鐘驅動器技術文檔總結

CDCU877 用于DDR2 SDRAM應用的1.8V鎖相環時鐘驅動器技術手冊

TI CDCU877和CDCU877A:高性能1.8V鎖相環時鐘驅動器深度解析

TI CDCU877和CDCU877A:高性能1.8V鎖相環時鐘驅動器深度解析

評論