Texas Instruments CDCE913-Q1與CDCEL913-Q1時鐘合成器深度剖析

作為電子工程師,在設計中選擇合適的時鐘合成器至關重要。Texas Instruments的CDCE913-Q1和CDCEL913-Q1可編程1-PLL VCXO時鐘合成器是汽車及相關應用的優質選擇。以下將詳細介紹它們的特點、應用、技術參數及設計要點。

文件下載:cdcel913-q1.pdf

一、器件特性亮點

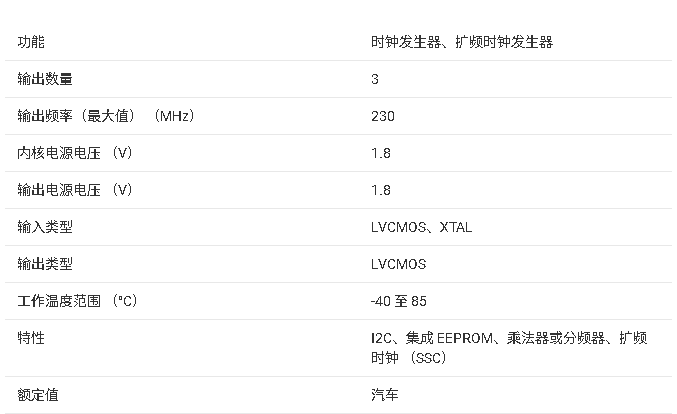

汽車應用資質

這兩款器件均符合汽車應用標準,通過AEC-Q100認證。CDCE913-Q1的工作溫度范圍為 -40°C 至 +125°C(1級),而CDCEL913-Q1為 -40°C 至 +85°C(3級)。同時,它們在ESD(靜電放電)防護方面表現出色,人體模型(HBM)分類為H2,充電設備模型(CDM)分類為C6。

功能安全與可編程性

具備功能安全能力,可提供相關文檔輔助設計。支持系統內可編程,配備串行可編程易失性寄存器和非易失性EEPROM,能存儲用戶設置,方便定制化。

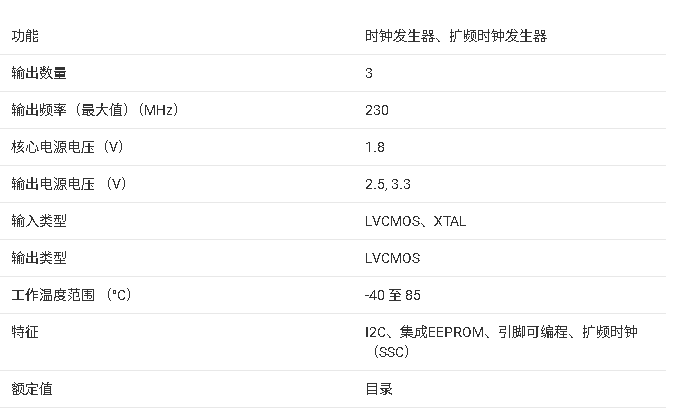

靈活的時鐘輸入輸出

支持8MHz至32MHz的外部晶體、片上VCXO(±150ppm牽引范圍)以及最高160MHz的單端LVCMOS時鐘輸入。輸出頻率可自由選擇,最高達230MHz,且具備低噪聲PLL內核和集成的PLL環路濾波器組件,實現低周期抖動(典型值50ps)。輸出電源引腳獨立,CDCE913-Q1支持3.3V和2.5V,CDCEL913-Q1為1.8V。

可編程功能與應用兼容性

擁有三個用戶可定義的控制輸入(S0、S1、S2),可用于SSC選擇、頻率切換、輸出啟用或電源關閉等。能為視頻、音頻、USB、IEEE1394、RFID、藍牙、WLAN、以太網和GPS等應用生成高精度時鐘,也適用于TI的DaVinci?、OMAP?和DSP等。此外,還支持可編程SSC調制,可實現0-PPM時鐘生成。

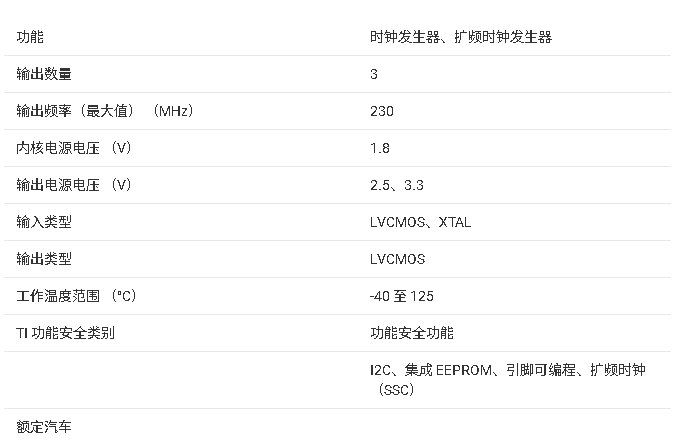

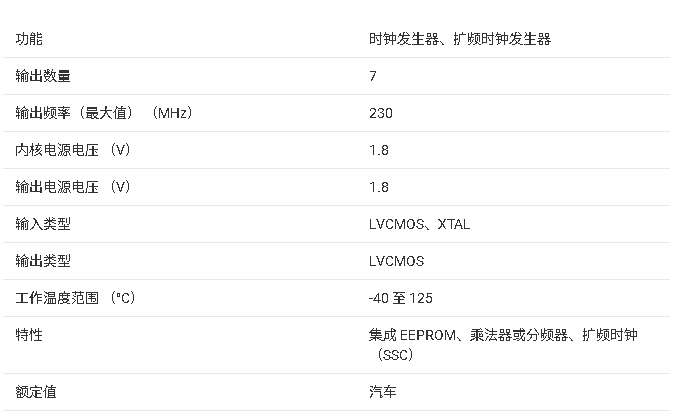

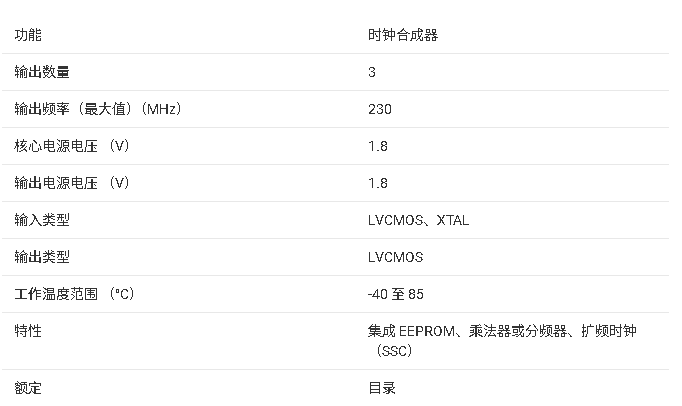

二、器件對比與封裝信息

| 與其他類似器件相比,CDCE913-Q1和CDCEL913-Q1在電源和輸出配置上有所不同。具體見下表: | 器件 | 電源(V) | PLL | 輸出 |

|---|---|---|---|---|

| CDCE913-Q1 | 2.5 至 3.3 | 1 | 3 | |

| CDCEL913-Q1 | 1.8 | 1 | 3 | |

| CDCE937-Q1 | 2.5 至 3.3 | 3 | 7 | |

| CDCEL937-Q1 | 1.8 | 3 | 7 | |

| CDCE949-Q1 | 2.5 至 3.3 | 4 | 9 | |

| CDCEL949-Q1 | 1.8 | 4 | 9 |

兩款器件均采用TSSOP封裝,CDCE913-Q1的封裝尺寸為5mm × 6.4mm。

三、技術參數詳解

絕對最大額定值

需要注意各電源引腳和輸入輸出的電壓、電流以及溫度的最大限制,超過這些值可能導致器件永久損壞。例如,VDD電源電壓在CDCEL913-Q1和CDCE913-Q1中有不同的范圍,操作時需謹慎。

ESD和推薦工作條件

ESD評級方面,HBM為±2000V,CDM為±1000V。推薦工作條件涵蓋電源電壓、輸入輸出電壓、電流、負載和環境溫度等參數,確保器件在這些條件下能正常工作并發揮最佳性能。

電氣特性

包括電源電流、VCO頻率范圍、LVCMOS輸入輸出電壓、抖動、偏斜和占空比等參數。例如,典型的電源電流在不同工作模式下有所不同,輸出抖動和偏斜會影響時鐘信號的質量。

時序要求

對于CLK_IN和I2C接口,對時鐘頻率、上升下降時間、占空比和其他時序參數都有明確要求,設計時需嚴格遵循,以保證通信的穩定性。

四、詳細設計與應用要點

功能框圖與特性描述

從功能框圖可以看出,器件由PLL、VCXO、可編程分頻器和輸出驅動器等部分組成。控制終端(S0、S1、S2)可進行多種功能配置,如SSC選擇、頻率切換和輸出狀態控制。同時,S1/SDA和S2/SCL為雙功能引腳,可在默認的I2C編程接口和控制引腳之間切換。

編程與數據協議

支持Byte Write、Byte Read、Block Write和Block Read操作,通過I2C接口進行編程。編程時需注意EEPROM的寫入操作,要在CLKIN拉低的情況下進行,并通過EEPIP監控編程狀態。

典型應用與設計流程

在信息娛樂系統等應用中,可根據具體需求設計時鐘頻率。例如,在滿足EMI要求的前提下,可通過配置SSC參數來降低電磁干擾。設計時需進行PLL頻率規劃,根據輸入頻率和輸出頻率要求計算PLL的乘數和除數。同時,要考慮晶體振蕩器的啟動時間和頻率調整,以及未使用的輸入輸出處理和XO與VCXO模式的切換。

電源與布局建議

電源方面,要注意外部參考時鐘和電源的上電順序,避免輸出不穩定。布局時,晶體應盡量靠近器件,確保布線長度一致,避免在晶體及其布線區域下方布線,以減少寄生參數和噪聲耦合。同時,合理放置旁路電容,降低線路電感影響。

五、總結與思考

Texas Instruments的CDCE913-Q1和CDCEL913-Q1時鐘合成器憑借其豐富的功能、靈活的配置和良好的性能,在汽車及相關應用中具有很大的優勢。但在實際設計中,工程師仍需根據具體應用需求,仔細考慮各項參數和設計要點,如電源管理、布局布線和編程配置等。大家在使用這兩款器件時,是否遇到過一些特殊的問題或挑戰呢?歡迎在評論區分享交流。

-

時鐘合成器

+關注

關注

0文章

113瀏覽量

8891

發布評論請先 登錄

CDCE949-Q1可編程4-PLL VCXO時鐘合成器數據表

CDCE913-Q1和CDCEL913-Q1可編程1-PLL VCXO時鐘合成器數據表

?CDCE913-Q1和CDCEL913-Q1可編程時鐘合成器技術文檔總結

?CDCE937-Q1/CDCEL937-Q1 可編程時鐘合成器技術文檔總結

CDCEL913-Q1 汽車目錄可編程 1-PLL VCXO 時鐘合成器技術手冊

CDCEL913 具有 1.8V LVCMOS 輸出的可編程 1-PLL VCXO 時鐘合成器技術手冊

CDCE913 可編程1PLL VCXO時鐘合成器技術手冊

Texas Instruments CDCE913-Q1與CDCEL913-Q1時鐘合成器深度剖析

Texas Instruments CDCE913-Q1與CDCEL913-Q1時鐘合成器深度剖析

評論