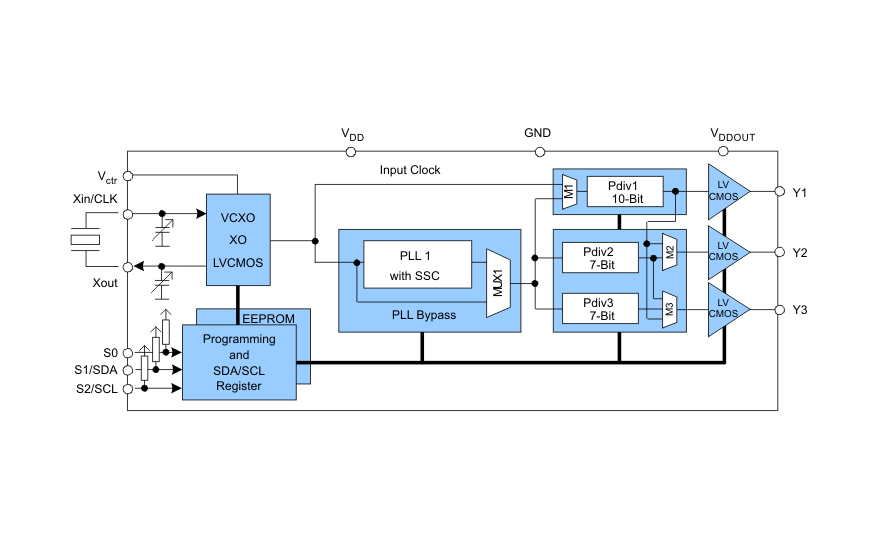

CDCE913和CDCEL913器件是基于PLL的模塊化、低成本、高性能、可編程時鐘合成器。這些器件從單個輸入頻率產生多達三個輸出時鐘。每個輸出都可以使用集成的可配置PLL在系統內針對高達230MHz的任何時鐘頻率進行編程。

CDCx913 具有獨立的輸出電源引腳 VDDOUT,用于 CDCEL913 為 1.8V,用于 CDCE913為 2.5V 至 3.3V。

*附件:cdcel913.pdf

輸入接受外部晶體或LVCMOS時鐘信號。可選的片內VCXO允許將輸出頻率與外部控制信號同步。

PLL 支持 SSC(擴頻時鐘),以獲得更好的電磁干擾 (EMI) 性能。

該器件支持非易失性 EEPROM 編程,可根據應用輕松定制器件。所有器件設置都可通過SDA/SCL總線(2線串行接口)進行編程。

CDCx913 在 1.8V 環境中工作,工作溫度范圍為 –40°C 至 85°C。

特性

- 可編程時鐘發生器系列成員

- CDCE913/CDCEL913:1-PLL,3 個輸出

- CDCE925/CDCEL925:2-PLL,5 個輸出

- CDCE937/CDCEL937:3-PLL,7 個輸出

- CDCE949/CDCEL949:4-PLL,9 路輸出

- 系統內可編程性和EEPROM

- 串行可編程易失性寄存器

- 用于存儲客戶設置的非易失性EEPROM

- 靈活的輸入時鐘概念

- 外部晶體:8MHz至32MHz

- 片上VCXO:拉動范圍±150ppm

- 單端LVCMOS,最高可達160MHz

- 自由選擇輸出頻率,最高可達 230 MHz

- 低噪聲PLL內核

- 集成 PLL 回路濾波器組件

- 低周期抖動(典型值 50ps)

- 獨立的輸出電源引腳

- CDCE913:3.3V 和 2.5V

- CDCEL913:1.8V

- 靈活的時鐘驅動器:

- 1.8V器件電源

- 寬溫度范圍:–40°C 至 85°C

- 采用 TSSOP 封裝

- 用于輕松進行 PLL 設計和編程的開發和編程套件 (TI Pro-Clock?)

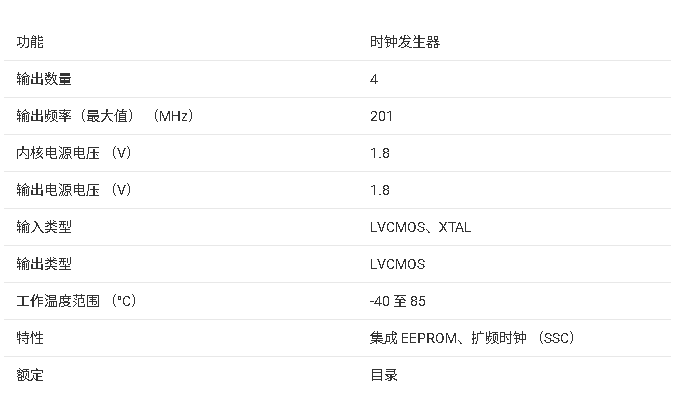

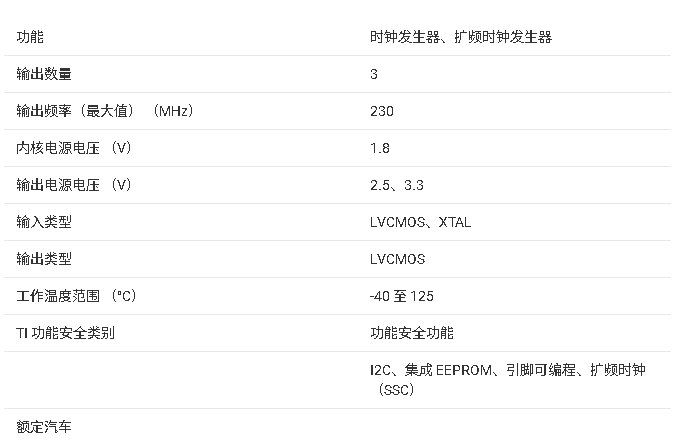

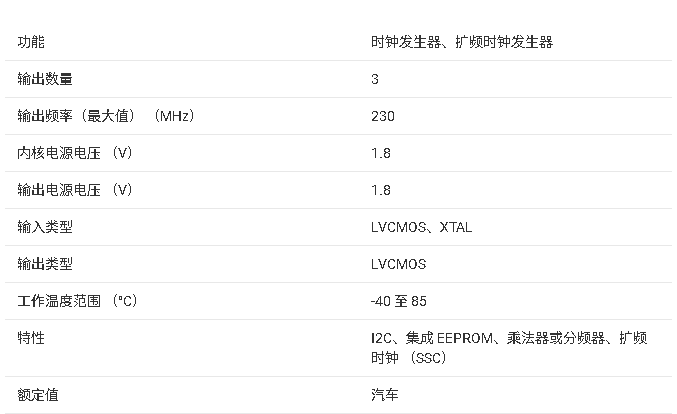

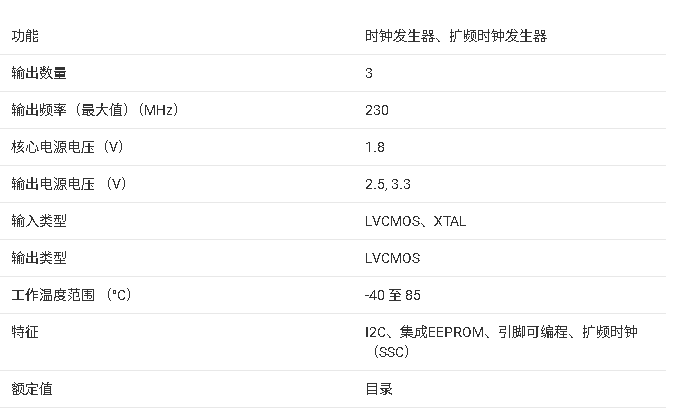

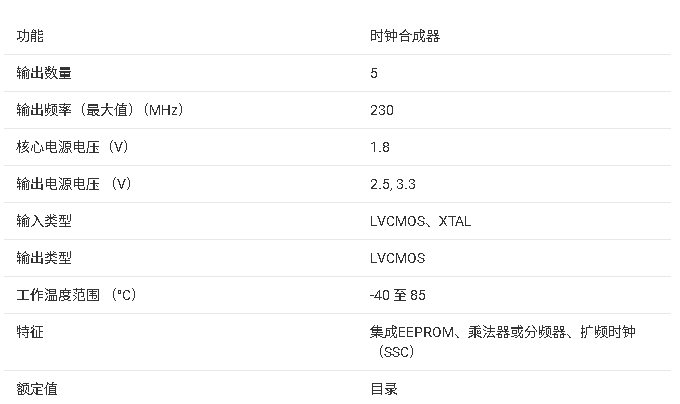

參數

方框圖

?1. 產品概述?

- ?型號系列?:CDCE913(3.3V/2.5V輸出)與CDCEL913(1.8V輸出),屬于可編程時鐘發生器家族,支持擴頻時鐘(SSC)以降低EMI。

- ?核心特性?:

- 單PLL設計,支持3路獨立輸出,頻率范圍最高至230MHz。

- 集成非易失性EEPROM,支持用戶配置存儲及系統內編程(通過I2C接口)。

- 支持外部晶體(8MHz–32MHz)或LVCMOS時鐘輸入,內置VCXO(壓控晶體振蕩器)實現頻率同步。

- 低周期抖動(典型值50ps),適用于視頻、音頻、USB、以太網等應用。

?2. 關鍵功能?

- ? 擴頻時鐘(SSC) ?:支持中心擴展(±0.25%至±2.0%)和下擴展(-0.25%至-2.0%),優化EMI性能。

- ?靈活控制?:3個可編程引腳(S0/S1/S2)支持頻率切換、輸出使能、SSC模式選擇等功能。

- ?多電壓輸出?:獨立供電引腳(VDDOUT)支持1.8V、2.5V或3.3V LVCMOS輸出電平。

?3. 應用場景?

- ?典型應用?:數字電視(D-TV)、機頂盒(STB)、DVD播放器/錄像機、打印機、網絡設備(WiFi、藍牙、以太網PHY)。

- ?參考設計?:提供音頻/視頻時鐘生成方案,例如從27MHz輸入衍生多路輸出時鐘。

?4. 技術參數?

- ?電氣特性?:

- 工作電壓:1.7V–1.9V(VDD),輸出電源1.8V–3.6V(VDDOUT)。

- 溫度范圍:-40°C至85°C。

- 輸出驅動能力:支持±8mA至±12mA(視電壓模式)。

- ?時序性能?:

- 傳播延遲:典型值3.2ns(3.3V模式)。

- 周期抖動:70ps(峰峰值,典型值)。

?5. 封裝與開發支持?

- ?封裝?:14引腳TSSOP(5mm×6.4mm)。

- ?開發工具?:TI Pro-Clock?軟件簡化PLL配置與編程。

?6. 設計注意事項?

- ?布局建議?:晶體需靠近器件,對稱布線以減少寄生效應;電源引腳需就近放置去耦電容。

- ?未使用引腳處理?:VCtrl懸空,其他未用輸入接地,輸出可浮空或禁用。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

可編程

+關注

關注

2文章

1330瀏覽量

41537 -

pll

+關注

關注

6文章

985瀏覽量

138315 -

時鐘合成器

+關注

關注

0文章

115瀏覽量

8906 -

輸出電源

+關注

關注

0文章

51瀏覽量

8846

發布評論請先 登錄

相關推薦

熱點推薦

CDCE913-Q1和CDCEL913-Q1可編程1-PLL VCXO時鐘合成器數據表

電子發燒友網站提供《CDCE913-Q1和CDCEL913-Q1可編程1-PLL VCXO時鐘

發表于 08-23 10:55

?0次下載

CDCEL949 具有1.8V LVCMOS輸出的可編程4-PLL VCXO時鐘合成器技術手冊

CDCE949和CDCEL949是基于模塊化PLL的低成本、高性能、可編程時鐘合成器、乘法器和分頻器。這些器件從單個輸入頻率生成多達九個

CDCE937 可編程 3-PLL VCXO 時鐘合成器技術手冊

CDCE937和CDCEL937器件是基于模塊化PLL的低成本、高性能、可編程時鐘合成器、乘法器和分頻器。這些器件從單個輸入頻率生成多達 7

CDCEL824可編程2 - PLL時鐘合成器:設計與應用指南

時鐘合成器,看看它如何在各種應用場景中發揮其獨特的優勢。 文件下載: cdcel824.pdf 一、CDCEL824概述 CDCEL824是

Texas Instruments CDCE913-Q1和CDCEL913-Q1時鐘合成器:特性、應用與設計要點

的時鐘信號。今天我們要深入探討Texas Instruments公司的CDCE913-Q1和CDCEL913-Q1可編程1-PLL

CDCE937-Q1 和 CDCEL937-Q1:可編程 3-PLL VCXO 時鐘合成器的技術解析

CDCE937-Q1 和 CDCEL937-Q1:可編程 3-PLL VCXO 時鐘

深入解析 CDCE949-Q1:可編程 4-PLL VCXO 時鐘合成器

深入解析 CDCE949-Q1:可編程 4-PLL VCXO 時鐘合成器 在電子設計領域,

Texas Instruments CDCE913-Q1與CDCEL913-Q1時鐘合成器深度剖析

的CDCE913-Q1和CDCEL913-Q1可編程1-PLL VCXO時鐘

探索 CDCE913/CDCEL913:靈活低功耗 LVCMOS 時鐘發生器

CDCE913 和 CDCEL913 屬于可編程時鐘發生器家族,這一系列還有不同的成員,如 CDCE925/CDCEL925(2 -

CDCEL913 具有 1.8V LVCMOS 輸出的可編程 1-PLL VCXO 時鐘合成器技術手冊

CDCEL913 具有 1.8V LVCMOS 輸出的可編程 1-PLL VCXO 時鐘合成器技術手冊

評論