Texas Instruments CDCE913-Q1和CDCEL913-Q1時(shí)鐘合成器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn)

在電子設(shè)計(jì)領(lǐng)域,時(shí)鐘合成器扮演著至關(guān)重要的角色,它能夠?yàn)楦鞣N電子設(shè)備提供精確穩(wěn)定的時(shí)鐘信號。今天我們要深入探討Texas Instruments公司的CDCE913-Q1和CDCEL913-Q1可編程1-PLL VCXO時(shí)鐘合成器,看看它們有哪些獨(dú)特的特性、適用于哪些應(yīng)用場景以及在設(shè)計(jì)中需要注意哪些要點(diǎn)。

文件下載:cdce913-q1.pdf

芯片特性剖析

1. 汽車應(yīng)用資質(zhì)

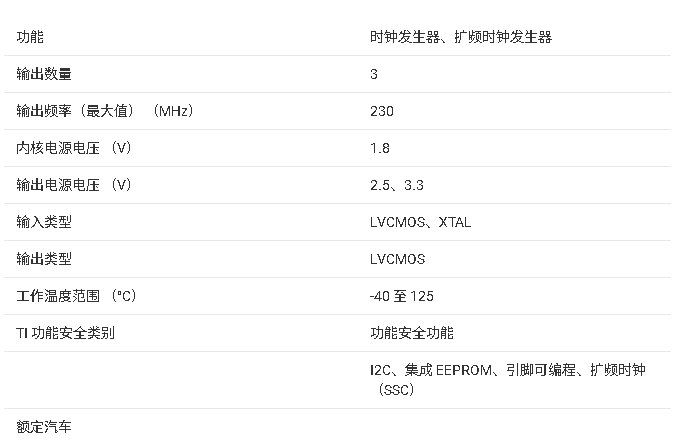

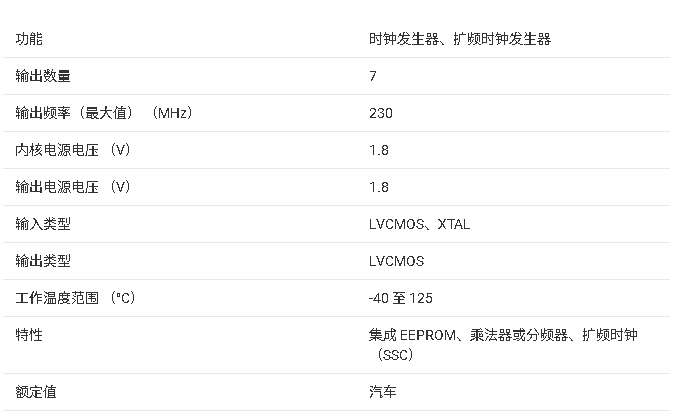

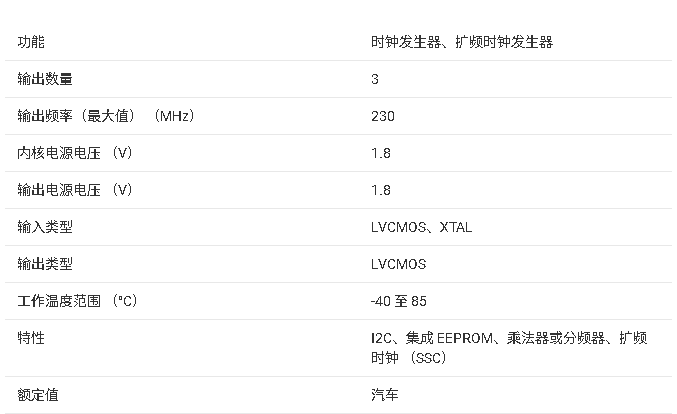

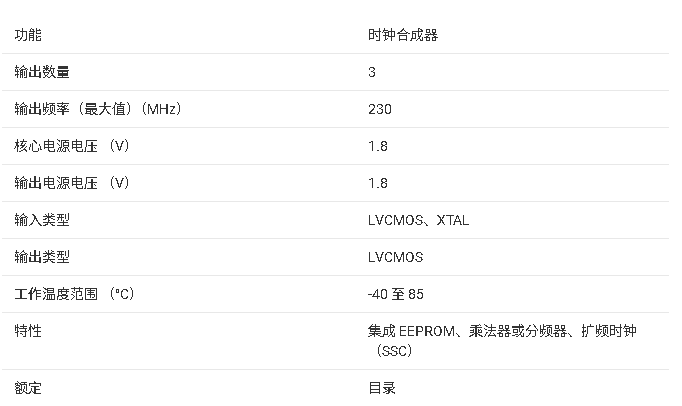

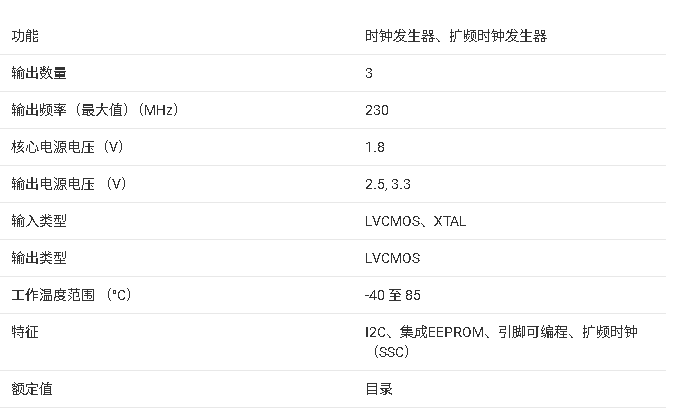

這兩款器件均符合汽車應(yīng)用標(biāo)準(zhǔn),通過了AEC-Q100認(rèn)證。CDCE913-Q1的工作溫度范圍為 -40°C 至 +125°C(1級),CDCEL913-Q1為 -40°C 至 +85°C(3級)。此外,它們還具有 H2 級別的人體模型(HBM)靜電放電(ESD)分類和 C6 級別的充電器件模型(CDM)ESD 分類,這使得它們在汽車復(fù)雜的電磁環(huán)境中能夠穩(wěn)定可靠地工作。這里不禁要問,這樣的溫度范圍和 ESD 防護(hù)能力,能滿足你所設(shè)計(jì)的汽車電子系統(tǒng)的需求嗎?

2. 功能安全能力

提供了有助于功能安全系統(tǒng)設(shè)計(jì)的文檔,這對于對安全性要求極高的汽車應(yīng)用來說是非常重要的。它可以幫助工程師更好地進(jìn)行系統(tǒng)設(shè)計(jì),確保整個(gè)系統(tǒng)的安全性和可靠性。

3. 系統(tǒng)可編程性和EEPROM

具備串行可編程易失性寄存器和非易失性 EEPROM 來存儲(chǔ)客戶設(shè)置。這意味著工程師可以根據(jù)實(shí)際需求對芯片進(jìn)行靈活編程,并且即使在掉電后也能保留設(shè)置,方便后續(xù)使用。那么在實(shí)際應(yīng)用中,你會(huì)如何利用這個(gè)特性來優(yōu)化你的設(shè)計(jì)呢?

4. 靈活的輸入時(shí)鐘理念

支持多種輸入時(shí)鐘方式,包括 8MHz 至 32MHz 的外部晶體、拉范圍為 ±150ppm 的片上 VCXO 以及最高 160MHz 的單端 LVCMOS 輸入。這種靈活性使得芯片能夠適應(yīng)不同的應(yīng)用場景和輸入要求。

5. 自由可選輸出頻率

輸出頻率最高可達(dá) 230MHz,并且可以自由選擇,能夠滿足多種不同頻率的時(shí)鐘需求。這在一些對時(shí)鐘頻率要求較為特殊的應(yīng)用中,比如高速數(shù)據(jù)傳輸、高頻通信等領(lǐng)域,具有很大的優(yōu)勢。

6. 低噪聲PLL核心

PLL 環(huán)路濾波器組件集成在芯片內(nèi)部,具有較低的周期抖動(dòng)(典型值為 50ps)。低噪聲的 PLL 核心可以保證輸出時(shí)鐘信號的穩(wěn)定性和精確性,減少對其他電路的干擾。

7. 獨(dú)立輸出電源引腳

CDCE913-Q1 提供 3.3V 和 2.5V 的輸出電源,CDCEL913-Q1 提供 1.8V 的輸出電源。獨(dú)立的輸出電源引腳可以根據(jù)不同的負(fù)載需求提供合適的電源,提高系統(tǒng)的穩(wěn)定性和兼容性。

8. 靈活的時(shí)鐘驅(qū)動(dòng)器

具有三個(gè)用戶可定義的控制輸入 [S0, S1, S2],可用于擴(kuò)頻時(shí)鐘選擇、頻率切換、輸出使能或電源關(guān)閉等功能。這種靈活性讓工程師可以根據(jù)實(shí)際需求對芯片的功能進(jìn)行自定義配置,大大增強(qiáng)了芯片的適用性。

應(yīng)用場景分析

這兩款時(shí)鐘合成器適用于多種汽車和其他電子設(shè)備應(yīng)用場景,具體如下:

1. 汽車領(lǐng)域

- 儀表盤:為儀表盤上的各種顯示和控制模塊提供精確的時(shí)鐘信號,確保數(shù)據(jù)的準(zhǔn)確顯示和處理。

- 主機(jī):在汽車信息娛樂系統(tǒng)的主機(jī)中,提供穩(wěn)定的時(shí)鐘信號,保證音頻、視頻的正常播放以及系統(tǒng)的流暢運(yùn)行。

- 導(dǎo)航系統(tǒng):為導(dǎo)航系統(tǒng)提供精確的時(shí)鐘,確保定位和導(dǎo)航的準(zhǔn)確性。

- 高級駕駛輔助系統(tǒng)(ADAS):在 ADAS 中,各種傳感器和處理器需要精確的時(shí)鐘同步,以確保系統(tǒng)的實(shí)時(shí)性和可靠性。

2. 其他領(lǐng)域

還可以為視頻、音頻、USB、IEEE1394、RFID、藍(lán)牙、WLAN、以太網(wǎng)和 GPS 等設(shè)備生成高精度時(shí)鐘,以及為 TI- DaVinci?、OMAP?、DSP 等器件提供常用的時(shí)鐘頻率。

設(shè)計(jì)要點(diǎn)提示

1. 電源供應(yīng)

在使用外部參考時(shí)鐘時(shí),必須在 (V{DD}) 上升之前驅(qū)動(dòng) XIN/CLK,以避免輸出不穩(wěn)定的風(fēng)險(xiǎn)。如果 (V{DDOUT}) 在 (V{DD}) 之前施加,建議將 (V{DD}) 拉至 GND,直到 (V_{DDOUT}) 上升。此外,芯片的電源上電控制連接到 1.8V 電源,在 1.8V 電源達(dá)到足夠電壓水平之前,整個(gè)設(shè)備將保持禁用狀態(tài)。這些電源供應(yīng)的注意事項(xiàng),你在設(shè)計(jì)時(shí)可一定要牢記哦!

2. 布局設(shè)計(jì)

當(dāng) CDCE913-Q1 用作晶體緩沖器時(shí),晶體兩端的任何寄生效應(yīng)都會(huì)影響 VCXO 的拉范圍。因此,應(yīng)將晶體單元放置在電路板上,并且盡可能靠近芯片,確保從晶體端子到 Xin 和 Xout 的走線長度相同。同時(shí),在晶體和到芯片的走線區(qū)域下方,應(yīng)盡量避免布置其他信號線,以免產(chǎn)生噪聲耦合。另外,可能需要額外的離散電容器來滿足某些晶體的負(fù)載電容要求,應(yīng)將這些小電容器盡可能靠近芯片放置,并相對于 Xin 和 Xout 對稱。

3. 編程與配置

芯片的時(shí)鐘輸入、控制引腳、PLL 和輸出級均可由用戶配置。所有設(shè)置可以通過 I2C 總線手動(dòng)寫入設(shè)備,也可以使用 TI Pro-Clock? 軟件進(jìn)行編程。該軟件可以幫助用戶快速進(jìn)行所有設(shè)置,并自動(dòng)計(jì)算優(yōu)化性能和最低抖動(dòng)所需的值。在編程過程中,需要注意 EEPROM 編程的相關(guān)時(shí)序和要求,例如在啟動(dòng) EEPROM 寫入周期之前,需要將 CLKIN 拉低,并在整個(gè)編程過程中保持低電平。

總結(jié)

Texas Instruments 的 CDCE913-Q1 和 CDCEL913-Q1 可編程1-PLL VCXO時(shí)鐘合成器具有豐富的特性、廣泛的應(yīng)用場景和一些需要注意的設(shè)計(jì)要點(diǎn)。作為電子工程師,我們可以充分利用它們的優(yōu)勢,設(shè)計(jì)出更加穩(wěn)定、可靠、高性能的電子系統(tǒng)。在實(shí)際應(yīng)用中,一定要仔細(xì)閱讀數(shù)據(jù)手冊,結(jié)合具體的設(shè)計(jì)要求,合理運(yùn)用這些芯片的功能。那么,你在設(shè)計(jì)中是否會(huì)考慮使用這兩款時(shí)鐘合成器呢?歡迎在評論區(qū)分享你的想法和經(jīng)驗(yàn)。

-

時(shí)鐘合成器

+關(guān)注

關(guān)注

0文章

113瀏覽量

8892 -

汽車應(yīng)用

+關(guān)注

關(guān)注

0文章

284瀏覽量

17458

發(fā)布評論請先 登錄

CDCE913-Q1是否同CDCE813-Q1一樣具有抖動(dòng)消除能力?

CDCE949-Q1可編程4-PLL VCXO時(shí)鐘合成器數(shù)據(jù)表

CDCE913-Q1和CDCEL913-Q1可編程1-PLL VCXO時(shí)鐘合成器數(shù)據(jù)表

?CDCE913-Q1和CDCEL913-Q1可編程時(shí)鐘合成器技術(shù)文檔總結(jié)

?CDCE937-Q1/CDCEL937-Q1 可編程時(shí)鐘合成器技術(shù)文檔總結(jié)

CDCEL913-Q1 汽車目錄可編程 1-PLL VCXO 時(shí)鐘合成器技術(shù)手冊

CDCEL913 具有 1.8V LVCMOS 輸出的可編程 1-PLL VCXO 時(shí)鐘合成器技術(shù)手冊

CDCE913 可編程1PLL VCXO時(shí)鐘合成器技術(shù)手冊

Texas Instruments CDCE913-Q1和CDCEL913-Q1時(shí)鐘合成器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn)

Texas Instruments CDCE913-Q1和CDCEL913-Q1時(shí)鐘合成器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn)

評論