Multi-Die設計將多個異構(gòu)或同構(gòu)裸片無縫集成在同一封裝中,大幅提升了芯片的性能和能效,因而在高性能計算(HPC)、人工智能(AI)、數(shù)據(jù)分析、先進圖形處理和其他要求嚴苛的應用領域中至關重要。

Multi-Die設計雖然代表了一項突破性的飛躍,但也帶來了諸多工程開發(fā)方面的挑戰(zhàn)。在2025年芯粒峰會上,來自Ansys、英特爾、新思科技和臺積公司的行業(yè)專家匯聚一堂,圍繞日益復雜的技術(shù)挑戰(zhàn)展開深入探討,并分享了寶貴的見解與建議。

應對多物理場挑戰(zhàn)

Multi-Die設計帶來的變革性優(yōu)勢毋庸置疑,但隨之而來的挑戰(zhàn)同樣令人生畏。與會專家指出,如何有效管理影響功耗和熱完整性的多物理場相互作用,是其中尤為棘手的難題。

Ansys電子、半導體與光學事業(yè)部的研究員兼首席技術(shù)專家Norman Chang表示:“電氣、機械、流體和熱之間的相互作用非常復雜。”

面對這些相互關聯(lián)的領域,設計團隊必須理解和分析其中涉及的所有相互作用和影響。Chang強調(diào):“必須綜合考慮所有因素。”

英特爾架構(gòu)、設計與技術(shù)解決方案及技術(shù)開發(fā)副總裁Lalitha Immaneni也表示,日益增長的處理需求使Multi-Die設計中的功耗和熱管理進一步復雜化。

她談到:“以AI領域為例,帶寬持續(xù)提升,容量面臨瓶頸,功耗也在不斷上升。未來五到十年內(nèi),設計的功耗可能高達五千瓦。我們該如何應對這樣的局面?”

縮放和優(yōu)化問題

隨著Multi-Die設計日益復雜,各個維度上的微縮/擴展和優(yōu)化已成為關鍵考量。工程師必須致力于器件微型化(微縮)、增強性能和容量(縱向擴展),并拓展多器件或系統(tǒng)間的連接與集成(橫向擴展)。

每個維度都伴隨著特有的挑戰(zhàn),包括功耗控制、散熱、信號完整性和整體系統(tǒng)可靠性的保障。

Immaneni表示,英特爾正在推進系統(tǒng)技術(shù)協(xié)同優(yōu)化(STCO),即同步優(yōu)化系統(tǒng)架構(gòu)、技術(shù)節(jié)點和設計方法,以期在半導體制造過程中實現(xiàn)性能、功耗和成本效益的全面改善。

她強調(diào):“如果忽視協(xié)同優(yōu)化,一旦執(zhí)行過程中出現(xiàn)問題,就要付出代價,損失將無法彌補。”

新思科技產(chǎn)品線管理執(zhí)行總監(jiān)Shekhar Kapoor補充說:“這是一個多尺度問題。我們需要同時進行微縮、縱向擴展和橫向擴展,必須在所有這些不同尺度上進行優(yōu)化,而每個尺度在性能、時序、電氣、散熱甚至成本方面都有不同的KPI。”

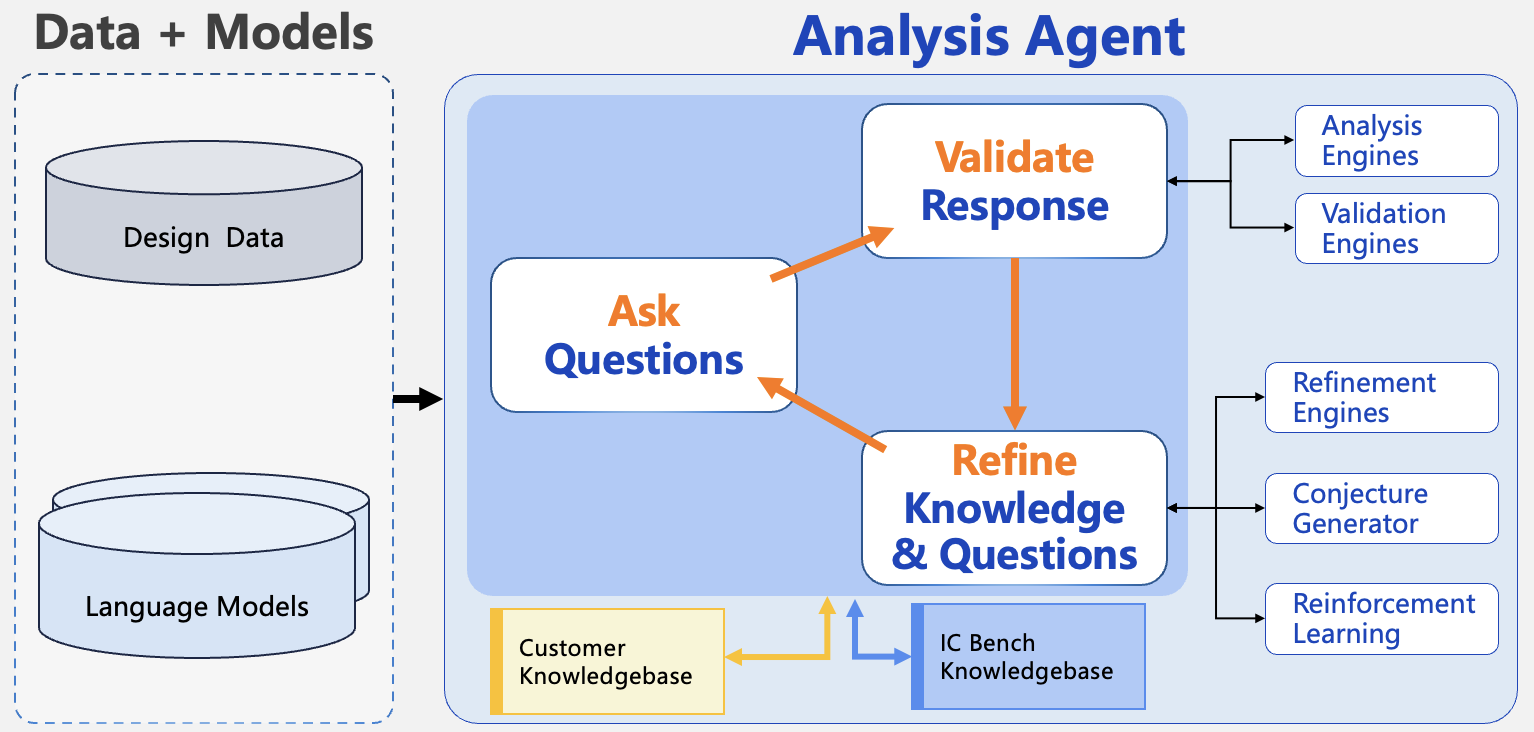

AI賦能Multi-Die設計

與會專家表示,電子設計自動化(EDA)工具和方法學的進步,為應對Multi-Die挑戰(zhàn)提供了有力支持。特別是AI驅(qū)動的工具,正被用來優(yōu)化性能、功耗和成本。

在談到AI輔助設計優(yōu)化時,Kapoor表示:“它可以解決布局、布線、架構(gòu)搭建等問題,還能探索龐大的多目標解空間,顯著加快設計進程。”

臺積公司的IP和3DFabric高級總監(jiān)Lluis Paris也表示:“AI正助力我們更快找出哪些材料組合可以實現(xiàn)更好的性能表現(xiàn)。我們還利用AI處理大量復雜的DRC(設計規(guī)則檢查),判斷它們是否完整。”

推動Multi-Die封裝技術(shù)發(fā)展和行業(yè)標準制定

與會專家一致認為,Multi-Die封裝是當前面臨的重大挑戰(zhàn)之一,還有多個障礙需要攻克。

Paris強調(diào):“我們需要共同努力,解決混合鍵合和3D封裝方法問題。相關技術(shù)指日可待。”

Immaneni補充道:“在開發(fā)一些復雜的3DIC解耦技術(shù)時,我認為材料方面需要大量創(chuàng)新。例如,分層問題、熱管理問題、高速I/O的可靠性問題,都是亟需解決的技術(shù)挑戰(zhàn)。只有大力推動材料創(chuàng)新,才能真正解決這些技術(shù)難題。”

與會專家還指出了行業(yè)標準的重要性,但也坦言在實際推進中面臨不小的阻力。

Immaneni表示:“我們面臨的最大挑戰(zhàn)之一是UCIe的各種變體,也就是外部內(nèi)存問題。它們必須針對現(xiàn)有封裝技術(shù)進行認證。”

Paris認為:“我完全認可UCIe標準本身的價值。但遺憾的是,市場上的實際情況并不理想。”他指出,客戶青睞UCIe PHY的高能效表現(xiàn),但往往忽視了對標準協(xié)議的采用。

整合研究方向與專業(yè)技能

與會專家認為,為了應對復雜的Multi-Die設計挑戰(zhàn)并加速創(chuàng)新,必須依靠全行業(yè)的協(xié)作和工程技能的持續(xù)演進。

Chang預言:“由1,000個芯粒組成的芯片并不遙遠,或許就在未來兩三年。我們還有大量研究工作需要開展,必須與大學和新思科技等伙伴攜手,共同實現(xiàn)這一愿景。”

工作流程和工程技能也必須融合。

Immaneni強調(diào):“觀察當下那些正在不斷成長和創(chuàng)新的工程師,你會發(fā)現(xiàn)他們的技能已不再局限于某個特定領域。不再有單一的芯片架構(gòu)師、封裝架構(gòu)師或平臺架構(gòu)師,現(xiàn)在需要的是跨領域的綜合能力。”

Paris補充道:“你需要成為一個通才。真正的價值體現(xiàn)在跨領域知識的融會貫通。如果你只是深入鉆研一個極窄的領域,未必能解決一些邊界模糊的新問題。”

Kapoor總結(jié)說:“不要像工程師那樣看問題,而要像創(chuàng)新者那樣去思考。技術(shù)能力固然重要,但創(chuàng)造力同樣不可或缺。這就是為什么我們需要構(gòu)建一個合作共贏的生態(tài)系統(tǒng)。它是成就一切的基礎。沒有生態(tài)系統(tǒng),我們將寸步難行。”

注明:本文包含2025年1月21至23日在美國加利福尼亞州圣克拉拉舉行的芯粒峰會上,相關人士在專家座談會上發(fā)表的觀點。

-

半導體

+關注

關注

339文章

30725瀏覽量

264036 -

eda

+關注

關注

72文章

3113瀏覽量

182872 -

新思科技

+關注

關注

5文章

956瀏覽量

52892 -

芯粒

+關注

關注

1文章

85瀏覽量

424

原文標題:邁向“千芯粒”時代:新思科技以AI驅(qū)動EDA加速Multi-Die創(chuàng)新

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

軟件定義的硬件輔助驗證如何助力AI芯片開發(fā)

新思科技Multi-Die方案助力車企邁向汽車電子新時代

新思科技助力UCIe 3.0快速落地

伴芯科技重磅發(fā)布DVcrew與PDcrew兩大創(chuàng)新產(chǎn)品,以AI智能體重構(gòu)EDA

新思科技斬獲2025年臺積公司開放創(chuàng)新平臺年度合作伙伴大獎

新思科技UCIe IP解決方案實現(xiàn)片上網(wǎng)絡互連

新思科技網(wǎng)頁端虛擬原型工具的工作流程

新思科技以AI驅(qū)動EDA加速Multi-Die創(chuàng)新

新思科技以AI驅(qū)動EDA加速Multi-Die創(chuàng)新

評論