AI 芯片正推動著萬物智能時代的到來:作為高度專用化的處理器和加速器,AI 芯片專為處理復雜算法與海量數(shù)據(jù)集而設(shè)計。但在當今快速變化、競爭激烈的市場中,要打造一款脫穎而出的 AI 芯片,需要具備哪些條件?答案早在芯片制造之前就已揭曉。

硅前規(guī)劃勢在必行

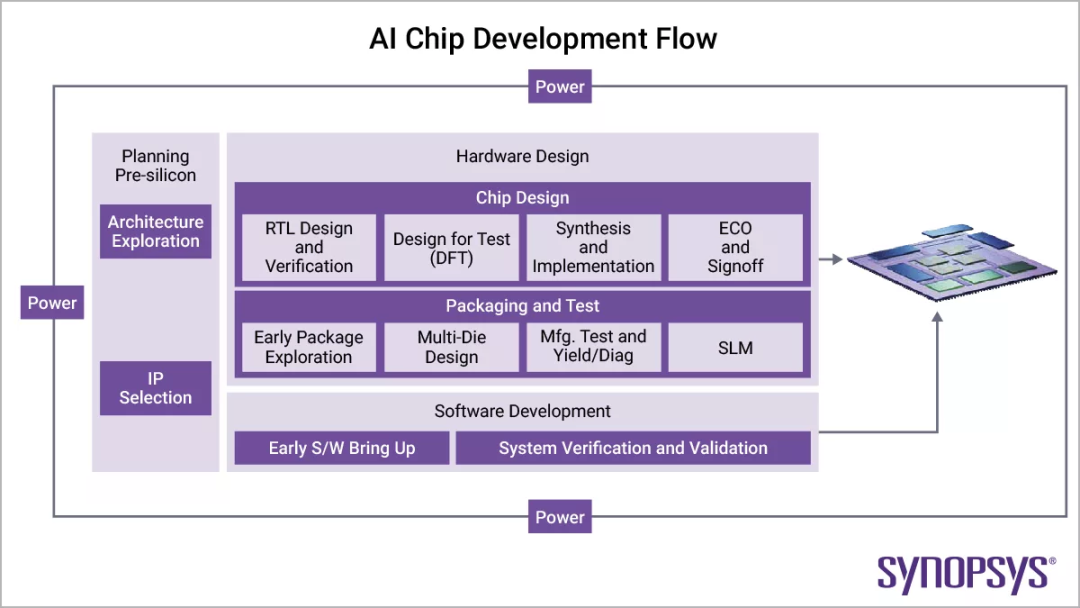

設(shè)計 AI 芯片面臨著巨大的技術(shù)挑戰(zhàn)。開發(fā)者必須在性能、能效、可擴展性和上市時間之間取得平衡,同時還要管控成本與風險。硅前規(guī)劃階段為整個開發(fā)流程繪制藍圖,并制定影響后續(xù)每一步驟的關(guān)鍵決策。

在硅前規(guī)劃中,需明確系統(tǒng)需求、選定架構(gòu),并預判可能遇到的集成挑戰(zhàn)。這不僅是一項技術(shù)工作,更是一項戰(zhàn)略部署。前期投入的時間和資源能夠避免后期出現(xiàn)代價高昂的失誤,助力確保芯片符合市場與客戶的預期。

了解 AI 工作任務

硅前規(guī)劃的首要任務之一,是明確 AI 芯片將要處理的工作任務。工作任務各種各樣,包括圖像識別、大語言模型(LLM)、自動駕駛、數(shù)據(jù)分析等。每種應用場景對算力、內(nèi)存帶寬和連接性的平衡需求各不相同。

開發(fā)者會借助基準測試和代表性數(shù)據(jù)集,對目標工作任務進行詳細的負載分析,從而有助于對性能需求進行精準建模,并及早識別瓶頸。例如,為深度神經(jīng)網(wǎng)絡(luò)訓練設(shè)計的芯片,與為邊緣設(shè)備推理優(yōu)化的芯片,兩者的需求存在顯著差異。

架構(gòu)探索與設(shè)計選擇

明確工作任務負載需求后,便進入架構(gòu)探索階段。工程團隊需考量:是采用同構(gòu)處理單元陣列,還是CPU、GPU 與定制加速器的異構(gòu)組合。內(nèi)存層級結(jié)構(gòu)與互連架構(gòu)的選擇,對支持目標應用也起著關(guān)鍵作用。

借助新思科技 Platform Architect 等先進建模工具,可對不同架構(gòu)進行仿真,并預測架構(gòu)在真實場景下的表現(xiàn)。工程團隊因而能夠在系統(tǒng)架構(gòu)、性能與能效之間做出基于數(shù)據(jù)的決策和權(quán)衡,最終節(jié)省設(shè)計周期后期的時間并降低風險。

低功耗:貫穿始終的優(yōu)先級

在 AI 芯片設(shè)計中,優(yōu)化能效已不再是事后考量,而是成為一項貫穿始終的關(guān)鍵要素。AI 工作任務負載正深刻重塑全球能源格局:據(jù)預測,全球數(shù)據(jù)中心的能耗到 2026 年將高達 1000 太瓦時,相當于一個國家的能源消耗量。這種計算需求的激增,給開發(fā)者帶來巨大壓力,要求設(shè)計出既能提供出眾性能、又保持高能效的解決方案。

為應對這一挑戰(zhàn),半導體團隊正越來越多地采用“左移”方法。通過從設(shè)計周期伊始就優(yōu)先考慮功耗優(yōu)化,開發(fā)者能夠主動評估架構(gòu)選擇、建模功耗,并實施最小化能耗的策略。對能效的早期持續(xù)關(guān)注,使設(shè)計全過程中的決策更具影響力,有助于實現(xiàn)可持續(xù)發(fā)展目標、管控運營成本,打造出能滿足下一代 AI 應用需求的芯片。

IP 選擇與集成

現(xiàn)代 AI 芯片很少從零開始設(shè)計,而是采用將經(jīng)過驗證的知識產(chǎn)權(quán)(IP)模塊(如處理器核心、內(nèi)存控制器和連接接口)集成到設(shè)計中的方法。IP 的選擇與集成是硅前規(guī)劃中的一個關(guān)鍵步驟。

新思科技廣泛多樣的硅驗證 IP 產(chǎn)品組合專為互操作性設(shè)計,并針對所有主流代工廠技術(shù)進行了優(yōu)化,有助于加速集成與驗證流程,同時最大限度降低風險。

AI 芯片設(shè)計的未來

隨著 AI 不斷演進,芯片設(shè)計的挑戰(zhàn)也在持續(xù)升級。先進工藝節(jié)點、Multi-Die 架構(gòu)及新型加速器正不斷突破技術(shù)極限。硅前規(guī)劃依然是駕馭此種復雜性、并最終交付創(chuàng)新解決方案的最有效途徑。

投入資源開展穩(wěn)健的硅前規(guī)劃,是打造能推動下一波技術(shù)突破的 AI 芯片的關(guān)鍵所在。通過將深度工作任務負載分析、全面的架構(gòu)探索、功耗優(yōu)化及經(jīng)過硅驗證的 IP 相結(jié)合,在首片晶圓生產(chǎn)之前,就已為成功筑牢根基。

-

處理器

+關(guān)注

關(guān)注

68文章

20300瀏覽量

253691 -

新思科技

+關(guān)注

關(guān)注

5文章

969瀏覽量

52963 -

AI芯片

+關(guān)注

關(guān)注

17文章

2140瀏覽量

36828

原文標題:AI 芯片決勝于「硅前」:從架構(gòu)探索、功耗優(yōu)化到 IP 集成,全面駕馭復雜性

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

新思科技發(fā)布全新軟件定義硬件輔助驗證解決方案

新思科技首屆Converge大會全新升級啟航

新思科技亮相CES 2026國際消費電子展

新思科技Fusion Compiler自適應場景壓縮技術(shù)提升設(shè)計效率與覆蓋度

Arm計算子系統(tǒng)平臺推動定制AI芯片普及

新思科技測試IO方案加速HPC和AI芯片量產(chǎn)

醫(yī)療PCB供應鏈復雜性與風險管控

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+AI芯片到AGI芯片

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+AI的科學應用

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+可期之變:從AI硬件到AI濕件

AI 芯片浪潮下,職場晉升新契機?

【書籍評測活動NO.64】AI芯片,從過去走向未來:《AI芯片:科技探索與AGI愿景》

新思科技攜手微軟借助AI技術(shù)加速芯片設(shè)計

新思科技VSO.ai如何顛覆芯片驗證

新思科技全面駕馭AI芯片設(shè)計復雜性

新思科技全面駕馭AI芯片設(shè)計復雜性

評論