CDCEL824可編程2 - PLL時鐘合成器:設計與應用指南

在現代電子系統中,精確的時鐘信號是確保系統穩定運行的關鍵因素。今天我們來深入探討德州儀器(TI)的CDCEL824可編程2 - PLL時鐘合成器,看看它如何在各種應用場景中發揮其獨特的優勢。

文件下載:cdcel824.pdf

一、CDCEL824概述

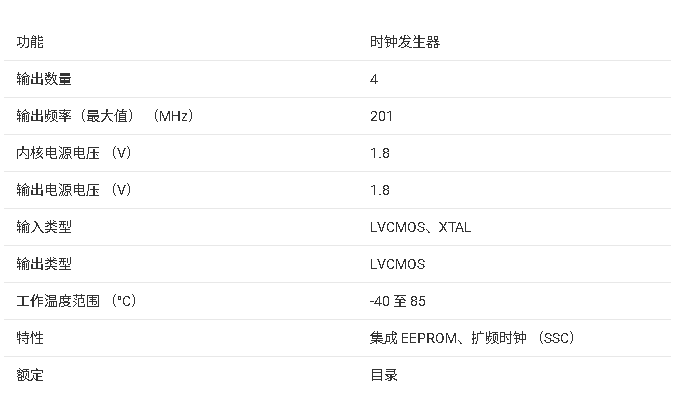

CDCEL824是一款基于模塊化PLL的低成本、高性能可編程時鐘合成器、乘法器和除法器。它能夠從單一輸入頻率生成多達四個輸出時鐘,每個輸出都可以在系統內編程,實現高達201 MHz的任意時鐘頻率,通過兩個獨立可配置的PLL實現靈活的頻率控制。該器件采用1.8 - V電源供電,工作溫度范圍為 - 40°C至85°C,封裝形式為TSSOP,適用于多種應用環境。

二、主要特性

(一)靈活的時鐘驅動

CDCEL824具備三個用戶可定義的控制輸入(S0/S1/S2),可用于頻率切換、輸出使能或電源關閉等功能。這使得它能夠根據不同的應用需求,靈活地調整時鐘輸出,實現0 - PPM時鐘生成。

(二)系統內可編程和EEPROM

該器件支持串行可編程的易失性寄存器和非易失性EEPROM,可用于存儲客戶設置。用戶可以通過SDA/SCL總線對設備進行編程,方便地更改配置參數,而EEPROM則確保了在斷電后配置信息不會丟失。

(三)靈活的輸入時鐘概念

CDCEL824支持多種輸入時鐘源,包括20 MHz至30 MHz的外部晶體和最高130 MHz的單端LVCMOS時鐘信號。對于晶體輸入,片上負載電容可滿足大多數應用需求,并且其值可以在0 pF至20 pF之間進行編程。

(四)可選擇的輸出頻率

輸出頻率最高可達201 MHz,滿足了不同系統對時鐘頻率的要求。同時,低噪聲PLL核心和集成的PLL環路濾波器組件,使得輸出時鐘具有較低的周期抖動(典型值為80 ps),保證了時鐘信號的穩定性和準確性。

三、引腳配置與功能

CDCEL824采用20 - 引腳TSSOP封裝,各引腳具有不同的功能。例如,Xin/CLK引腳用于晶體振蕩器輸入或LVCMOS時鐘輸入,可通過SDA/SCL總線進行選擇;S0、S1和S2為用戶可編程控制輸入,可用于控制設備的不同功能;VDD為1.8 - V電源引腳,VDDOUT為所有輸出的1.8 - V電源引腳等。詳細的引腳功能可以參考數據手冊中的引腳配置表。

四、技術規格

(一)絕對最大額定值

了解器件的絕對最大額定值對于正確使用和保護器件至關重要。CDCEL824的電源電壓范圍為 - 0.5 V至2.5 V,輸入和輸出電壓范圍也有相應的限制。超過這些額定值可能會導致器件永久性損壞。

(二)ESD額定值

該器件具有一定的靜電放電(ESD)保護能力,人體模型(HBM)下的ESD額定值為±2000 V,帶電設備模型(CDM)下為±1500 V。在使用和處理器件時,仍需注意靜電防護,以避免ESD對器件造成損壞。

(三)推薦工作條件

為了確保器件的正常工作,需要在推薦的工作條件下使用。例如,電源電壓VDD推薦為1.7 V至1.9 V,輸出負載電容LVCMOS推薦為不超過15 pF,工作溫度范圍為 - 40°C至85°C等。

五、編程與配置

(一)數據協議

CDCEL824支持字節寫入、字節讀取、塊寫入和塊讀取操作。系統控制器可以通過SDA/SCL總線對設備進行編程,訪問相應的寄存器。在進行EEPROM寫入操作時,需要注意寫入周期和狀態監測,以確保數據的正確寫入。

(二)命令代碼定義

命令代碼用于指定操作類型和字節偏移量。例如,命令代碼的第7位用于區分塊操作和字節操作,第6至0位用于指定字節偏移量。通過合理使用命令代碼,可以準確地對設備進行編程和配置。

(三)寄存器映射

CDCEL824的寄存器包括通用配置寄存器、PLL1配置寄存器和PLL2配置寄存器等。這些寄存器可以用于設置設備的各種參數,如輸入時鐘選擇、PLL頻率選擇、輸出狀態選擇等。用戶可以根據自己的需求,對寄存器進行相應的設置。

六、應用案例

(一)激光距離測量應用

CDCEL824在激光距離測量設備中具有出色的應用表現。其兩個獨立的PLL可以實現所需的低中頻和高最大調制頻率,從而提高測量設備的精度。快速穩定的PLL支持在單次測量中快速切換多個調制頻率,提高了設備的測量速率。同時,低功耗和低成本的特點使得它成為商業激光距離測量設備的理想選擇。

(二)設計要求與步驟

在激光距離測量應用中,需要根據設計目標選擇合適的中間頻率、RF頻率和計數器頻率。較低的RF頻率可以實現更長的測量范圍,而較低的比例(較高的RF頻率和較低的IF頻率)可以降低測量誤差。通過合理設置PLL的乘法器和除法器值,可以計算出所需的輸出頻率。具體的設計步驟和計算公式可以參考數據手冊中的相關內容。

七、布局與電源建議

(一)布局指南

在PCB布局時,當CDCEL824用作晶體緩沖器時,需要注意晶體單元的放置和布線。晶體應盡可能靠近設備,確保從晶體端子到XIN和XOUT的布線長度相同。同時,應避免在晶體和布線區域下方放置接地平面和電源平面,并避免在該區域布線其他信號線,以減少噪聲耦合。

(二)電源建議

在電源方面,沒有嚴格的上電順序要求。但如果先施加VDDOUT,建議將VDD接地,以避免VDDOUT上出現大電流。器件具有上電控制功能,會在1.8 - V電源達到足夠電壓水平后開啟所有內部組件。

八、總結

CDCEL824可編程2 - PLL時鐘合成器以其靈活的時鐘驅動、系統內可編程性、低噪聲PLL核心等特性,在激光距離測量等多種應用場景中表現出色。電子工程師在設計過程中,需要充分了解其技術規格、編程方法和布局要求,以確保設備的正常運行和性能優化。你在使用CDCEL824的過程中遇到過哪些問題呢?歡迎在評論區分享你的經驗和見解。

-

時鐘合成器

+關注

關注

0文章

113瀏覽量

8891

發布評論請先 登錄

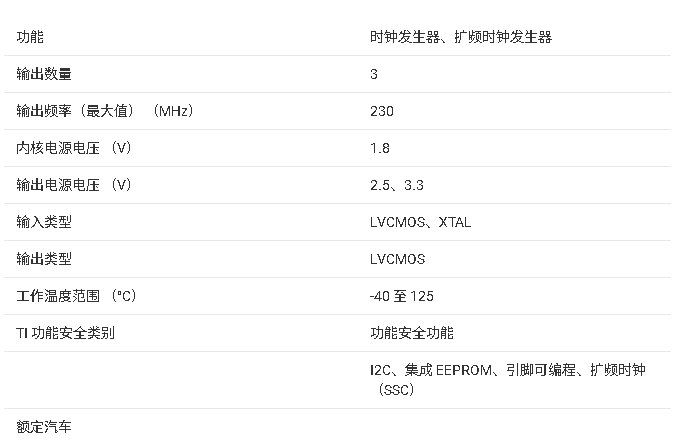

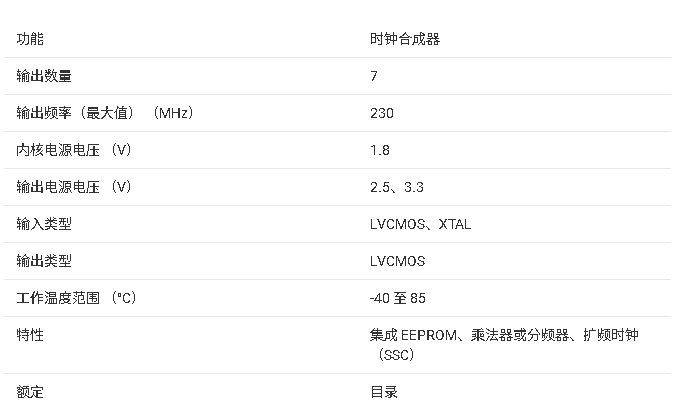

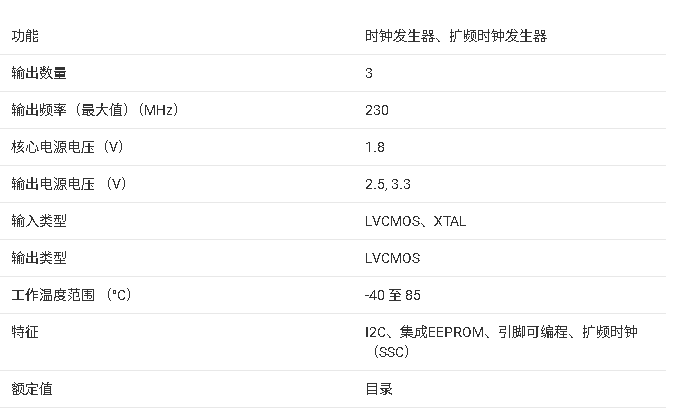

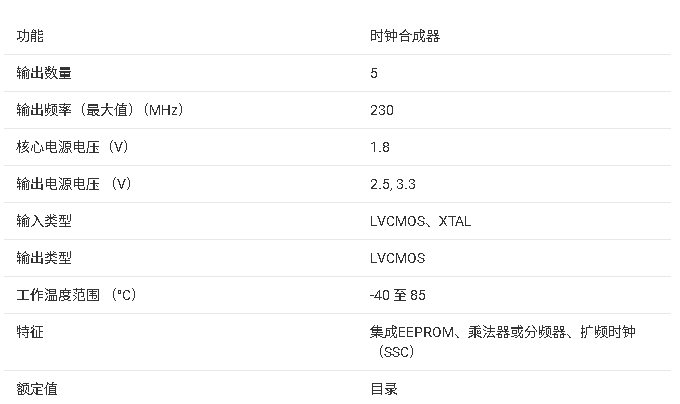

CDCEx937-Q1可編程3-PLL VCXO時鐘頻率合成器數據表

CDCE949-Q1可編程4-PLL VCXO時鐘合成器數據表

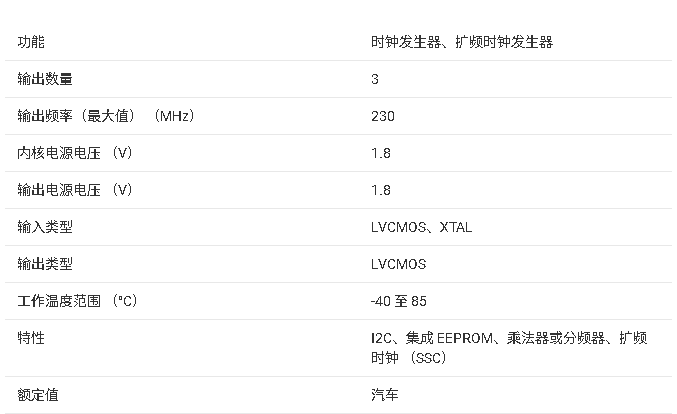

CDCE913-Q1和CDCEL913-Q1可編程1-PLL VCXO時鐘合成器數據表

?CDCE913-Q1和CDCEL913-Q1可編程時鐘合成器技術文檔總結

CDCEL913-Q1 汽車目錄可編程 1-PLL VCXO 時鐘合成器技術手冊

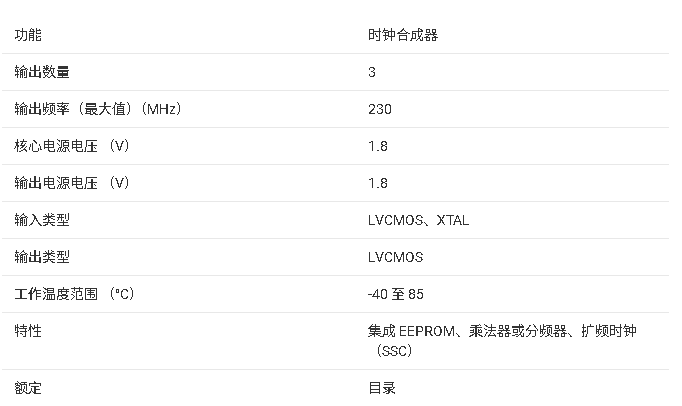

CDCEL913 具有 1.8V LVCMOS 輸出的可編程 1-PLL VCXO 時鐘合成器技術手冊

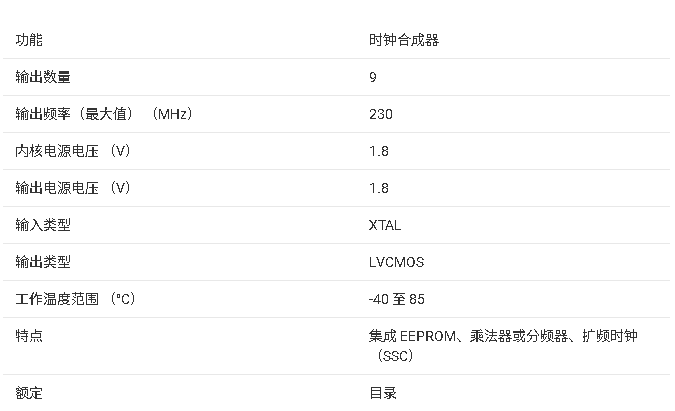

CDCEL949 具有1.8V LVCMOS輸出的可編程4-PLL VCXO時鐘合成器技術手冊

CDCE937 可編程 3-PLL VCXO 時鐘合成器技術手冊

CDCEL824可編程2 - PLL時鐘合成器:設計與應用指南

CDCEL824可編程2 - PLL時鐘合成器:設計與應用指南

評論