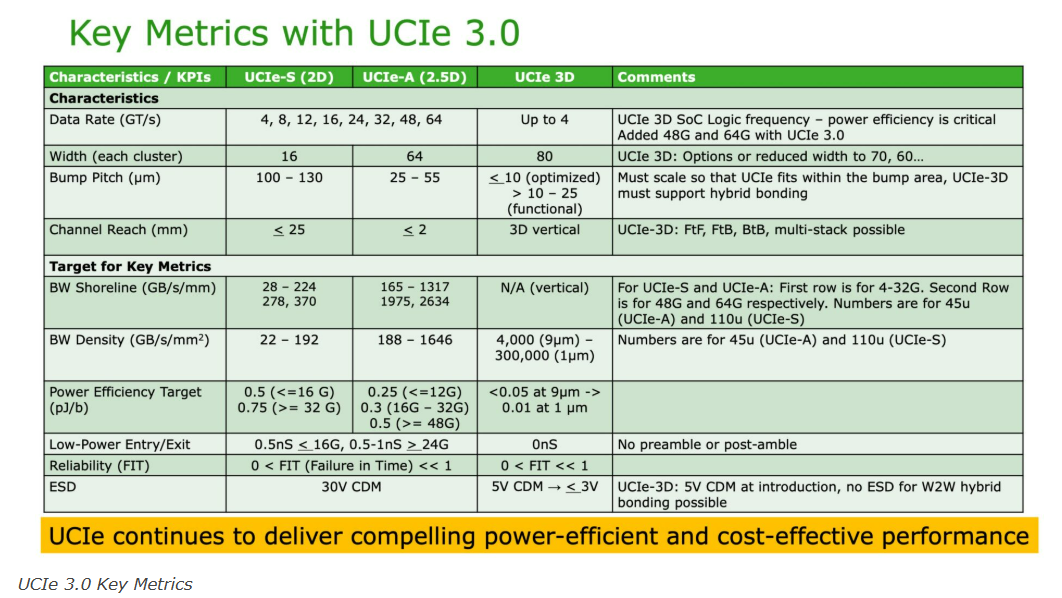

當(dāng)AI大模型參數(shù)規(guī)模突破萬億級別,傳統(tǒng)單芯片設(shè)計遭遇物理極限。芯粒技術(shù)通過模塊化組合突破瓶頸,而芯片間互聯(lián)帶寬成為決定性因素之一。近期,UCIe 3.0規(guī)范將數(shù)據(jù)傳輸速率從UCIe 2.0的32 GT/s提升至48 GT/s和64 GT/s兩檔,實現(xiàn)帶寬密度翻倍增長。這對常受限于芯片面積內(nèi)連接數(shù)量的芯片間通信至關(guān)重要。作為UCIe聯(lián)盟的首批中國成員,奇異摩爾將積極參與并踐行升級后的UCIe 標(biāo)準(zhǔn),為客戶帶來更高性能、更具靈活性和可靠性的片內(nèi)互聯(lián)解決方案,為推動整個芯粒生態(tài)系統(tǒng)的發(fā)展貢獻(xiàn)更多力量。

“芯粒時代”真正到來之前,產(chǎn)業(yè)界需要先解決一個根本問題:如何讓不同工藝、不同廠商、不同功能的小芯片在封裝里像樂高一樣自由拼接,同時還能跑得快、功耗低、成本可控。

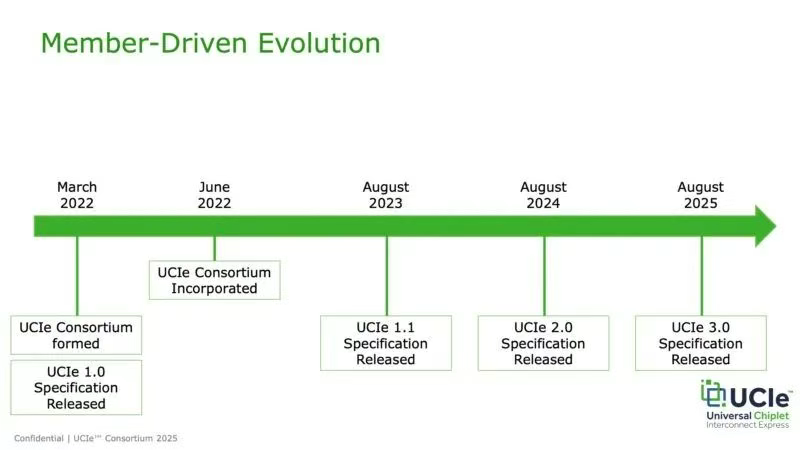

2022 年,英特爾、AMD、臺積電、高通、谷歌、微軟、Meta等 120 余家上下游企業(yè)共同成立 UCIe(Universal Chiplet Interconnect Express)聯(lián)盟,目的就是給這個“樂高世界”制定統(tǒng)一的“接口語言”,實現(xiàn)來自不同供應(yīng)商、在不同晶圓廠生產(chǎn)且具備不同功能的芯片,能夠無縫集成到一個統(tǒng)一且可用的封裝中,從而進(jìn)一步提升系統(tǒng)的靈活性、效率和定制能力。同期,UCIe-Express 1.0規(guī)范正式發(fā)布。

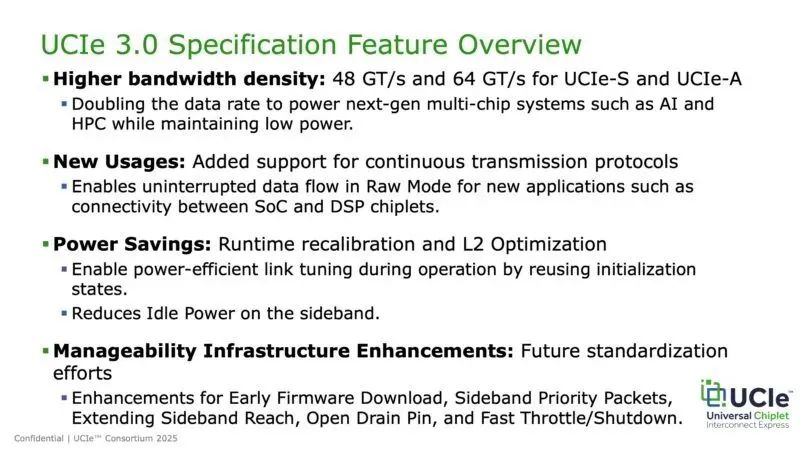

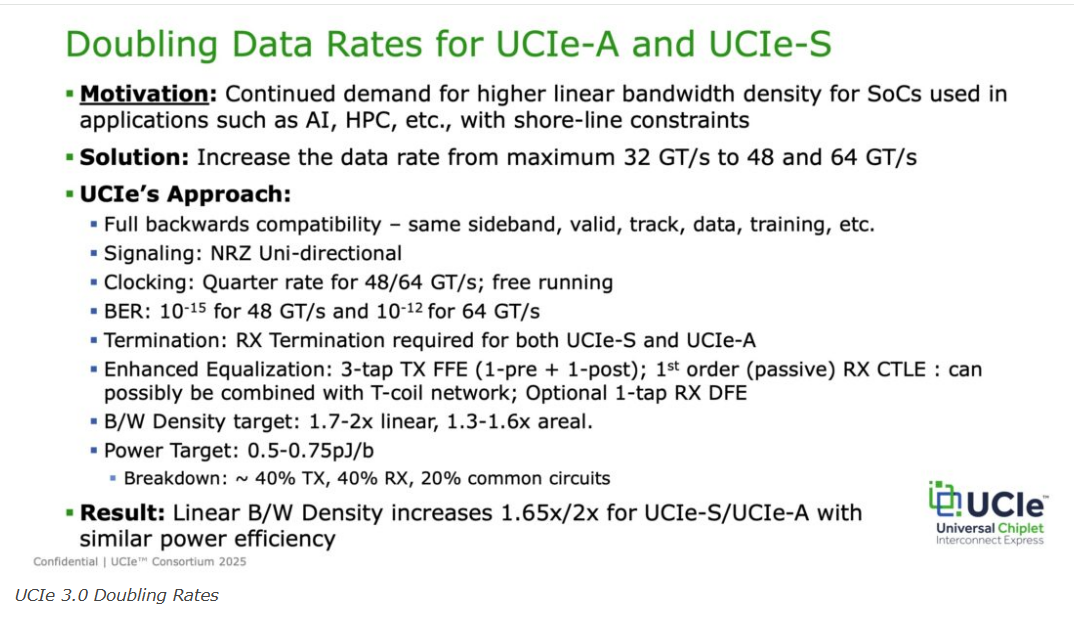

近日,UCIe-Express聯(lián)盟(現(xiàn)已擁有超過140名成員)推出了開放式標(biāo)準(zhǔn)的3.0版本。新版本在能效、管理以及持續(xù)的向后兼容性方面進(jìn)行了全面增強。其中,最引人注目的改進(jìn)在于性能的大幅提升。新規(guī)范支持高達(dá)48 GT/s(每秒千兆傳輸)和64 GT/s的數(shù)據(jù)速率,是前一年推出的UCIe-Express 2.0規(guī)范所提供32 GT/s帶寬的兩倍。

這一性能飛躍有效應(yīng)對了聯(lián)盟所指出的對更高帶寬“永不滿足的需求”,特別是在人工智能、高性能計算和數(shù)據(jù)分析等快速發(fā)展的領(lǐng)域,這些領(lǐng)域高度受限于芯片間連接的物理空間。英特爾高級研究員兼UCIe-Express聯(lián)盟主席Debendra Das Sharma表示:“這類限制在人工智能和高性能計算領(lǐng)域尤為明顯。你需要在給定的空間內(nèi)提供更多的帶寬,但芯片尺寸不會僅僅因為需要更多帶寬而改變。這就是我們提升數(shù)據(jù)速率的原因。”

數(shù)據(jù)傳輸速率的翻倍提升同時適用于UCIe-Express-S(2D標(biāo)準(zhǔn)封裝)和UCIe-Express-A(2.5D高級封裝)設(shè)計。Das Sharma指出,3D設(shè)計方面并未進(jìn)行改動。他解釋道:“3D設(shè)計仍采用較低頻率,原因是其采用的微凸點技術(shù)已能提供極高帶寬——每平方毫米數(shù)百TB的帶寬,甚至超出了當(dāng)前需求,因此3D領(lǐng)域無需升級。而2D和2.5D方面需要在固定空間內(nèi)提供更高的帶寬。”

3.0版本的關(guān)鍵優(yōu)勢在于保持與舊版本的向后兼容性。聯(lián)盟在一份白皮書中強調(diào):“這是一個至關(guān)重要的考慮因素,因為它確保了現(xiàn)有系統(tǒng)和基礎(chǔ)設(shè)施能夠與新標(biāo)準(zhǔn)無縫集成,為系統(tǒng)設(shè)計人員和開發(fā)人員提供平滑過渡,同時確保了與按照前幾代規(guī)范設(shè)計的舊芯片的互操作性。”

Das Sharma表示:“UCIe無處不在,我們將其視為與PCIe相當(dāng)?shù)臉?biāo)準(zhǔn),是一種板級互連技術(shù),應(yīng)用范圍從手持設(shè)備一直延伸到數(shù)據(jù)中心,例如,UCI-Express A可能更適合高端小芯片,如人工智能芯片,因為手持設(shè)備不需要這種級別的帶寬需求。正因如此,我們保留了2D版本。可以說,我們希望構(gòu)建一個覆蓋整個計算領(lǐng)域的連續(xù)標(biāo)準(zhǔn)。這個標(biāo)準(zhǔn)覆蓋范圍還包括數(shù)字信號處理器、無線基礎(chǔ)設(shè)施和雷達(dá)系統(tǒng)等應(yīng)用,以及人工智能、高性能計算、數(shù)據(jù)中心等所有領(lǐng)域。”

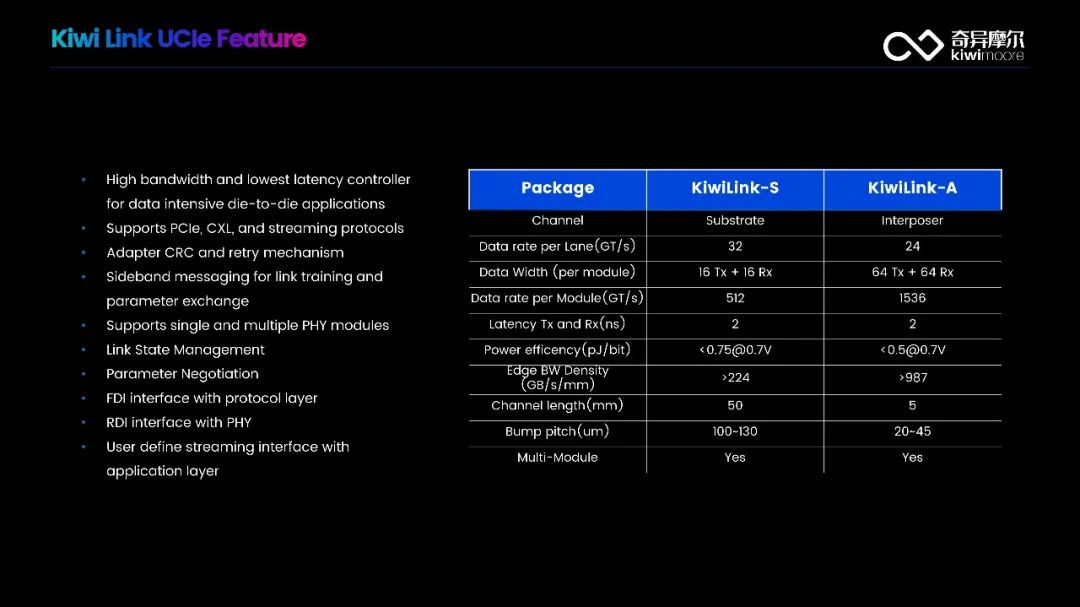

值得一提的是,奇異摩爾是國內(nèi)最早一批加入UCIe 聯(lián)盟的成員之一,深度參與到芯粒生態(tài)系統(tǒng)的建設(shè)與發(fā)展中。奇異摩爾提供完整的UCIe Die-to-Die IP解決方案,包括Controller,PHY和驗證完成的IP。該款I(lǐng)P Standard版本以16-32Gbps的速度運行,實現(xiàn)芯粒之間的超高速互聯(lián)通信,同時保持完全符合UCIe 1.1版本規(guī)范。

奇異摩爾的UCIe Die-to-Die IP包含基于了UCIe標(biāo)準(zhǔn)的低時延Controller(控制器),它包括Die-to-Die Adapter 和Protocol Layer 負(fù)責(zé)Sideband信息的收發(fā)實現(xiàn)Link bring up和Link magement,負(fù)責(zé)Mainband數(shù)據(jù)的發(fā)送和接收。UCIe Controller內(nèi)部Die-to-Die Adapter和Protocol Layer之間支持FDI接口, UCIe Controller與PHY之間支持RDI接口。

奇異摩爾UCIe Die-to-Die IP提供了卓越的高帶寬、極低延遲和較高的可兼容性。為了確保鏈路傳輸?shù)目煽啃裕揑P支持CRC(循環(huán)冗余碼)檢查和重傳機制。其設(shè)計適用于單模塊和多模塊配置,并能夠應(yīng)用于多種封裝形式,包括標(biāo)準(zhǔn)封裝及先進(jìn)封裝。其特點如下:

- 高帶寬-16~32 GT/s 傳輸速率

- 低延時-ns級傳輸延遲

- 多協(xié)議-PCIe、CXL和Streaming等

- 國際標(biāo)準(zhǔn)-全系列支持UCIe標(biāo)準(zhǔn)

- 支持xPU間的Chip-to-Chip互聯(lián)

此外奇異摩爾Kiwi Central IO Die 及Kiwi G2G-IOD 產(chǎn)品系列均基于UCIe協(xié)議設(shè)計,旨在打造規(guī)范且開源的芯粒互聯(lián)互通系統(tǒng)。

UCIe 3.0 規(guī)范的發(fā)布為半導(dǎo)體行業(yè)帶來了新的發(fā)展機遇和變革動力。未來,奇異摩爾將緊跟行業(yè)發(fā)展趨勢,積極參與并踐行升級后的UCIe 標(biāo)準(zhǔn)。憑借在AI互聯(lián)領(lǐng)域的深厚技術(shù)積累和對 UCIe 標(biāo)準(zhǔn)的深刻理解,奇異摩爾有信心通過升級產(chǎn)品,充分發(fā)揮 UCIe 規(guī)范的優(yōu)勢,為客戶帶來更高性能、更具靈活性和可靠性的互聯(lián)解決方案,為推動整個芯粒生態(tài)系統(tǒng)的發(fā)展貢獻(xiàn)更多力量。

關(guān)于我們

AI網(wǎng)絡(luò)全棧式互聯(lián)架構(gòu)產(chǎn)品及解決方案提供商

奇異摩爾,成立于2021年初,是一家行業(yè)領(lǐng)先的AI網(wǎng)絡(luò)全棧式互聯(lián)產(chǎn)品及解決方案提供商。公司依托于先進(jìn)的高性能RDMA 和Chiplet技術(shù),創(chuàng)新性地構(gòu)建了統(tǒng)一互聯(lián)架構(gòu)——Kiwi Fabric,專為超大規(guī)模AI計算平臺量身打造,以滿足其對高性能互聯(lián)的嚴(yán)苛需求。我們的產(chǎn)品線豐富而全面,涵蓋了面向不同層次互聯(lián)需求的關(guān)鍵產(chǎn)品,如面向北向Scale-out網(wǎng)絡(luò)的AI原生超級網(wǎng)卡、面向南向Scale-up網(wǎng)絡(luò)的GPU片間互聯(lián)芯粒、以及面向芯片內(nèi)算力擴展的2.5D/3D IO Die和UCIe Die2Die IP等。這些產(chǎn)品共同構(gòu)成了全鏈路互聯(lián)解決方案,為AI計算提供了堅實的支撐。

-

封裝

+關(guān)注

關(guān)注

128文章

9248瀏覽量

148607 -

奇異摩爾

+關(guān)注

關(guān)注

0文章

79瀏覽量

4037 -

芯粒

+關(guān)注

關(guān)注

1文章

85瀏覽量

424

原文標(biāo)題:UCIe 3.0 規(guī)范發(fā)布,奇異摩爾Die-to-Die片內(nèi)互聯(lián)方案持續(xù)升級

文章出處:【微信號:奇異摩爾,微信公眾號:奇異摩爾】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

高頻高側(cè)/低側(cè)驅(qū)動器UCC27201A-DIE:性能與應(yīng)用解析

TPS7A4001-DIE:超高耐壓線性穩(wěn)壓器的特性與應(yīng)用解析

UC1843A - DIE:電流模式PWM控制器的卓越之選

THS4541-DIE:高性能全差分放大器的設(shè)計與應(yīng)用

高頻N溝道MOSFET驅(qū)動器UCC27201A - DIE的深度解析

新思科技以AI驅(qū)動EDA加速Multi-Die創(chuàng)新

奇異摩爾Networking for AI生態(tài)沙龍成功舉辦

奇異摩爾助力OISA全向智感互聯(lián)IO芯粒技術(shù)白皮書發(fā)布

Cadence基于臺積電N4工藝交付16GT/s UCIe Gen1 IP

晶圓制造中的Die是什么

DAF膠膜(Die Attach Film)詳解

新思科技UCIe IP解決方案實現(xiàn)片上網(wǎng)絡(luò)互連

HMC347A-Die單刀雙擲(SPDT)

UC1843A-DIE 采用 DIE 封裝的航天級 30V 輸入、1A 單輸出 500kHz PWM 控制器數(shù)據(jù)手冊

奇異摩爾Die-to-Die片內(nèi)互聯(lián)方案持續(xù)升級

奇異摩爾Die-to-Die片內(nèi)互聯(lián)方案持續(xù)升級

評論