THS4541-DIE:高性能全差分放大器的設計與應用

在電子工程師的日常設計中,選擇一款合適的放大器至關重要。今天,我們就來深入探討一下TI推出的THS4541-DIE全差分放大器,看看它在性能、應用和設計方面有哪些獨特之處。

文件下載:ths4541-die.pdf

一、產品概述

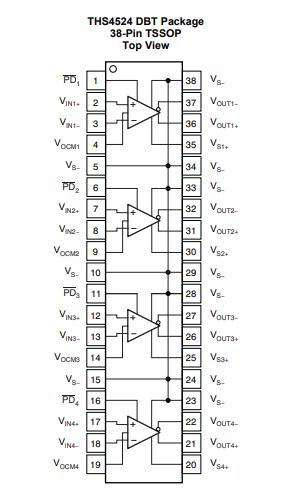

THS4541-DIE是一款低功耗、基于電壓反饋的全差分放大器(FDA)。它具有輸入共模范圍低于負軌、軌到軌輸出的特點,是一款裸片產品,適用于多芯片模塊(MCM)、系統級封裝(SiP)、板上芯片(COB)、混合電路以及對尺寸要求極高的系統。該產品專為低功耗數據采集系統設計,在高性能模數轉換器(ADC)或數模轉換器(DAC)接口設計中,對高密度要求較高的場景中表現出色。

二、核心特性

(一)電氣性能

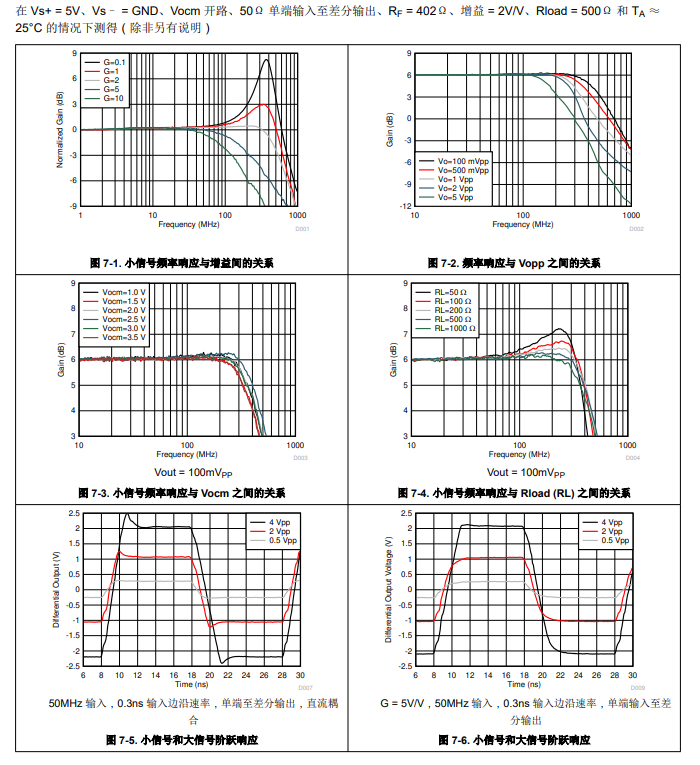

- 帶寬與增益:小信號帶寬在增益為2V/V時大于500MHz,增益帶寬積高達850MHz。在不同增益設置下,如增益為1、2、5、10時,小信號帶寬分別可達620MHz、500MHz、210MHz、125MHz 。大信號帶寬在增益為2、輸出2VPP時為340MHz。

- 壓擺率:壓擺率高達1500V/μs,能夠快速響應輸入信號的變化,適用于高速信號處理。

- 失真特性:在10MHz、2VPP、(R{L}=500 Omega)條件下,二次諧波失真((HD{2}))為 –95 dBc,三次諧波失真((HD_{3}))為 –90 dBc,保證了信號的高保真度。

- 噪聲性能:輸入電壓噪聲在(f>100 kHz)時為2.2 nV/√Hz,輸入電流噪聲在(f > 1 MHz)時為1.9 pA/√Hz,有效降低了噪聲對信號的干擾。

- 直流特性:開環電壓增益((A_{OL}))典型值為119dB,輸入失調電壓漂移典型值為±0.5 μV/°C,具有良好的直流穩定性。

(二)電源特性

- 電源范圍:單電源電壓范圍為2.7V至5.4V,分裂電源電壓范圍為±1.35V至±2.7V,具有較寬的電源適應性。

- 靜態電流:在5V電源下,靜態電流為10.1mA,并且具有掉電功能,掉電時靜態電流典型值為2μA,有效降低了功耗。

(三)輸入輸出特性

- 輸入特性:具有負軌輸入(NRI)能力,輸入共模范圍可低于負軌,能夠直接支持直流耦合、以地為中心的雙極性輸入信號。

- 輸出特性:軌到軌輸出(RRO),輸出電壓擺幅接近電源軌,輸出電壓低為((V{s–}) + 0.2)至((V{s–}) + 0.25)V,輸出電壓高為((V{s+}) – 0.25)至((V{s+}) – 0.2)V。

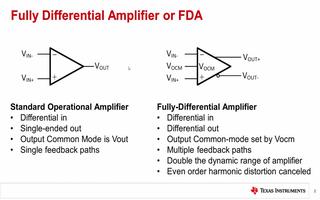

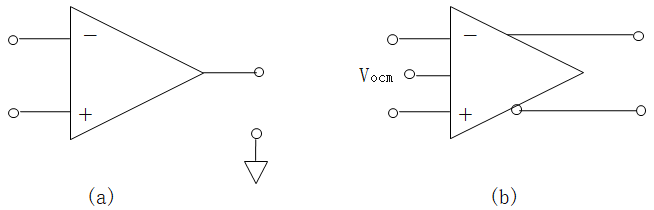

三、功能框圖與原理

(一)功能框圖

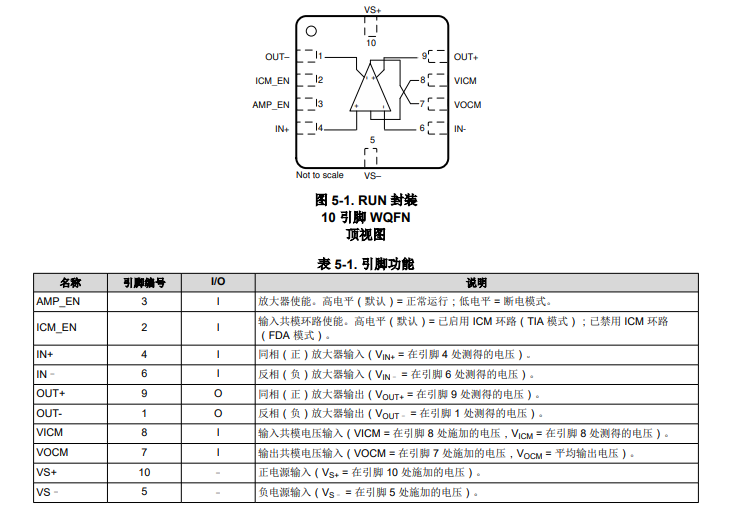

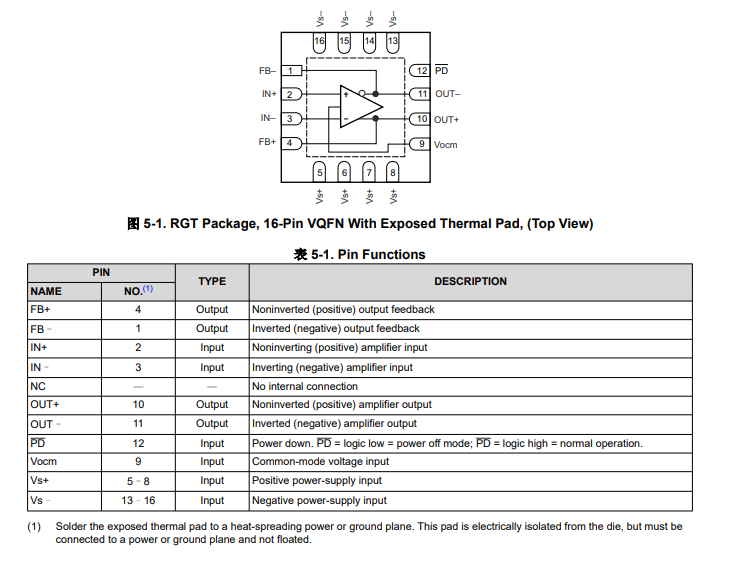

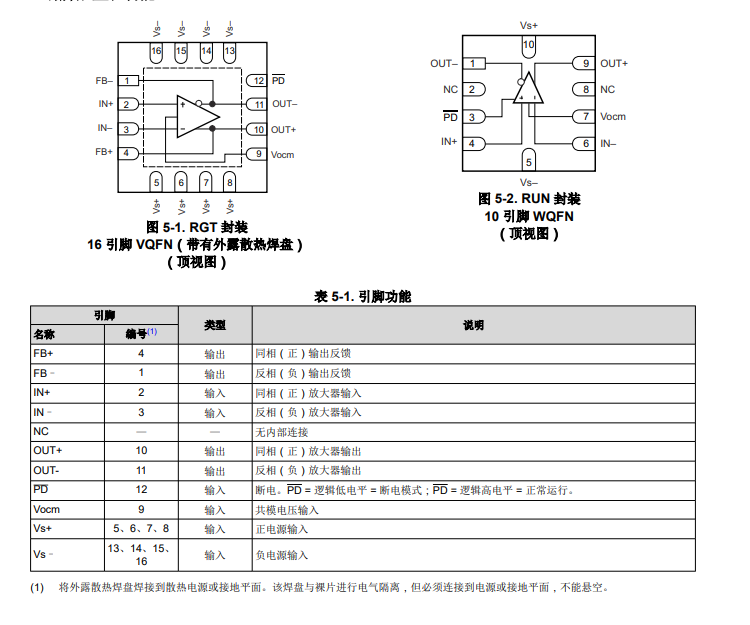

THS4541-DIE的功能框圖包含了核心的差分輸入輸出模塊、共模誤差放大器以及電源控制模塊。輸入信號通過差分輸入模塊進入放大器,輸出信號的共模電壓由共模誤差放大器進行監測和調整,以確保輸出平均電壓符合Vocm引腳設定的目標值。

(二)工作原理

- 差分I/O模塊:是一個經典的高開環增益級,具有約900Hz的主極點。電壓反饋結構使其在850MHz處具有單極點、單位增益的開環增益(Aol)。高速差分輸出端包含一個內部平均電阻網絡,用于檢測輸出共模電壓。

- 共模控制:輸出共模電壓由Vocm引腳控制。當Vocm引腳浮空時,參考電壓為電源電壓的一半;當Vocm引腳接特定電壓時,共模誤差放大器會將輸出平均電壓調整到該目標值。

- 電源控制:通過PD引腳進行電源控制。當PD引腳為高電平時,放大器正常工作;當PD引腳為低電平(接近負電源0.7V以內)時,放大器進入低功耗掉電狀態,靜態電流可降至約2μA。

四、典型應用

(一)高性能ADC驅動

THS4541-DIE非常適合作為低功耗、高性能ADC的驅動放大器,如SAR、ΔΣ和流水線型ADC。在與ADC34J22這款低功耗、12位、四通道50-MSPS JESD 204B ADC接口的示例中,通過合理的電路設計,實現了2V/V的增益、50Ω的輸入匹配,并在ADC前端添加了三階貝塞爾濾波器,有效控制了寬帶噪聲,減少了對SNR和SFDR性能的影響。

(二)單端轉差分放大器

能夠輕松實現單端輸入信號到差分輸出信號的轉換,并且輸出信號可以圍繞用戶控制的共模電平對稱擺動。在實際應用中,需要考慮輸入引腳的共模電壓變化對輸入阻抗的影響,合理選擇電阻值。

(三)差分有源濾波器和差分跨阻放大器

可用于構建差分有源濾波器,實現對信號的濾波處理;也可作為DAC輸出的差分跨阻放大器,實現電流到電壓的轉換。

五、設計要點

(一)電源設計

- 建議使用標稱值為+3V至+5V的單電源供電,電源電壓公差在2.7V至5.4V范圍內。

- 為了減少電源噪聲,需要進行電源去耦。在器件電源引腳的接地平面上使用0.1μF的高頻去耦電容,同時可使用2.2μF的較大電容,可放置在離器件電源引腳稍遠的位置并在多個器件間共享。對于雙電源供電,還應在兩個電源之間添加去耦電容。考慮使用X2Y電源去耦電容,其自諧振頻率比標準電容更高,能提供更好的高頻去耦效果。

- 若需要將線性輸出擺幅擴展到地,可以使用LM7705固定–230-mV的負電源發生器提供小的負電源電壓。

(二)布局設計

- 對于高速信號路徑的布局,要使用微帶布局技術,確保差分信號走線的阻抗匹配。

- 輸入求和節點對寄生電容非常敏感,應盡量縮短Rg元件到器件引腳一側的走線長度,而Rg元件的另一側到信號源或地的走線長度可適當增加。

- 每個THS4541-DIE應連接一個0.1-μF的電容到附近的接地平面。對于級聯或多個并行通道,在較大電容和局部高頻去耦電容之間添加鐵氧體磁珠通常是有用的。

(三)保護設計

在輸入過驅動情況下,內部輸入二極管可安全吸收高達±15mA的電流。對于需要吸收更多電流的設計,可考慮添加外部保護二極管,如BAV99。

六、總結

THS4541-DIE全差分放大器憑借其出色的電氣性能、靈活的電源配置和豐富的應用場景,為電子工程師在低功耗、高性能數據采集系統設計中提供了一個優秀的選擇。在實際設計過程中,我們需要充分考慮其特性和設計要點,合理布局和優化電路,以實現最佳的系統性能。大家在使用THS4541-DIE過程中遇到過哪些問題或者有什么獨特的應用經驗呢?歡迎在評論區分享交流。

-

數據采集系統

+關注

關注

5文章

309瀏覽量

32099 -

全差分放大器

+關注

關注

0文章

41瀏覽量

9300

發布評論請先 登錄

求助,關于THS4541-DIE差分運放供電問題求解

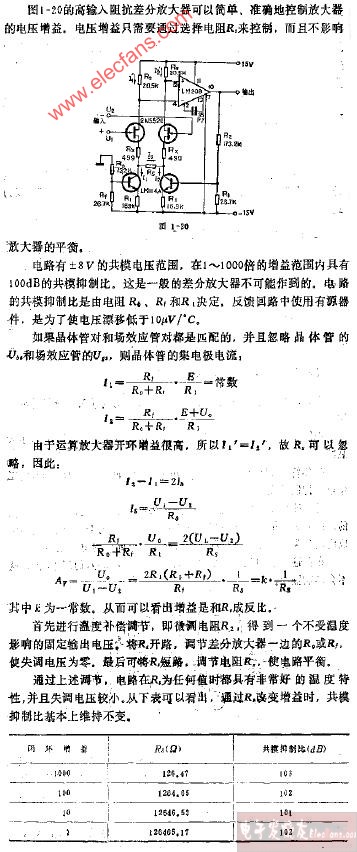

使用全差分放大器構建儀表放大器

全差分放大器OPA1632資料分享

全差分放大器和單端轉差分放大器的主要區別是什么?

THS4541-DIE 負軌輸入、軌到軌輸出、精密850MHz全差分放大器技術手冊

THS4567 具有VICM和VOCM控制的、220MHz、CMOS輸入全差分放大器技術手冊

THS4541-Q1 汽車類高速差分、IO放大器技術手冊

THS4541 高速差動、IO、放大器技術手冊

THS4541-DIE:高性能全差分放大器的設計與應用

THS4541-DIE:高性能全差分放大器的設計與應用

評論