ZCU104 評(píng)估套件可幫助設(shè)計(jì)人員為監(jiān)控、高級(jí)駕駛員輔助系統(tǒng) (ADAS)、機(jī)器視覺(jué)、增強(qiáng)實(shí)境 (AR)、無(wú)人機(jī)和醫(yī)學(xué)成像等嵌入式視覺(jué)應(yīng)用快速啟動(dòng)設(shè)計(jì)。該套件采用帶視頻編解碼器的 Zynq? UltraScale+? MPSoC EV 器件,支持嵌入式視覺(jué)使用案例的許多常見外設(shè)及接口。隨附提供的 ZU7EV 器件配備四核 ARM? Cortex?-A53 應(yīng)用處理器、雙核 Cortex-R5 實(shí)時(shí)處理器、Mali?-400 MP2 圖形處理單元、支持 4KP60 的 H.264/H.265 視頻編解碼器和 16nm FinFET+ 可編程邏輯。

主要性能和優(yōu)勢(shì)

-

FPGA

+關(guān)注

關(guān)注

1660文章

22408瀏覽量

636207 -

嵌入式

+關(guān)注

關(guān)注

5198文章

20442瀏覽量

333964 -

MPSoC

+關(guān)注

關(guān)注

0文章

203瀏覽量

25171

原文標(biāo)題:Xilinx Zynq UltraScale+MPSoC ZCU104 評(píng)估套件

文章出處:【微信號(hào):FPGA-EETrend,微信公眾號(hào):FPGA開發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

基于ZYNQ-MZ702P開發(fā)板實(shí)現(xiàn)以太網(wǎng)通信

如何在Zynq UltraScale+ MPSoC平臺(tái)上通過(guò)JTAG啟動(dòng)嵌入式Linux鏡像

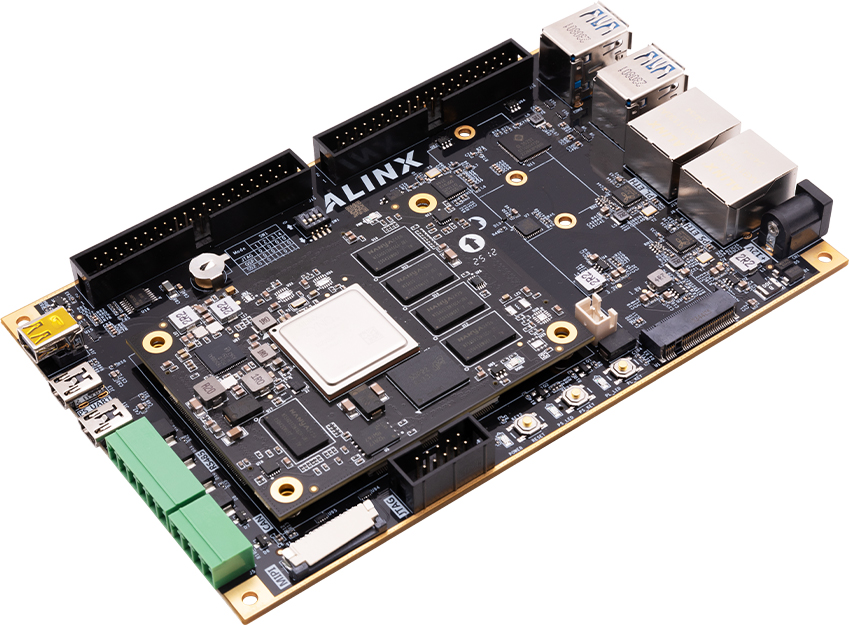

新品上市!AMD Zynq UltraScale+MPSoC EG異構(gòu)多處理開發(fā)平臺(tái)

如何在ZYNQ本地部署DeepSeek模型

AMD UltraScale架構(gòu):高性能FPGA與SoC的技術(shù)剖析

ALINX教程分享_Zynq UltraScale+ MPSoC PYNQ3.1.2移植

同系列性能更強(qiáng)!面向高性能 AI 應(yīng)用,AXU2CGB-I 有何亮點(diǎn)?

雙Zynq MPSoC PS側(cè)PCIe高速DMA互連解決方案

AMD Vivado IP integrator的基本功能特性

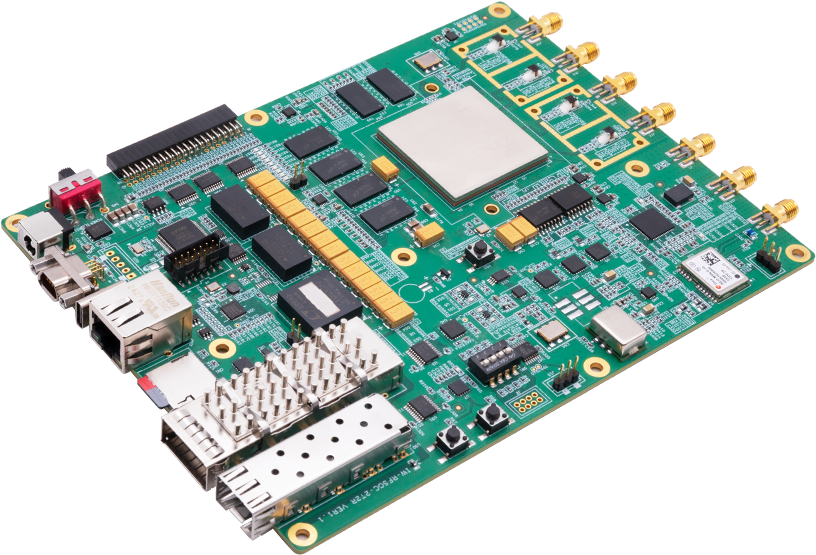

璞致電子 UltraScale+ RFSoC 架構(gòu)下的軟件無(wú)線電旗艦開發(fā)平臺(tái)

PZ/璞致【PZ-ZU19EG-KFB】—ZYNQ UltraScale + 賦能異構(gòu)計(jì)算與高性能嵌入式系統(tǒng)開發(fā)

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 異構(gòu)架構(gòu)下的智能邊緣計(jì)算標(biāo)桿

高性能緊湊型 RFSoC FPGA 開發(fā)平臺(tái) AXW22,重塑射頻開發(fā)體驗(yàn)

Xilinx Ultrascale系列FPGA的時(shí)鐘資源與架構(gòu)解析

采用Zynq UltraScale+MPSoC進(jìn)行基于軟件的創(chuàng)造性應(yīng)用開發(fā)

采用Zynq UltraScale+MPSoC進(jìn)行基于軟件的創(chuàng)造性應(yīng)用開發(fā)

評(píng)論