作者:AMD 工程師 Simreet Behera & Abhinav Dubey

本文主要介紹了 AMD Vivado IP integrator (IPI) 的諸多功能特性。我們將講解 Vivado IP integrator 的各項基本功能,欲知詳情,請參閱以下 GitHub 倉庫中所含教程:

https://github.com/Xilinx/Vivado-Design-Tutorials/tree/2022.1/Design_Flow_Tutorials/IP_Integrator

我們還將帶您了解在 AMD Zynq UltraScale+ MPSoC 開發板與 AMD Versal 自適應 SoC 開發板上使用 IP integrator 時,兩種設計流程之間存在的差異。

除此之外,我們將介紹塊設計容器 (BDC),最后是介紹“Module Referencing”(模塊引用)功能,該功能可用于將 AMD IP (XCI)、RTL 設計或塊設計 (BD) 例化到另一個 BD 中。

IPI 的基本功能特性

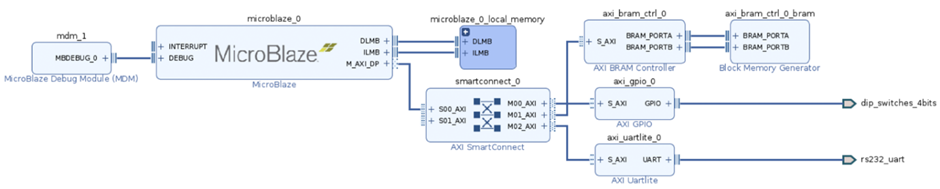

我們將在基于微處理器的設計中使用 AMD Zynq UltraScale+ MPSoC 開發板來介紹 Vivado IPI 的基本功能特性,如從 IP 目錄添加 IP、運行連接自動化、塊自動化設置、創建層級和使用地址編輯器。

在 IPI 中,基于微處理器的設計流程如下:

1. 從 Vivado IP 目錄添加 IP

微處理器 IP

根據您的設計規范,將相關 IP 添加到新的塊設計 (BD) 中,如 MicroBlaze 處理器 IP、Zynq 處理器系統 IP 等

互連 IP

AXI Interconnect、AXI Smart Connect 等

存儲器接口 IP

PS DDR4 Controller、AXI Block RAM (BRAM) Controller 等

接口 IP

AXI General Purpose Input/Output (GPIO)、AXI UART_lite 等

2. 使用設計輔助功能

IP integrator 提供了一項名為“Designer Assistance”(設計輔助)的功能,其中包含“Connection Automation”(自動連接)、“Block Automation”(塊自動化設置)和“Board Automation”(板自動化設置)。它能幫助您在不同塊之間建立內部連接以及建立從各塊到外部接口的連接,從而組建一個基本 IP 子系統。在設計中使用 AMD MicroBlaze 處理器或 Zynq UltraScale+ MPSoC (Zynq_ultra_ps_e_0) 等嵌入式處理器時,就會提供“Block Automation”功能。

如果使用開發板(如 ZCU102 評估板)來創建工程,則“Board Automation”功能可協助將 IP 接口連接到外部開發板。由于所選開發板的所有 I/O 管腳分配和屬性都已固定,因此該功能還會處理這些分配和屬性。

例如,在 MicroBlaze 設計中,“Connection Automation”功能將幫助您完成 UART 和 GPIO 接口的連接以及 AXI BRAM Controller 到 Block Memory Generator 的連接。

3. 創建層級

您可運用多種不同方法來更改畫布上的視圖,以便對各塊進行更妥善的組織。其中有一項功能是創建層次結構,用于對一個或多個塊進行分組。層次結構不僅有助于對畫布上的塊進行組織,還能對塊設計的不同部分進行復制。例如,您可以按住 Ctrl 鍵并逐一點擊 microblaze_0、microblaze_0_local_memory 和 mdm_1 塊來創建一個層次結構。

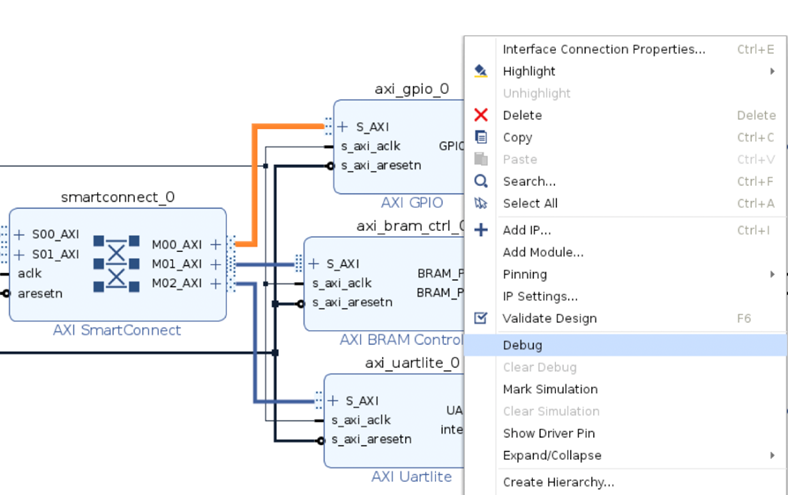

4. 在 IPI 中標記信號以供調試

IP integrator 中的 System ILA 調試核支持您對塊設計執行系統內調試。需要監控設計內的接口和信號時,即可使用此功能。

如下圖所示,您只需右鍵單擊信號線并從上下文菜單中選擇“Debug”(調試),即可標記 AXI SmartConnect 與 AXI GPIO IP 之間的接口。

5. 創建和實現頂層設計

完成 IP 子系統設計后,您可將其作為模塊或塊包含在頂層設計內,也可以將其用作為頂層設計本身。但無論如何,您都需要為子系統設計生成 HDL 文件。這是通過生成輸出文件完成的,隨后會為設計啟動中的每個 IP 運行非關聯 (OOC) 流程。然后,您將創建 HDL 封裝文件,并為設計生成比特流。該步驟包括了綜合與實現。

如需了解更多信息,請參閱《Vivado Design Suite 用戶指南:采用 IP integrator 設計 IP 子系統》(UG994):

https://docs.amd.com/r/en-US/ug994-vivado-ip-subsystems

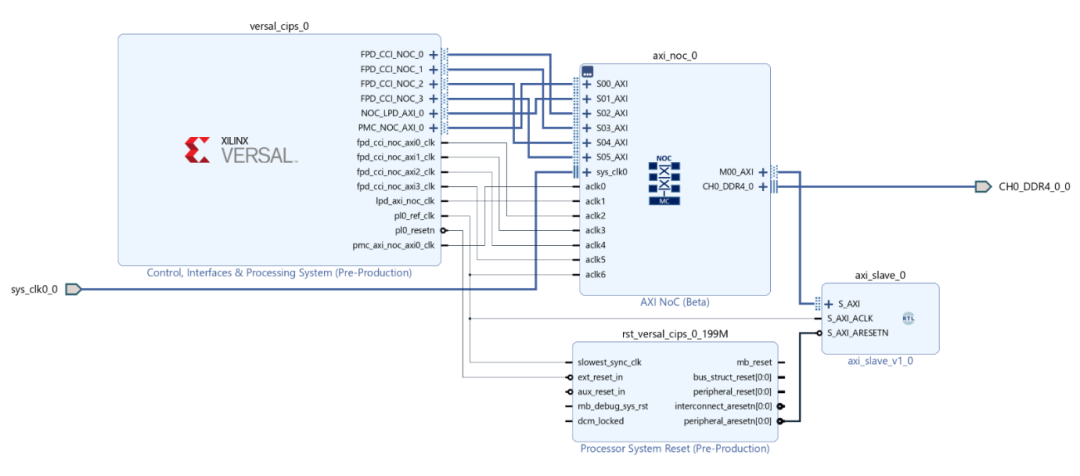

使用 IP integrator 完成基本 Versal 設計

AMD Versal 自適應 SoC 計算加速平臺包含多個處理器,每個處理器都具有不同的計算功能用以滿足各種應用需求。所有器件都包括處理器系統 (PS) 和平臺管理控制器 (PMC)。此外還包括片上網絡 (NoC) 互連,用于支持所有處理器接入 DDR 存儲器控制器以及器件內的其他資源。

Versal 自適應 SoC 支持 2 種設計流程:傳統設計流程和基于平臺的設計流程。

本文我們將重點介紹傳統設計流程,因為這種設計僅由 RTL 和 IP 組成。

一個基本的 Versal 設計涉及通過配置 Control, Interface, and Processing System (CIPS) IP 核來選擇合適的啟動器件和外設。這對于 Versal 設計至關重要,因為平臺管理控制器 (PMC) 整合在 CIPS IP 中,必須配置 PMC 才能讓 Versal 器件正確啟動。此外,硬化的 DDR 存儲器控制器 (DDRMC) 只能通過 NoC IP 來訪問。要使用硬化的 DDR 存儲器控制器,您的設計應包含 NoC IP。

您可根據自己的需要通過 CIPS 自定義 GUI 來自定義 CIPS。例如,您可以更改 QSPI 模式、啟動模式,設置適當的 I/O 管腳等。

以下是包含 AXI NoC IP 的基本 Versal 設計的截圖:

您可以對這個設計執行“Save”(保存)、“Validate”(確認)和“Implement”(實現),最后生成比特流(PDI 文件),用于燒錄 Versal 開發板。

如需了解有關 Versal 設計流程的更多信息,請參閱《Versal 自適應 SoC 設計指南》(UG1273):

https://docs.amd.com/r/zh-CN/ug1273-versal-acap-design/%E6%A6%82%E8%BF%B0

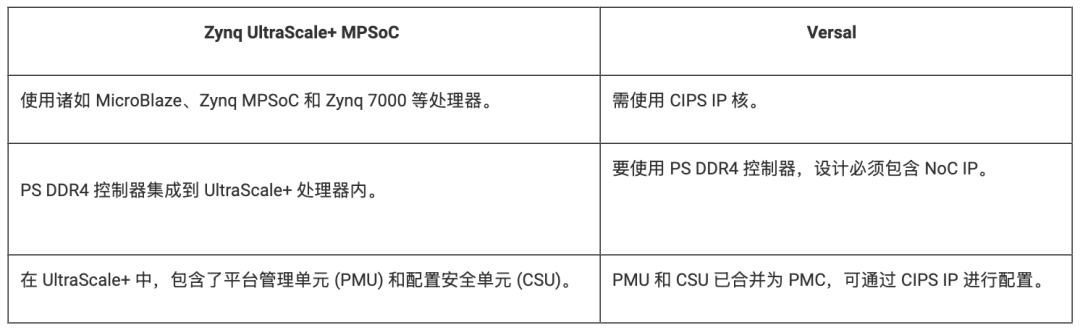

基本 Zynq UltraScale+ MPSoC 設計與 Versal 設計之間的差異

使用 Zynq UltraScale+ MPSoC 開發板進行設計與 Versal 開發板進行設計相比,有些設計注意事項需要考量。下表提到了這兩種架構在設計上的一些差異。

如需了解有關這兩種架構的更多信息,請參閱《Versal 自適應 SoC 技術參考手冊》 (AM011):

https://docs.amd.com/r/en-US/am011-versal-acap-trm

和《Zynq UltraScale+ 器件 TRM》(UG1085):

https://docs.amd.com/v/u/en-US/ug1085-zynq-ultrascale-trm

塊設計容器簡介

塊設計容器 (BDC) 擴展了 Vivado IP integrator 的分層塊功能。如果塊設計 (BD) 可包含用戶選定的 IP 塊且數量不限,那么分層塊能用于在該設計層級內創建新的層次。塊設計容器 (BDC) 功能特性會將分層塊及其中所含內容轉變為單獨的塊設計 (BD) 本身。生成的塊設計定義為 BD 設計源文件,并且也可在其他塊設計工程內使用。使用 BDC 的好處在于,父 BD 與子 BD 之間的邊界是透明的。例如,參數傳輸和地址分配都可以通過這個層級來完成。

BDC 同時支持自上而下的設計流程和自下而上的設計流程。

自上而下流程

在自上而下流程中,首先會創建頂層塊設計的流程圖,然后按適當的層級將一組 IP 塊作為子塊推送到 BDC 內。借助外部接口和特定功能塊的詳細信息,即可構建和驗證頂層 BD。隨后,設計團隊可以復用該頂層 BD 來開發其 BDC 部分。在為所有團隊成員復制單個工程或者處理以相同器件為目標的多個工程的過程中即可完成此操作。

自下而上流程

在自下而上設計流程中,子塊設計是單獨創建的,您需要在頂層塊設計中將這些子塊作為 BDC 來加以例化。團隊成員可以集中精力為所分配的設計分區開發 BD,以便在頂層 BD 中將該 BD 作為 BDC 來加以復用,或后續在另一個工程中一起復用。

IPI 中的模塊引用

IP integrator 的模塊引用 (ModuleRef) 功能特性支持您快速將來自 Verilog 或 VHDL 源文件的模塊或實體定義直接添加到自己的塊設計中。此方法支持快速添加 RTL 模塊,無需將 RTL 封裝為 IP 再通過 Vivado IP 目錄來添加。

模塊引用流程很快,但不具備下列使用 IP 目錄來處理時所具備的優勢,如:

1. 提供精確定義的 IP,可通過 IP 目錄來管理

2. 能夠在多個設計中使用這些 IP

3. 能夠在有新版本 IP 可用時進行升級

您可為塊設計、XCI 文件和 RTL 模塊創建模塊引用。

要在不同 BD 中使用 IP 或 BD 模塊引用功能,您必須首先創建 AI 引擎接口拼塊 RTL 文件。AI 引擎接口拼塊文件只是 RTL 模塊/封裝文件,必須將其作為工程源文件添加到設計中,此文件充當“掛鉤”用于連接工程要引用的其他 IP 或 BD 源文件。您可以從 IP 或 BD 例化模板或者從生成的 BD 封裝文件中創建一個新的 AI 引擎接口拼塊 RTL 文件(例如:包含“shim”模塊的 shim.v)。

例如,將 MicroBlaze 處理器 IP 例化到另一個 BD 內時,所用的 shim.v 文件如下所示:

限制

1. ModuleRef 不得包含 CIPS 或 NoC IP。

2. ModuleRef 無法例化一個或多個 DCP 模塊。

3. ModuleRef 無法例化一個或多個 ModuleRef(即“嵌套 ModuleRef”)。

4. ModuleRef 無法使用塊設計容器 (BDC) 技術來例化 BD。

結論

在本篇博文中,我們了解了如何利用 IP integrator 的眾多功能特性來創建基本的 MicroBlaze 設計和 Versal 設計,并觀察了這兩種設計流程之間的差異。

我們還談及如何通過 2 種受支持的塊設計容器流程(自上而下流程和自下而上流程)來擴展 IPI 的分層功能。

最后,我們講解了全新的模塊引用功能特性,它支持您快速將來自 Verilog 或 VHDL 源文件的模塊或實體定義直接添加到自己的塊設計中。

-

amd

+關注

關注

25文章

5692瀏覽量

140128 -

微處理器

+關注

關注

11文章

2431瀏覽量

85958 -

開發板

+關注

關注

26文章

6320瀏覽量

118867 -

Zynq

+關注

關注

10文章

630瀏覽量

49492 -

Vivado

+關注

關注

19文章

858瀏覽量

71211

原文標題:開發者分享|AMD Zynq? UltraScale+? MPSoC 和 Versal? 的 IPI 基本功能特性

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

熟悉Vivado HLS基本功能要多少時間?

reertos基本功能包括什么

Vivado環境下如何在IP Integrator中正確使用HLS IP

AMD Vivado IP integrator的基本功能特性

AMD Vivado IP integrator的基本功能特性

評論