本教程在 Ubuntu22.04.1 虛擬機中安裝了 Xilinx 2024.1 的開發環境,基于該環境從源碼編譯 PYNQ 3.1.2 工程,生成能夠在 ALINX AXU15EGB 開發板上運行的 PYNQ 系統鏡像。

Zynq US+ MPSoC AI SFP+ 10G 光纖 FPGA 開發板AXU15EGB

AXU15EGB 開發板:

www.alinx.com/detail/261

資源鏈接:

https://pan.baidu.com/s/1jafq5tUB4O_ojCQFZNzWTA提取碼:73c8

環境配置

提示:

ubuntu、vitis 和 vivado 安裝的部分可以參考 ALINX 的教程文檔《course_s0_Xilinx開發環境安裝教程》,雖然版本不一樣,但流程基本不變;安裝 2024.1 版本的 petalinux 則需要參照本教程,petalinux 的依賴庫和舊版本稍有區別。

ubuntu22.04.1 安裝

1. 在 vmware 中安裝 ubuntu22.04.1,可以使用資源鏈接中提供的 ubuntu-22.04.1-desktop-amd64.iso 鏡像文件,安裝過程比較簡單,使用 vmware 的創建虛擬機流程安裝即可。(vmware 軟件建議使用較新的版本,本教程中使用的是 vmware16)

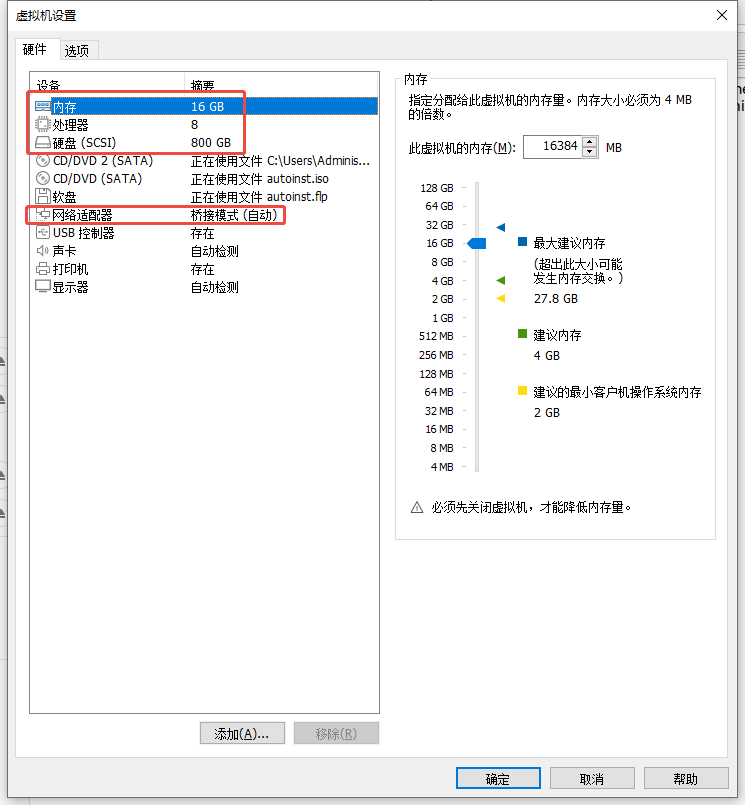

需要注意的是分配給虛擬機的資源,本教程中虛擬機資源配置如圖所示。其中處理器 8 個,分配內存建議至少 16GB,硬盤存儲至少 500GB。主機如果是網線直連,網絡適配器就配置為橋接模式,如果是使用 wifi,就配置為 NAT 模式。(請根據自身主機的配置合理分配資源。主機留給自身的內存太少會導致主機系統卡頓甚至卡死)

進入 ubuntu22.04.1 系統,打開 Software & Updates,切換軟件源為阿里云的軟件源

選擇 Updates,將更新自檢改為 Never,為了保證環境穩定,我們不會更新系統版本。(如果系統主動彈出更新提示的窗口,建議也不要更新,直接關閉窗口)

打開一個命令行終端,輸入命令,選擇“No”,回車確認。這一步是將 ubuntu 默認的 shell 從 dash 改為 bash

sudo dpkg-reconfigure dash

在 ubuntu 的 Settings 中,選擇 Privacy->Screen,將鎖屏時間取消

Petalinux 2024.1安裝

在 ubuntu 中打開一個命令行終端,輸入命令,更新軟件源

sudo apt-get update

輸入命令,安裝 petalinux 的依賴項

sudo apt-get install iproute2 gawk python3 python2 build-essential gcc git make net-tools libncurses5-dev tftpd zlib1g-dev libssl-dev flex bison libselinux1 gnupg wget git-core diffstat chrpath socat xterm autoconf libtool tar unzip texinfo zlib1g-dev gcc-multilib automake zlib1g:i386 screen pax gzip cpio python3-pip python3-pexpect xz-utils debianutils iputils-ping python3-git python3-jinja2 libegl1-mesa libsdl1.2-dev pylint

輸入命令,準備 petalinux 的安裝目錄(注意,這里的 alinx 需要替換成自己的用戶名)

sudo mkdir -p /opt/pkg/petalinux sudo chown alinx:alinx /opt/pkg/petalinux

將資源鏈接提供的 petalinux2024.1 安裝包拷貝到 ubuntu 中,本教程拷貝到 Downloads 目錄下

在 Downloads 目錄下打開終端,輸入如下命令,安裝 petalinux。此時會出現讓你查看協議的提示,按回車查看協議內容,按 q 退出協議內容,按 y 同意協議內容

chmod 755 ./petalinux-v2024.1-05202009-installer.run ./petalinux-v2024.1-05202009-installer.run -d /opt/pkg/petalinux/

安裝完成后,在當前終端輸入命令,測試 petalinux 環境變量配置(注意,環境變量配置只在當前終端中生效,如果打開另一個終端,需要重新配置 petalinux 環境變量)

source /opt/pkg/petalinux/settings.sh

Vivado 和 Vitis 2024.1 安裝

在 ubuntu 中解壓資源鏈接提供的 vitis 的安裝壓縮包

進入解壓后的目錄,打開終端,輸入命令,運行依賴庫檢測腳本

sudo ./installLibs.sh

輸入命令,添加執行權限,運行安裝程序

sudo chmod +x xsetup

安裝完成后,輸入命令,修改安裝目錄的權限

sudo chmod 777 -R /tools/Xilinx/

輸入命令,配置 vivado 環境變量,并打開 vivado(vivado 環境變量配置也僅在當前終端中生效)

source /tools/Xilinx/Vivado/2024.1/settings64.sh vivado&

軟件啟動后,在“Help → Manage license…”中添加 license 文件

輸入命令,安裝下載器驅動

cd /tools/Xilinx/Vivado/2024.1/data/xicom/cable_drivers/lin64/install_script/install_drivers/ sudo ./install_drivers

Vivado 工程參照 ALINX 教程文檔 course_s2_ALINX_ZYNQ_MPSoC 開發平臺 Vitis 應用教程“第一章 體驗 ARM,裸機輸出Hello World”中搭建 vivado 工程的部分,搭建基礎的 ps_hello vivado 工程,ZYNQ Processor IP 配置已在該章節詳述。完善介紹其余部分配置介紹:

啟用 PL Fabric Clocks 勾選,這里預設置四個時鐘頻率。

Slave Interface 配置

在 PS-PL Configuration 窗口,配置 AXI HP, 勾選 AXI HP0 FPD 和 AXI HP1 FPD 設置數據位寬為 128,外連到 AXI_Interconnect_1 的 Master AXI port 以此數據位寬越大越好。

Master Interface 配置

同樣在該窗口勾選 AXI HPM0 LPD 并配置數據位寬為 32

Interrupts 配置

在中斷欄里啟用中斷請求 IRQ0, IRQ1。

其端口位寬自動是 7 也與外連端口自適應,中斷敏感是上升沿。預留終端請求 0,連接 1。

GPIO EMIO 配置

在 I/O 配置欄中勾選 GPIO EMIO, MPSoC 器件最大可選 95。

將 I2C 1 設置成 EMIO 用于連接攝像頭

同樣勾選 UART 1 設置成 emio 類型導出引腳連接 PL 側 UART

ALINX 向廣大用戶提供文檔時也將出廠測試的 Vivado 工程及鏡像。這篇文檔是基于此工程實現,接下來介紹工程實現。

總覽:工程內基于 AXU15EGB 外設接口應用眾多 AMD IP 以及 ALINX IP 實現檢測辦法。

添加 MIPI CSI-2 Rx subsystem 模塊,用于 MIPI 數據的接收和解析,轉成 axi-stream 接口。配置如下,數據格式選擇 YUV422, 選擇 2 lane,Line Rate 配置為 1000Mbps,指的是最大支持的速率,也可以根據自己的需求填寫,范圍為 80-2500;Pixels Per Clock 默認配置為 1,表示 1 個周期為 1 個像素;這里配置為 2。

Shared Logic 選擇“include Shared Logic in core”

Pin Assignment 根據原理圖按照以下配置。

添加 subset 模塊

調整圖像數據順序,因為經過實際操作發現,圖像的 YUV 數據順序需要調整。

添加 Video Processing Subsystem 模塊

Sample Per Clock設置 2,Maximum Data Width:8;Maximum Number of Pixels:1920;Maximum Number of lines: 1080 再選擇Color Space Conversion Only 并勾選 RGB | YUV 4:4:4 | YUV 4:2:2

添加 Video Frame Buffer Write 模塊

這個 IP 類似于 VDMA IP, 將流接口轉成 AXI, 按照如下配置。

添加 AXI_Ethernet 模塊

在 Physical Interface 欄勾選 1Gbps,Physical Interface Selection 選 RGMII

Mac Features 里選擇 4k

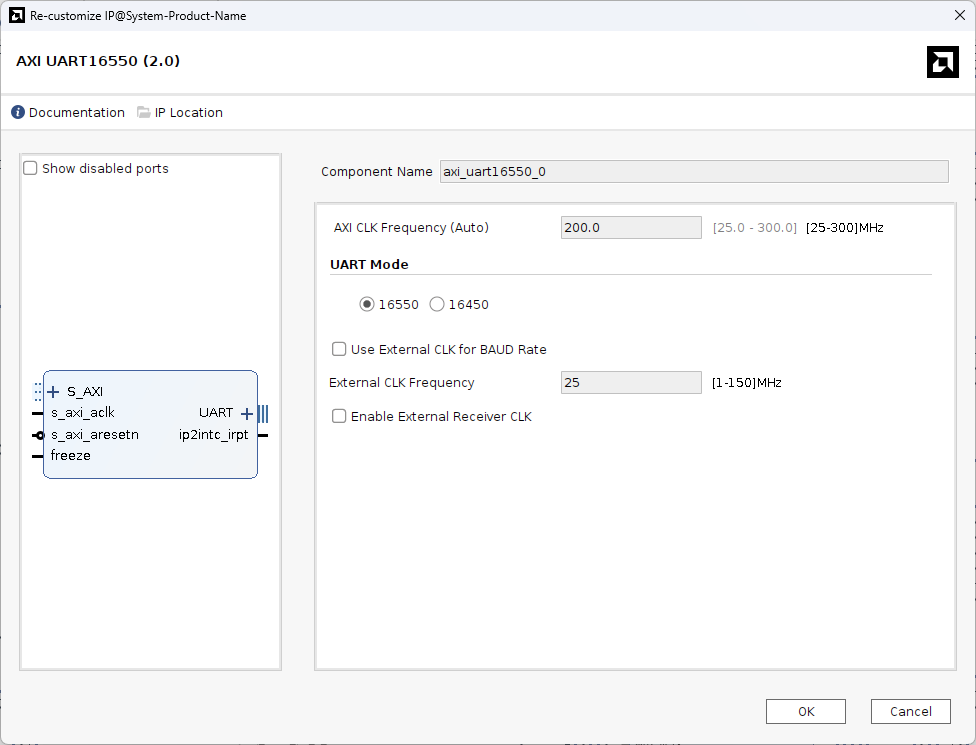

添加兩個 AXI_UART16550 模塊

PL 系統時鐘是 200MHz

導出引腳,外接兩個 RS485 外設。

添加后續幾個 AXI_GPIO 模塊控制 PL 端按鍵和 LED

Extender 模塊是 ALINX 的檢測 FMC 以及 40 pin 擴展口上引腳的代碼模塊,這里的 17 對引腳是 40pin 擴展口上引腳兩兩環通做測試,需要用到 ALINX 內部測試模塊。

最后使用 AXI_Interconnect 模塊將以上 16 個 AXI 模塊連線。

(注意:ps_hello 工程中不涉及到 ps 和 pl 部分交互的接口,例如 hp 口,如果后續要在 pynq 系統中使用這部分接口,需要在這一步就將這些接口使能。移植完成的 pynq 系統中 ps 部分開放的接口和參數都是固定的,雖然基于 pynq 系統,可以任意重新配置 pl 部分,但 pl 能夠和 ps 部分連接的接口在這一步就已經固定了。)

編譯 vivado 工程,因為涉及 PL 側部分導出包含 bit 流的 xsa

petalinux 工程

這部分可參考 ALINX 教程:

《course_s3_ALINX_ZYNQ_MPSoC 開發平臺Linux 基礎教程》“第一章 使用 Petalinux 定制 Linux 系統” 和 “第八章 SD 卡根文件系統”

使用上一章節導出的 xsa 搭建 petalinux 工程

設置離線編譯和 sd 卡根文件系統

在設備樹文件 system-user.dtsi 中修改成如下所示

/include/ "system-conf.dtsi" / { clock_ref_pcie:clk100 { compatible = "fixed-clock"; #clock-cells = ; clock-frequency = ; }; clock_ref_usb0:clk26 { compatible = "fixed-clock"; #clock-cells = ; clock-frequency = ; }; clock_ref_dp:clk27 { compatible = "fixed-clock"; #clock-cells = ; clock-frequency = ; }; }; &psgtr { /* nc, sata, usb3, dp */ clocks = , , ; clock-names = "ref0", "ref1", "ref2"; }; &qspi { status = "okay"; flash0: flash@0 { #address-cells = ; #size-cells = ; compatible ="jedec,spi-nor"; reg= ; partition@0 { label = "qspi-0"; reg = ; }; /delete-node/ partition@1; /delete-node/ partition@2; }; }; /* SD */ &sdhci1 { disable-wp; no-1-8-v; }; /* USB */ &dwc3_0 { status = "okay"; dr_mode = "host"; };

如果要用到 ps 部分的 m.2 接口,測試 ssd 固態硬盤,可以輸入命令打開內核配置界面,在 Device Drivers ---> NVME Support --->路徑下,按 y 使能 nvme 驅動<*> NVM Express block device 后,保存配置并退出

petalinux-config -c kernel

編譯 petalinux 工程,生成 linux 鏡像文件(BOOT.bin、boot.scr、image.ub、rootfs.tar.gz)

制作啟動系統的 sd 卡,連接板卡的 ps 網口、dp 接口。板卡插上 u 盤、ssd 固態硬盤,uart 接口連接到主機,主機上打開串口終端。

板卡上電,串口終端打印啟動信息,啟動信息打印完成會提示輸入用戶名

2024.1 版本的 petalinux 系統默認用戶名是 petalinux,初次登錄會提示設置密碼

測試功能接口

測試 ps 網口:如果網口是連接到支持 dhcp 服務的接口或者路由器,使用 ifconfig 命令可以查看到自動分配的 ip 地址,可以使用 ping 命令實際測試一下

測試 dp 接口:由于沒有配置桌面環境,dp 接口連接到的顯示器會顯示另一個終端界面信息

測試 usb 接口:輸入命令“ dmesg |grep usb ”,可以看到識別到了對應的 usb 設備,如圖可以看到我插入的金士頓的 u 盤設備

測試 m.2 接口:輸入命令“ ls /dev/nvme* ”,如果存在 nvme0,則說明識別到 ssd 設備

確認 petalinux 工程生成的系統 ps 部分的功能正常后,我們需要生成 bsp 包

由于 2024.1 版本的 petalinux 工具存在的一些 bug,似乎會將工作目錄錯誤定位到系統根目錄,該版本直接打包 bsp 會出現如下報錯

一種解決方法是,在 ubuntu 的根目錄下創建一個 build 目錄并添加訪問權限,用于通過 bsp 打包的過程檢測,最終打包文件不受影響

sudo mkdir -p /build sudo chmod 777 /build

sudo mkdir -p /build最后成功打包生成 bsp

pynq 工程

在 home 目錄下打開終端,輸入命令,創建 pynq 的工作目錄

mkdir -p /home/alinx/Projects/pynq

輸入命令,切換到工作目錄,下載 pynq 工程

cd /home/alinx/Projects/pynq git clone https://github.com/Xilinx/PYNQ.git

輸入命令,運行 pynq 的環境配置腳本(該腳本只需要執行一次)

cd /home/alinx/Projects/pynq/PYNQ/sdbuild/scripts ./setup_host.sh

在 /home/alinx/Projects/pynq/PYNQ/boards 目錄下創建一個新目錄 AXU15EGB,用于存放對應開發板的配置文件,將之前 petalinux 工程生成的 petalinux.bsp 文件拷貝到該目錄下

輸入命令,創建并打開一個配置文件 AXU15EGB.spec

touch AXU15EGB.spec gedit AXU15EGB.spec

touch AXU15EGB.spec修改 AXU15EGB.spec 文件內容如下

ARCH_AXU15EGB := aarch64 BSP_AXU15EGB := petalinux.bsp #BITSTREAM_AXU15EGB := base/base.bit FPGA_MANAGER_AXU15EGB := 1 STAGE4_PACKAGES_AXU15EGB := xrt pynq ethernet pynq_peripherals

由于 AXU15EGB 板卡上 mmc0 設備對應的是 emmc,mmc1 對應的是 sd 卡

我們現在需要使用 sd 卡啟動,所以需要將 /PYNQ/sdbuild/boot/meta-pynq/recipes-bsp/device-tree/files/pynq_bootargs.dtsi 文件中的 mmcblk0p2 改為 mmcblk1p2

將資源鏈接提供的三個預編譯文件拷貝到 /PYNQ/sdbuild/prebuilt 目錄下

輸入命令,切換到 sdbuild 目錄,配置 vitis 和 petalinux 的環境變量,編譯 pynq 工程,編譯過程中會有幾次需要輸入用戶密碼。(工程編譯時間較長,編譯時會從 github 上下載一些資源,如果網絡穩定性較差,編譯可能會失敗)

cd /home/alinx/Projects/pynq/PYNQ/sdbuild source /opt/pkg/petalinux/settings.sh source /tools/Xilinx/Vitis/2024.1/settings64.sh make BOARDS=AXU3EGB

如果是網絡問題導致的編譯失敗,比如訪問 github 下載某些資源失敗,可以重新輸入“ make BOARDS=AXU15EGB ”編譯

如果是其他報錯,可以考慮輸入命令“ make clean ”清除編譯結果,然后重新編譯工程

編譯成功后會在 /PYNQ/sdbuild/output 目錄下生成對應板卡型號的 img 鏡像文件

運行測試

將鏡像文件燒寫到 sd 卡

燒寫后的 sd 卡在 ubuntu 中可以看到兩個分區,PYNQ 分區存放啟動鏡像,root 分區存放根文件系統,其中 root 分區由于是 EXT4 格式,在 windows 下一般是看不到的。

在 root 分區的 /usr/local/bin/ 目錄下有一個 resizefs.sh 腳本,這個腳本會在系統初次啟動時被執行,用于將 root 分區擴容到當前存儲設備容量上限

在該目錄下打開終端,輸入命令,以 root 權限編輯文件,將里面的 mmcblk0 修改為 mmcblk1,保存文件并退出

sudo gedit resizefs.sh

開發板接上 dp 接口,ps 網口,uart 接口,插入 sd 卡,上電啟動

此時串口終端會打印啟動信息,完成啟動后會自動登錄(用戶名和密碼都是xilinx)

在串口終端中輸入 ifconfig,確定 ps 網口分配到的 ip 地址,并確保主機和開發板能夠雙向 ping 通

在主機中打開瀏覽器,在網址欄輸入:開發板 ip 地址:9090 ,回車確認。輸入密碼:xilinx,點擊 Log in

此時會遠程連接開發板上運行的 pynq 系統,并進入 jupyter 界面

dma 環通讀寫測試

本節測試用例參考文檔

https://discuss.pynq.io/t/tutorial-pynq-dma-part-1-hardware-design/3133

https://discuss.pynq.io/t/tutorial-pynq-dma-part-2-using-the-dma-from-pynq/3134

搭建 AXU15EGB 的 dma 環通測試 vivado 工程,具體可以參考資源鏈接提供的 dma_test vivado 工程

在 sd 卡 root 分區 /home/xilinx/jupyter_notebooks 目錄下創建一個 testfile 目錄

將 vivado 工程 /dma_test/dma_test.runs/impl_1 目錄下的 design_1_wrapper.bit 文件和 /dma_test/dma_test.gen/sources_1/bd/design_1/hw_handoff 目錄下的 design_1.hwh 文件拷貝到 testfile 目錄下,將 design_1.hwh 文件改名為 design_1_wrapper.hwh,和 bit 文件保持一致

將資源鏈接提供的測試程序 dma_test.ipynb 拷貝到 testfile 目錄下

sd 卡插到板卡中,上電啟動,查看 ip 地址。主機通過瀏覽器遠程登錄 pynq 系統,可以看到我們創建的 testfile 目錄

點擊 testfile 目錄下的 dma_test.ipynb 程序,進入程序編寫和執行界面

鼠標選中第一段程序,然后點擊“運行”,這一段程序的功能是重新加載 bit 流,然后輸出新 bit 流中各 ip 的配置狀況,可以看到 dma 測試工程中的 axi_dma ip 的配置

當第 1 段執行完成,選中框會自動移動到下一段,我們可以多次點擊運行,逐步執行程序

第 2 段是查詢 axi_dma ip 是否存在,如果存在則輸出它的幫助信息

第 3 段創建兩個 dma 收發通道實例

第 4、5、6 段申請一段內存地址 input_buffer,并填充數據

第 7 段開始 dma 傳輸,第 8 段先申請一段內存地址 output_buffer 并打印其中部分數據,第 9、10 段接收 dma 傳輸過來的數據,并打印部分數據,可以看到和發送的數據一致。

資源鏈接

百度網盤:

https://pan.baidu.com/s/1J1KnN_z404Skze42CUj7gQ

提取碼: in8s

-

移植

+關注

關注

1文章

416瀏覽量

29465 -

開發板

+關注

關注

26文章

6321瀏覽量

118983 -

Zynq

+關注

關注

10文章

630瀏覽量

49494

發布評論請先 登錄

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

Ti推出面向Zynq UltraScale+ MPSoC的電源參考設計

基于Zynq UltraScale+ MPSoC上運行 Xen 管理程序

Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞

Zynq UltraScale+ MPSoC的發售消息

米爾科技Zynq UltraScale+ MPSoC技術參考手冊介紹

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

米爾電子zynq ultrascale+ mpsoc底板外設資源清單分享

ZYNQ Ultrascale+ MPSoC系列FPGA芯片設計

Zynq UltraScale+ MPSoC中的隔離方法

Zynq UltraScale+ MPSoC的隔離設計示例

Zynq UltraScale+ MPSoC驗證數據手冊

ALINX教程分享_Zynq UltraScale+ MPSoC PYNQ3.1.2移植

ALINX教程分享_Zynq UltraScale+ MPSoC PYNQ3.1.2移植

評論