電子發燒友網報道(文/吳子鵬)根據相關媒體報道,臺積電拒絕為三星Exynos處理器提供代工服務,理由是臺積電害怕通過最先進的工藝代工三星Exynos處理器可能會導致泄密,讓三星了解如何提升最先進制程工藝的良率,而這恰恰是三星在先進制程方面的最大痛點。

據悉,三星System LSI部門已經改變了此前晶圓代工獨自研發的發展路線,轉而尋求外部聯盟合作,不過縱觀全球晶圓代工產業,只有臺積電、三星和英特爾三家企業具有尖端制程工藝代工的能力。而要發展最先進的3nm和2nm工藝,對于三星來說,可選的伙伴只有臺積電。然而,X平臺用戶@Jukanlosreve透露,臺積電不會與三星達成任何形式的合作以大規模生產Exynos系列處理器。臺積電并不擔心錯失Exynos訂單,該公司可以憑借其及時交貨的優勢收取溢價費用。

不過,從三星System LSI部門的動作來看,該公司并沒有將寶都押在純晶圓代工領域,而是將先進封裝的權重大幅提升,作為該公司在高性能芯片制造領域突圍的關鍵。

三星晶圓代工繞不過良率低這道坎

根據臺灣供應鏈人士透露,目前臺積電在2nm上進展非常順利,良率已經達到了60%。N2平臺能夠帶來效能提升15%,功耗降低30%。臺積電研發和先進技術副總裁Geoffrey Yeap表示,N2是臺積電“四年多的勞動成果”,首次采用新型全環繞柵極(GAA)納米片晶體管,目前主要客戶已經完成2nm IP設計并開始驗證,臺積電還開發出低阻值重置導線層、超高效能金屬層間電容,以此對2nm制程工藝的能效進行提升。臺積電2nm工藝預計2025年實現量產。

和臺積電相比,三星在先進制程方面的進展就沒那么順利了。在當前最前沿的3nm工藝節點上,臺積電的良率已經超過了80%,而三星最開始設定的首代和第二代3nm GAA技術的良率目標是70%。然而,根據目前的記錄,三星第二代改良版3nm工藝平臺的良率只有20%。

盡管面臨挑戰,三星并未放棄,他們一方面在改善3nm工藝,另一方面也在推進2nm工藝的研發。據悉,三星計劃在2027年推出代號為Ulysses(尤利西斯)的2nm工藝Exynos處理器,該處理器將用于Galaxy S27系列。

不過,如果良率問題持續無法得到解決,三星在代工和芯片上的計劃都可能擱淺,搭載非高通芯片的三星旗艦機可能成為歷史。

三星選擇提升先進封裝權重

根據韓媒此前的報道,三星正計劃“洗牌”先進半導體封裝供應鏈,將從根本上重新評估材料、零部件和設備,影響開發到采購各個環節,從而進一步增強技術競爭力。據悉,三星優先關注設備,跳出現有合作關系的限制,準備在“性能”優先的原則下,重新選擇供應商。據悉,三星甚至考慮退回已采購的設備,重新評估其是否符合新的標準。

在先進封裝領域,三星的策略開始由“一對一”聯合開發計劃(JDP)模式轉為“一對多”的 JDP 模式,即同時與多家供應商合作開發,以尋求更先進的技術和設備,預計該計劃最早將于2025年實施。

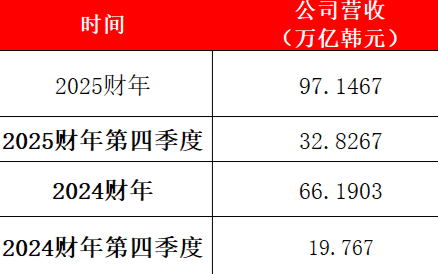

在去年的年度股東大會上,三星聯席首席執行官慶桂顯表示,三星電子在先進封裝產業的投資成果將從2024年下半年開始真正顯現。2024年三星大舉進軍先進封裝領域,預計2024年先進封裝能夠為三星帶來1億美元的營收。

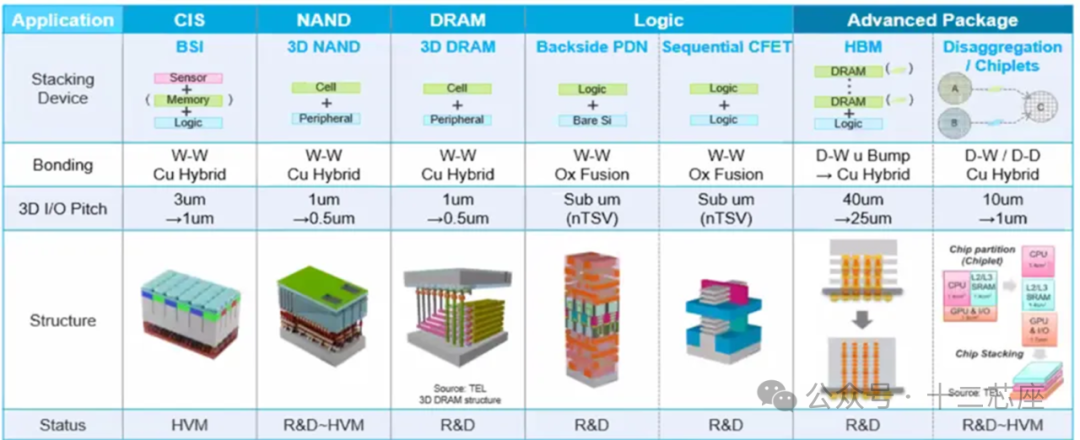

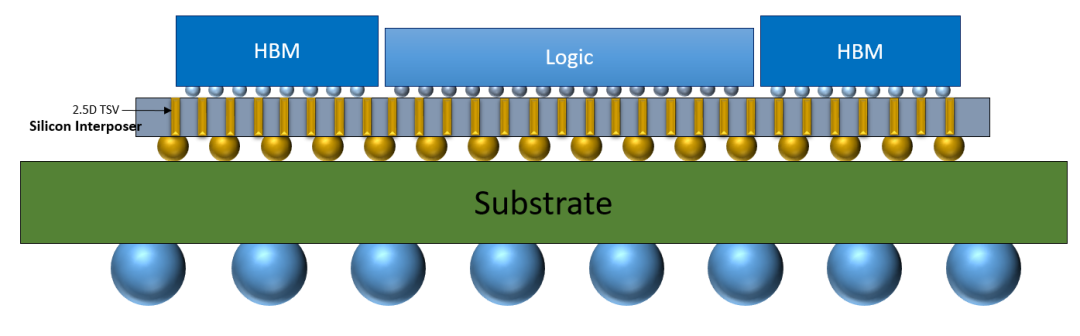

目前,三星在先進封裝方面有很多代表性技術,比如I-Cube 2.5D封裝、X-Cube 3D IC和玻璃基板等。其中,三星I-Cube 2.5D封裝通過并行水平芯片放置防止熱量積存并擴展性能。三星以硅通孔(TSV)和后道工序(BEOL)為技術基石,整合兩個以上的(不同)芯片,使之完美協作,讓系統發揮1+1 > 2的功能。

I-Cube 2.5D封裝包括I-Cube S、I-Cube E和H-Cube 三種產品形態。I-Cube SI-CUBE S 是一種異構技術,將一塊邏輯芯片與一組高帶寬存儲器 (HBM) 裸片水平放置在一個硅中介層上,兼具高帶寬和高性能的優勢,即使在大中介層下,仍具有出色的翹曲控制能力;I-Cube E 技術采用硅嵌入結構,不僅具有硅橋的精細成像優勢,也同時擁有PLP的技術特點:大尺寸、無硅通孔 (TSV) 結構的RDL 中介層;H-Cube 是一種混合基底結構,將精細成像的 ABF(Ajinomoto Build-up Film)基底和 HDI(高密度互連)基底技術相結合,可在 I-Cube 2.5D 封裝中實現較大的封裝尺寸。

三星3D IC封裝通過垂直堆疊的方式大幅地節省了芯片上的空間,主要包括X-Cube(微凸塊)和X-Cube(銅混合鍵合)兩種形態,前者通過增加每個堆棧的芯片密度,進一步提升 X-CUBE 的速度或性能;后者與傳統的芯片堆疊技術相比,具有極大的布局靈活性優勢。

除了在架構上創新,在材料上三星也在關注玻璃基板。此前有消息人士稱,三星計劃于2026年大規模量產玻璃基板先進封裝。該公司正在悄然布局用于FOPLP(面板級封裝)工藝的半導體玻璃基板,相較于塑料基板,玻璃基板以其優異的導熱性和穩定性,具有成本低、電學性能優越以及低翹曲率等優勢,被視為下一代封裝材料的理想選擇。不過,玻璃基板也面臨著高精度通孔、高質量金屬填充、高密度布線和鍵合技術等方面的技術挑戰,如果不能妥善解決,也會演變成為先進封裝的良率缺陷。

結語

從目前的情況來看,三星在先進制程方面已經深陷低良率的漩渦,且沒有什么有效的應對手段,這導致三星的巨額投資無法變現。目前,尋求外部合作的三星,實際上可選對象只有臺積電,但臺積電很顯然不會參與這項風險奇高的商務合作。在后續發展上,三星在先進封裝方面的布局有可能成為重點,成為Chiplet技術發展的重要力量,畢竟三星除了有制造、封裝,該公司的HBM技術也處于全球第一梯隊。

-

芯片

+關注

關注

463文章

54098瀏覽量

467303 -

臺積電

+關注

關注

44文章

5804瀏覽量

176703 -

三星

+關注

關注

1文章

1770瀏覽量

34309

發布評論請先 登錄

被臺積電拒絕代工,三星芯片制造突圍的關鍵在先進封裝?

被臺積電拒絕代工,三星芯片制造突圍的關鍵在先進封裝?

評論