當前,半導體行業正在將 3.5D 作為先進封裝的下一個最佳選擇,這是一種混合方法,包括堆疊邏輯芯片并將它們分別粘合到其他組件共享的基板上。

這種封裝模型既滿足了大幅提升性能的需求,又避開了異構集成中一些最棘手的問題。它在數據中心內已經廣泛使用的2.5D和芯片行業近十年來一直在努力實現商業化的全3D-IC之間建立了一個中間地帶。

3.5D 架構有幾個主要優勢:

它創造了足夠的物理分離來有效解決散熱和噪音問題。

它提供了一種在高速設計中添加更多 SRAM 的方法。自 20 世紀 60 年代中期以來,SRAM 一直是處理器緩存的首選,并且仍然是加快處理速度的必要元素。但 SRAM 不再以與數字晶體管相同的速率擴展,因此它在每個新節點上占用更多的空間(以百分比計算)。而且由于光罩的尺寸是固定的,因此最好的選擇是通過垂直堆疊芯片來增加面積。

通過減小處理元件和內存之間的接口,3.5D 方法還可以縮短信號需要傳輸的距離,并大大提高處理速度,遠遠超過平面實現。這對于大型語言模型和 AI/ML 至關重要,因為這些領域需要快速處理的數據量正在激增。

芯片制造商仍然認為,完全集成的 3D-IC 是平面 SoC 的最佳替代品,但將所有東西都打包成 3D 配置使得處理物理效應變得更加困難。散熱可能是最難解決的問題。工作負載可能會有很大差異,從而產生動態熱梯度并將熱量困在意想不到的地方,從而縮短芯片的使用壽命和可靠性。除此之外,在每個新節點上,電源和基板噪聲都會變得更加成問題,電磁干擾問題也是如此。

Ansys產品營銷總監Marc Swinnen表示:“市場首先采用的是高性能芯片,這些芯片會產生大量熱量。他們選擇了昂貴的冷卻系統,配備了大量風扇和散熱器,并且選擇了硅中介層,這可以說是連接芯片的最昂貴的技術之一。但它也能提供最高的性能,并且非常適合散熱,因為它與熱膨脹系數相匹配。散熱是它成功的一大原因。除此之外,你可能想要更大的系統,里面有更多東西,而這些東西是無法放在一塊芯片上的。這只是一個光罩尺寸的限制。另一個是異構集成,你需要多個不同的工藝,比如 RF 工藝或 I/O,而這些工藝不必在 5nm 范圍內。”

3.5D 封裝還提供了更大的靈活性來添加額外的處理器內核,并且由于可以單獨制造和測試已知良好的芯片,因此可以實現更高的產量,這是Xilinx于 2011 年在 28nm 工藝上率先提出的概念。

3.5D 是所有這些方法的松散融合。它可以包括兩到三個堆疊在一起的芯片,甚至可以包括水平排列的多個芯片。

“它的垂直方向受到限制,這不僅僅是因為散熱原因,” ASE 集團研究員兼高級技術顧問Bill Chen表示。“這也是出于性能原因。但散熱是限制因素,我們已經討論過許多不同的材料來幫助解決這個問題——金剛石和石墨烯——但這個限制仍然存在。”

這就是為什么最有可能的組合(至少在最初階段)是將處理器堆疊在SRAM上,從而簡化冷卻。不同處理元件的高利用率產生的熱量可以通過散熱器或液體冷卻去除。而且,使用一個或多個變薄的基板,信號將傳播更短的距離,從而使用更少的功率在處理器和內存之間來回移動數據。

“最有可能的是,這將是邏輯過程上的內存邏輯,”Arm硅操作工程研究員兼高級總監 Javier DeLaCruz 表示。“這些通常都包含在 SoC 中,但其中一部分將是 SRAM,而 SRAM 在節點之間的擴展性不是很好。因此,在內存和邏輯過程中使用邏輯才是真正的制勝解決方案,這是 3D 更好的用例之一,因為這才是真正縮短連接性的原因。處理器通常不會與另一個處理器通信。它們通過內存相互通信,因此將內存放在不同的樓層,并且它們之間沒有延遲是非常有吸引力的。”

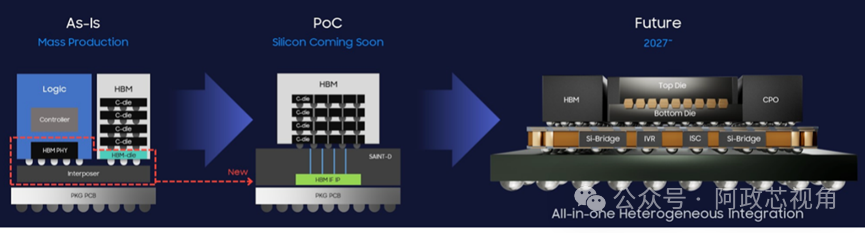

SRAM 不一定必須與處理器的先進節點處于同一節點,這也有助于提高產量和可靠性。在最近的三星代工活動中,該公司代工業務開發副總裁 Taejoong Song 展示了 3.5D 配置的路線圖,明年將使用 2nm 芯片堆疊在 4nm 芯片上,2027 年將使用 1.4nm 芯片堆疊在 2nm 芯片上。

圖 1:三星的異構集成路線圖,顯示堆疊式 DRAM(HBM)、小芯片和共封裝光學器件。資料來源:三星代工廠

英特爾代工廠的方法在很多方面都很相似。英特爾高級副總裁兼代工服務總經理 Kevin O'Buckley 表示:“我們的 3.5D 技術是在帶有硅橋的基板上實現的。這不是成本極高、產量低、多掩模版形狀的硅,甚至不是 RDL。我們以更具成本效益的方式使用薄硅片,通過硅橋實現芯片到芯片的連接,甚至是堆疊芯片到芯片的連接。因此,您可以獲得相同的硅密度優勢,以及該硅橋的相同 SI(信號完整性)性能,而無需在整個硅橋下方放置巨大的單片中介層,這既成本高昂又限制了容量。它正在發揮作用。它正在實驗室中運行。”

圖 2:英特爾的 3.5D 模型。來源:英特爾

這里的策略部分是進化的——3.5D 至少已經進行了幾年的研發——部分是革命性的,因為減薄互連層、找出處理這些更薄互連層的方法以及如何粘合它們仍在進行中。可能會出現翹曲、開裂或其他潛在缺陷,并且動態配置數據路徑以最大化吞吐量是一項持續的挑戰。但在兩芯片和三芯片堆棧的熱管理方面已經取得了重大進展。

“將會有多種解決方案,”ASE 公司研發副總裁 CP Hung 表示。“例如,除了設備本身和外部散熱器之外,許多人還會添加浸入式冷卻或局部液體冷卻。因此對于封裝,您可能還會看到蒸汽室的實現,這將為設備本身和外部散熱器之間添加一個良好的接口。面對所有這些挑戰,我們還需要針對不同的間距。例如,如今您可以看到批量生產的間距為 45 到 40。這是一種典型的凸塊解決方案。我們預計行業將轉向 25 到 20 微米的凸塊間距。然后,為了更進一步,我們需要混合鍵合,即小于 10 微米的間距。”

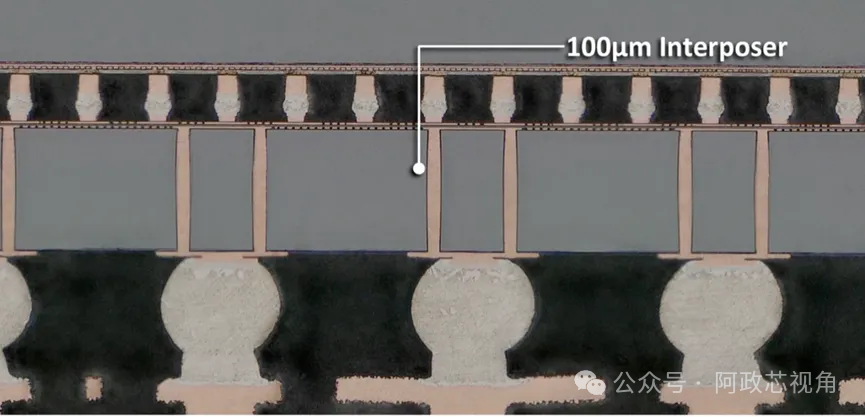

圖 3:當今的中介層支持間距為 45m 的 100,000 多個 I/O。來源:ASE

混合鍵合解決了另一個棘手的問題,即數千個微凸塊之間的共面性。“人們開始意識到,我們互連的密度需要一定的平整度,而制造傳統鍵合產品的人很難以合理的產量滿足這一要求,”Promex Industries首席運營官 David Fromm說。“這使得制造它們變得困難,人們的想法是,‘所以也許我們必須做點別的。’你開始看到其中的一些。”

-

封裝

+關注

關注

128文章

9249瀏覽量

148615 -

邏輯芯片

+關注

關注

1文章

167瀏覽量

32158

原文標題:3.5D封裝,來了!(上)

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

先進封裝成破局,博通率先落地3.5D,6000mm2超大集成

2D、2.5D與3D封裝技術的區別與應用解析

淺談2D封裝,2.5D封裝,3D封裝各有什么區別?

從 2D 到 3.5D 封裝演進中焊材的應用與發展

0.1-3.5 GHz SP3T 開關 skyworksinc

3.5 A 恒定導通時間降壓 DC-DC 轉換器 skyworksinc

S32DS v3.5安裝S32k3開發包失敗的原因?

2.5D封裝為何成為AI芯片的“寵兒”?

3.5D封裝來了(上)

3.5D封裝來了(上)

評論