繼續講解!內容越來越深了哦!沒想到時隔三年之后又寫出這么多文章,內容來源于教學和實踐,真正的實現教學相長!希望能有更多的讀者能給我留言,督促我不斷進步。再次看一下PPT中的理論。本文適合搞通信仿真的專業人士閱讀學習,非此領域的人慎入,畢竟知識點的難度擺在這里,很多概念的理解需要仿真基礎。

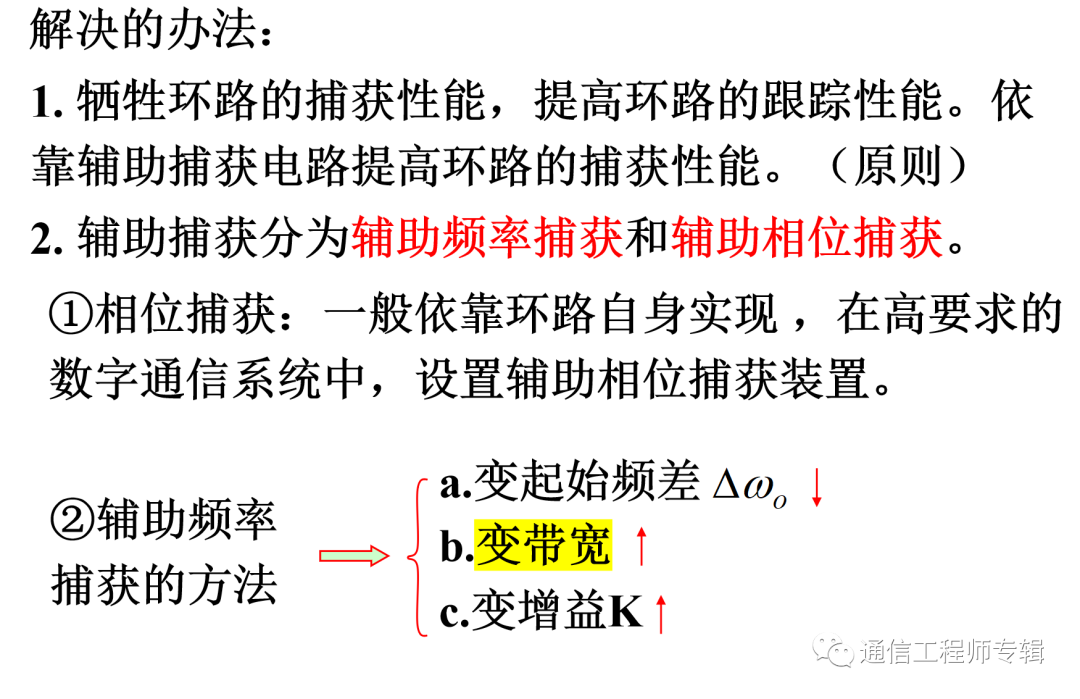

什么是輔助捕獲?怎么實現?這個概念在實際產品中一直被使用。在進入環路前,我們會通過其他算法將信號的載波頻率進行粗估計,然后將估計結果預先置給環路中的 VCO,這樣就可以減少環路的輸入和本地輸出的偏差,以便快速入鎖。后續有系列專門講信號的捕獲知識。這里主要看看變帶寬方式的仿真程序如何寫?當年本人獨立研究此方面內容,沒有人可以請教或者交流,學起來非常痛苦。現在我在網上發表了這類文章,不僅包含了理論知識,也飽含了經驗。因此希望大家能夠認真的學習消化,肯定會收獲頗豐。

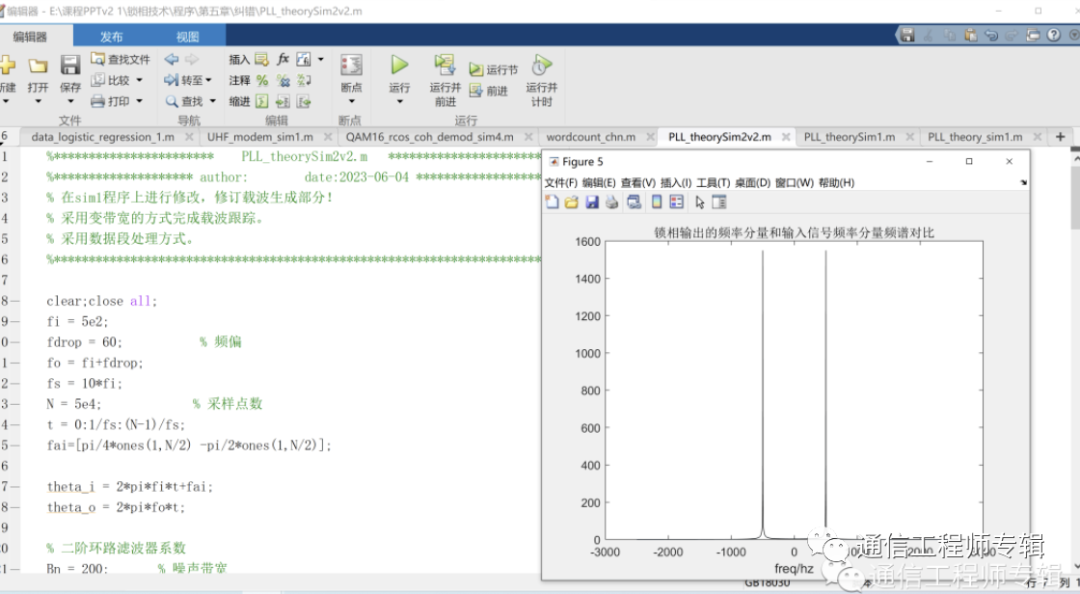

先來看程序,在固定位置進行帶寬變動。注意程序的重大改動。在此程序中將之前的數據流處理方式改為了數據段處理方式,在大頻偏下也跟蹤正確了,之前的流處理方式只能在小頻偏環境下跟蹤正確。那這就需要我們后續好好解析這兩種寫法背后的物理意義。這個現象在我讀研期間寫算法的時候就遇到過。沒想到多年以后把這塊。忽略了。因此,在幫助讀者改程序的時候也遇到了。同樣的困惑。好在。對之前存檔的程序進行了剖析以后。在此。讓我回想起這個問題。因此非常有必要在本文里面進行詳細地解釋和分析。

原文標題:大學畢業設計一席談v2之十六 鎖相環(13)變帶寬跟蹤

文章出處:【微信公眾號:通信工程師專輯】歡迎添加關注!文章轉載請注明出處。

-

通信網絡

+關注

關注

22文章

2105瀏覽量

54383

原文標題:大學畢業設計一席談v2之十六 鎖相環(13)?變帶寬跟蹤

文章出處:【微信號:gh_30373fc74387,微信公眾號:通信工程師專輯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Altera公司鎖相環IP核介紹

探索CDC516:高性能3.3V鎖相環時鐘驅動器

CDC2516:高性能鎖相環時鐘驅動器的深度解析

CDC509:高性能3.3V鎖相環時鐘驅動器

CDCVF2505 3.3 - V 時鐘鎖相環時鐘驅動器:設計與應用指南

CDCVF25081:高性能鎖相環時鐘驅動器深度解析

TLC2932A高性能鎖相環芯片詳解:設計與應用指南

探索TLC2933A高性能鎖相環:特性、應用與設計要點

?CDCVF2510 3.3V鎖相環時鐘驅動器技術文檔總結

?CDCVF2509 3.3V鎖相環時鐘驅動器技術文檔總結

?CDCVF25081 3.3-V 鎖相環時鐘驅動器技術文檔總結

?CDCVF2510A 3.3V鎖相環時鐘驅動器技術文檔總結

基于鎖相環的無軸承同步磁阻電機無速度傳感器檢測技術

高壓放大器在鎖相環穩定重復頻率研究中的應用

大學畢業設計一席談v2之十六 鎖相環(13)?變帶寬跟蹤

大學畢業設計一席談v2之十六 鎖相環(13)?變帶寬跟蹤

評論