繼續講解!通過最近兩篇文章的程序就可以來驗證下圖中的文字!這也是經驗獲取的過程!那我的經驗又是怎么獲取的呢?主要是靠看大量的論文和書籍。在我們那個年代,互聯網已經開始展現出它的魅力。我從互聯網上下載了很多論文。現在的時代不一樣了,不僅有文章,還會有視頻講解課程。我相信這些內容會對大家的學習有更大的幫助。

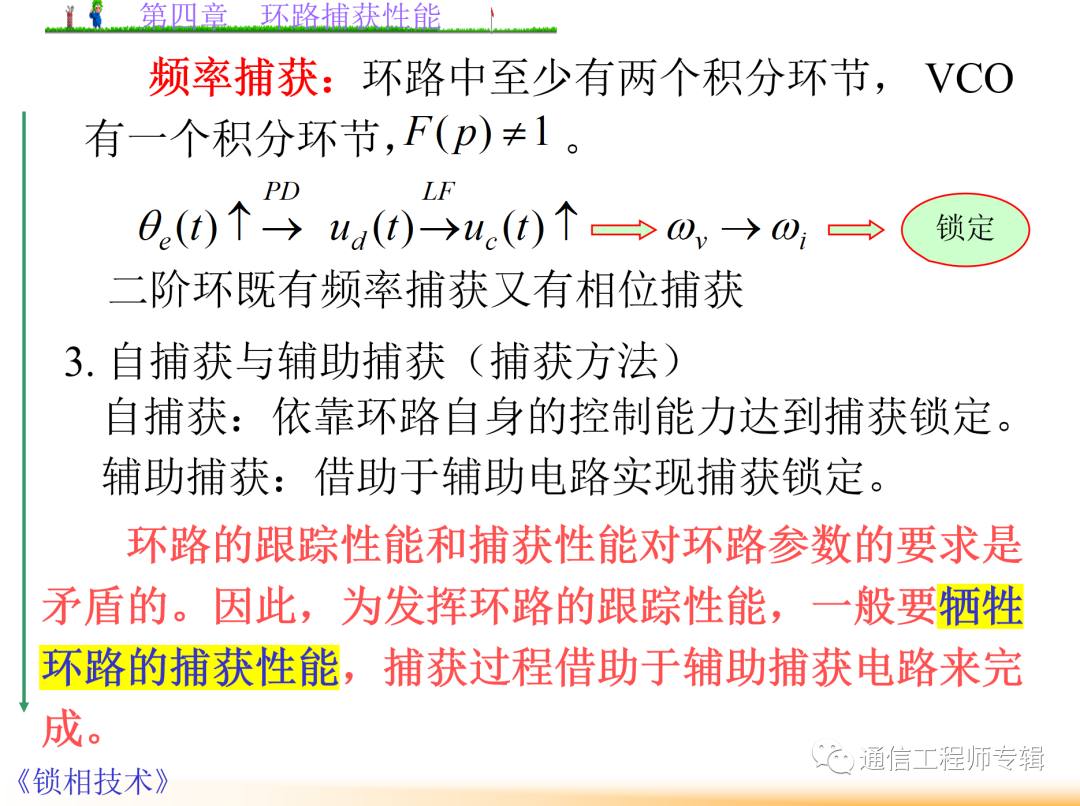

怎么理解犧牲環路的捕獲性能!

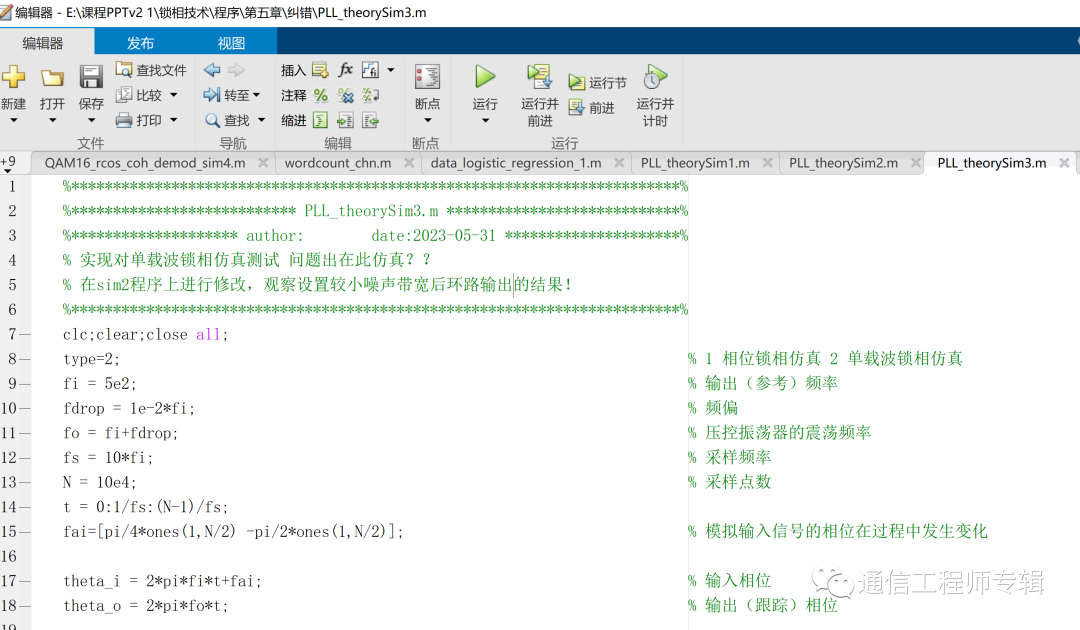

這就是環路中噪聲帶寬設置的折衷。設置的值大了,捕獲帶增加,捕獲速度加快。但跟蹤時殘留的噪聲大,不穩定性也增加。下面用仿真程序來說明這個概念!

% 二階環路濾波系數

原文標題:大學畢業設計一席談v2之十六 鎖相環(12)代碼分析加經驗總結

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

通信網絡

+關注

關注

22文章

2105瀏覽量

54379

原文標題:大學畢業設計一席談v2之十六 鎖相環(12)?代碼分析加經驗總結

文章出處:【微信號:gh_30373fc74387,微信公眾號:通信工程師專輯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

Altera公司鎖相環IP核介紹

鎖相環(PLL,Phase Lock Loop)的主要作用是實現輸出時鐘對輸入參考時鐘的相位與頻率的精確跟蹤和同步。鎖相環(PLL)的主要模塊包括相位頻率檢測器(PFD)、電荷泵、環路濾波器

探索CDC516:高性能3.3V鎖相環時鐘驅動器

探索CDC516:高性能3.3V鎖相環時鐘驅動器 在電子設計領域,時鐘驅動器對于確保系統的穩定運行至關重要。今天我們要深入探討的是德州儀器(Texas Instruments)的CDC516,一

CDC2516:高性能鎖相環時鐘驅動器的深度解析

: cdc2516.pdf 一、CDC2516概述 CDC2516是一款高性能、低偏斜、低抖動的鎖相環(PLL)時鐘驅動器,專為同步DRAM應用而設計。它工作在3.3V的VCC電壓下,

CDC509:高性能3.3V鎖相環時鐘驅動器

CDC509:高性能3.3V鎖相環時鐘驅動器 在電子設計領域,時鐘驅動是一項關鍵技術,尤其是在同步DRAM應用中,需要高精度、低抖動的時鐘信號來確保數據的準確傳輸。德州儀器(Texas

CDCVF2505 3.3 - V 時鐘鎖相環時鐘驅動器:設計與應用指南

的 CDCVF2505 3.3 - V 時鐘鎖相環時鐘驅動器,看看它在同步 DRAM 和通用應用中能發揮怎樣的作用。 文件下載: cdcvf2505.pdf 一、產品特性亮點 寬頻率范圍與低抖動

CDCVF25081:高性能鎖相環時鐘驅動器深度解析

,一款高性能、低偏斜、低抖動的鎖相環(PLL)時鐘驅動器。 文件下載: cdcvf25081.pdf 一、產品特性亮點 1. 架構與輸出 CDCVF25081基于鎖相環技術,是零延遲緩

TLC2932A高性能鎖相環芯片詳解:設計與應用指南

TLC2932A高性能鎖相環芯片詳解:設計與應用指南 在電子設計領域,鎖相環(PLL)是一種至關重要的電路,它能夠實現信號的相位同步和頻率合成,廣泛應用于通信、雷達、儀器儀表等眾多領域。今天要給大家

探索TLC2933A高性能鎖相環:特性、應用與設計要點

,了解其特性、工作原理及應用中的設計要點。 文件下載: tlc2933a.pdf 一、TLC2933A概述 TLC2933A專為鎖相環系統設計,主要由電壓控制振蕩器(VCO)和邊緣觸發型相位頻率檢測器

?CDCVF2510 3.3V鎖相環時鐘驅動器技術文檔總結

該CDCVF2510是一款高性能、低偏斜、低抖動、鎖相環 (PLL) 時鐘驅動器。它使用鎖相環 (PLL) 將反饋 (FBOUT) 輸出與時鐘 (CLK) 輸入信號在頻率和相位上精確對齊。它專為

?CDCVF2509 3.3V鎖相環時鐘驅動器技術文檔總結

該CDCVF2509是一款高性能、低偏斜、低抖動、鎖相環 (PLL) 時鐘驅動器。該器件使用 PLL 將反饋 (FBOUT) 輸出與時鐘 (CLK) 輸入信號在頻率和相位上精確對齊。該器件專為與同步

?CDCVF25081 3.3-V 鎖相環時鐘驅動器技術文檔總結

CDCVF25081是一款高性能、低偏斜、低抖動、鎖相環時鐘驅動器。它使用 PLL 將輸出時鐘在頻率和相位上精確對齊輸入時鐘信號。輸出分為 2 個組,總共 8 個緩沖 CLKIN 輸出。當不存在 CLKIN 信號時,該器件會自動

?CDCVF2510A 3.3V鎖相環時鐘驅動器技術文檔總結

該CDCVF2510A是一款高性能、低偏斜、低抖動、鎖相環 (PLL) 時鐘驅動器。該CDCVF2510A使用鎖相環 (PLL) 將反饋 (FBOUT) 輸出在頻率和相位上精確對齊到時鐘 (CLK

高壓放大器在鎖相環穩定重復頻率研究中的應用

實驗名稱: 鎖相環穩定重復頻率的系統分析 實驗內容: 針對重復頻率的漂移,引入兩套鎖相環系統反饋控制兩個激光器的重復頻率,將其鎖定在同一個穩定的時鐘源上。本章主要闡述了經典

鎖相環(PLL)電路設計與應用(全9章)

內容介紹本文檔主要介紹鎖相環(PLL)電路的設計與應用,內容包括PLL工作原理與電路構成、PLL電路的傳輸特性、PLL電路中環路濾波器的設計方法、PLL電路的測試與評價方法、PLL特性改善技術

發表于 04-18 15:34

大學畢業設計一席談v2之十六 鎖相環(12)?代碼分析加經驗總結

大學畢業設計一席談v2之十六 鎖相環(12)?代碼分析加經驗總結

評論