這個系列的文章之前改了一版,第二版共計有十篇文章,今天續寫第十一篇文章,相隔超過了三年!!!為什么又開始續寫了呢?因為我的一個朋友突然發來求助信息,他寫的程序一直沒有調好,我正好借幫他調試程序的機會給大家展示調試過程。這個過程一定要展示給大家,因為這是絕好的學習過程。有實例講解的文章自然能讓大家深透的掌握鎖相理論。分析錯誤糾正錯誤的過程能獲取很多經驗值,請各位珍惜。本系列課程非常經典,望想學物理層算法的同學好好珍惜和消化!

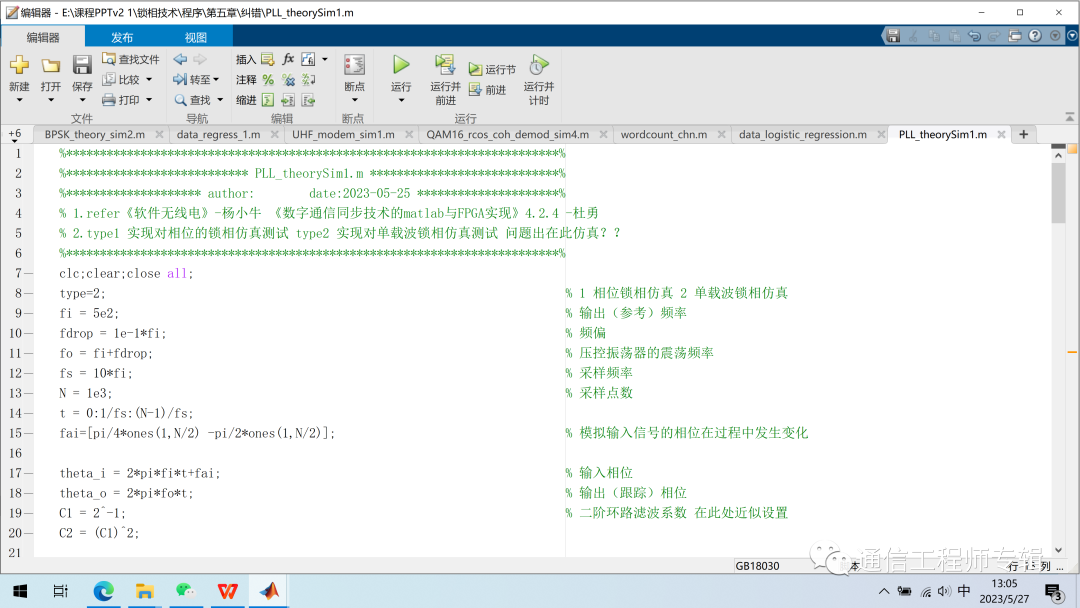

先看他寫的代碼,我也需要時間來吃透程序的過程。這個過程需要細致的閱讀,不能少了這一步。大家以后到了工作崗位接到消化項目代碼的時候,記住務必細致,吃透思路。

本文標題依舊是第十篇,會將之前的內容合并到本文。為何不寫成第十一篇了呢?因為菜單快寫滿了,因此,只能不斷的合并文章內容,減少不必要的篇幅增加。本文內容超過三千字,主要是因為代碼內容太多了,請耐心看完。先來回顧之前第十篇文章的內容,提及了AFC環路。

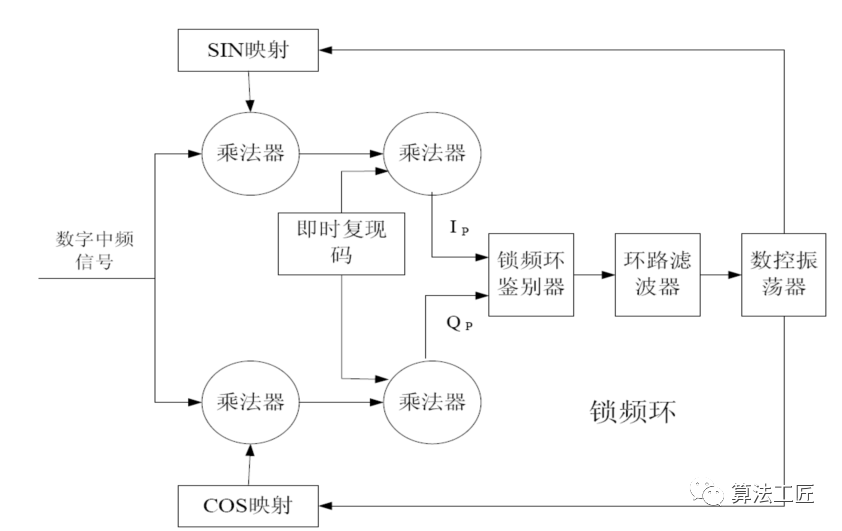

衛星導航接收機中采用鎖頻環的目的是為了將載波頻率偏差牽引到鎖相環能夠捕獲的范圍,使得鎖相環可以實現相干解調,得到導航電文。因此鎖頻環是通過復現近似的頻率以完成載波剝離過程,所以也被稱為自動頻率控制(AFC)環。

鎖頻環(FLL)的結構!

頻率跟蹤實質上是載波相位的差分跟蹤。一般情況下,頻率跟蹤鑒相器的作用是測量載波相位在固定時間間隔內的變化量。頻率鎖相環通過數控振蕩器(NCO)產生適當的本地載波以解調信號,在信號初始捕獲完成后實現頻率鎖定比實現相位鎖定容易。鑒頻器常采用叉積鑒頻算法。講到這里,大家應該對環路的知識有所了解了吧!!!此時應該去回顧上一節課的程序了!

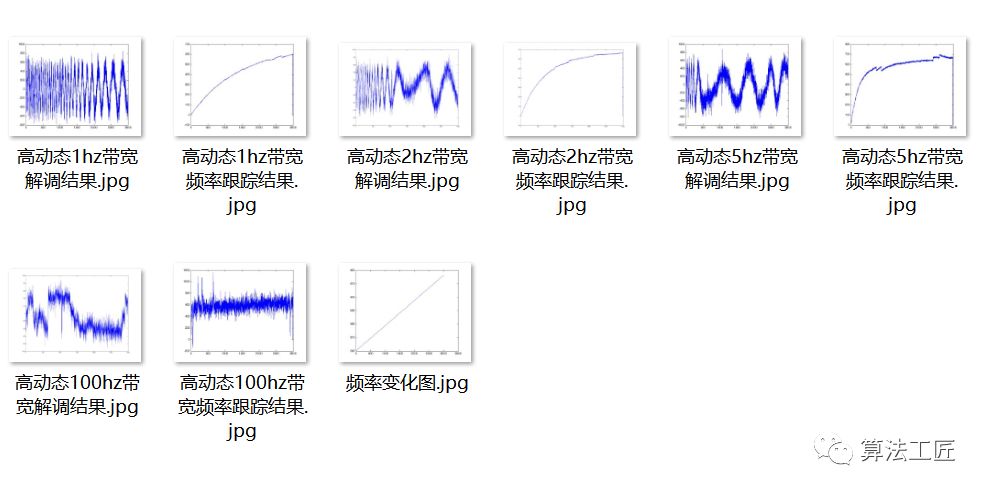

希望大家能夠在高動態環境下測試一下AFC的性能!

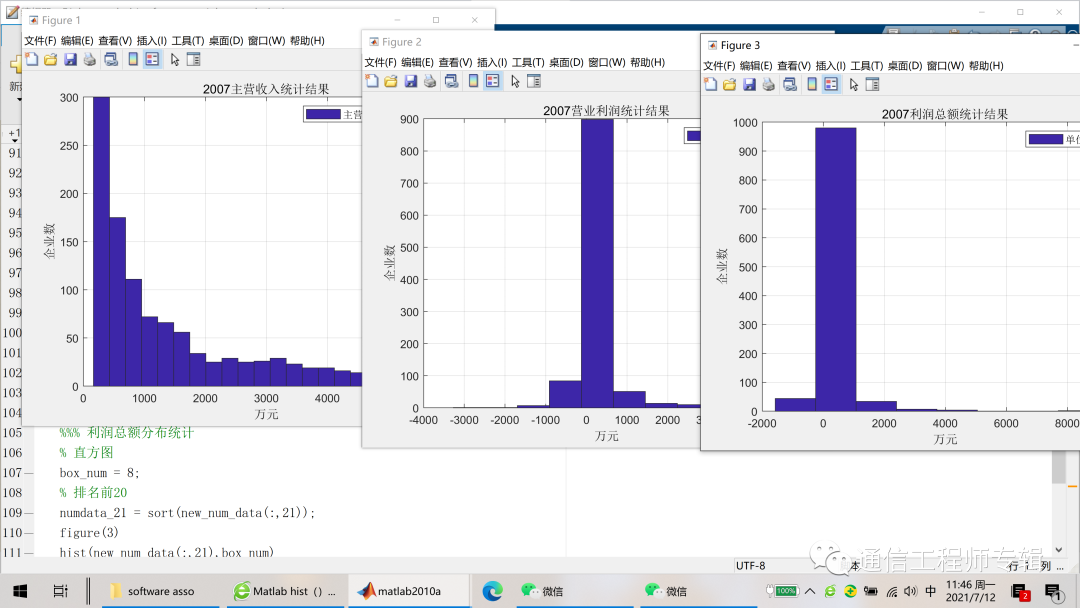

無實踐,無工科!請多用圖表來表示仿真結果,首先可以讓讀者一目了然的清楚仿真的結果,二來方便我們以后調用!寫論文的時候不至于找不到圖來證明程序的正確性!為什么會講這些內容呢?看看百度搜索后的結果。

看看網上的搜索結果就知道學習鎖頻環的原因了!

隨著國防技術的飛速發展,要求導彈等經常工作在高動態環境下武器的性能不斷改進。傳統的導彈制導手段不能滿足現代戰爭對導彈提出的高精度、高可靠性。那么靠什么制導呢?衛星導航了!最近幾年,國家的航天技術突飛猛進!背后是無數科技人員的辛苦!

2020年3月9日19時55分,我國在西昌衛星發射中心用長征三號乙運載火箭,成功發射北斗系統第五十四顆導航衛星。衛星順利進入預定軌道,后續將進行變軌、在軌測試、試驗評估,適時入網提供服務。

2021年4月24日,2021中國航天日開幕啟動儀式在江蘇南京舉行。中國首輛火星車命名為“祝融號”。5月17日,祝融號火星車首次通過環繞器傳回遙測數據。5月22日10時40分,“祝融號”火星車已安全駛離著陸平臺,到達火星表面,開始巡視探測。

2021年4月29日11時,長征五號B遙二運載火箭搭載空間站天和核心艙,在海南文昌航天發射場發射升空。2021年6月17日18時48分,航天員聶海勝、劉伯明、湯洪波先后進入天和核心艙,標志著中國人首次進入自己的空間站。

這些項目都值得國人自豪,用的是自主開發的技術!同學們,加油!國家需要你們!為國家科技進步不斷努力吧!后續鎖相環應用于各種調制方式下的知識將在后續的相干解調章節中。畢竟傳統的相干解調大多數是采用鎖相環來完成載波恢復的。后續也會講解碼跟蹤環路,畢竟這些代碼沒必要藏著掖著,傳播出去才能幫助更多的人!不過代碼肯定會收費,不然抄襲現象會滿天飛!知識付費是必然的趨勢!百度文庫的收費模式似乎已經被接受,連我自己都買了一些文檔。

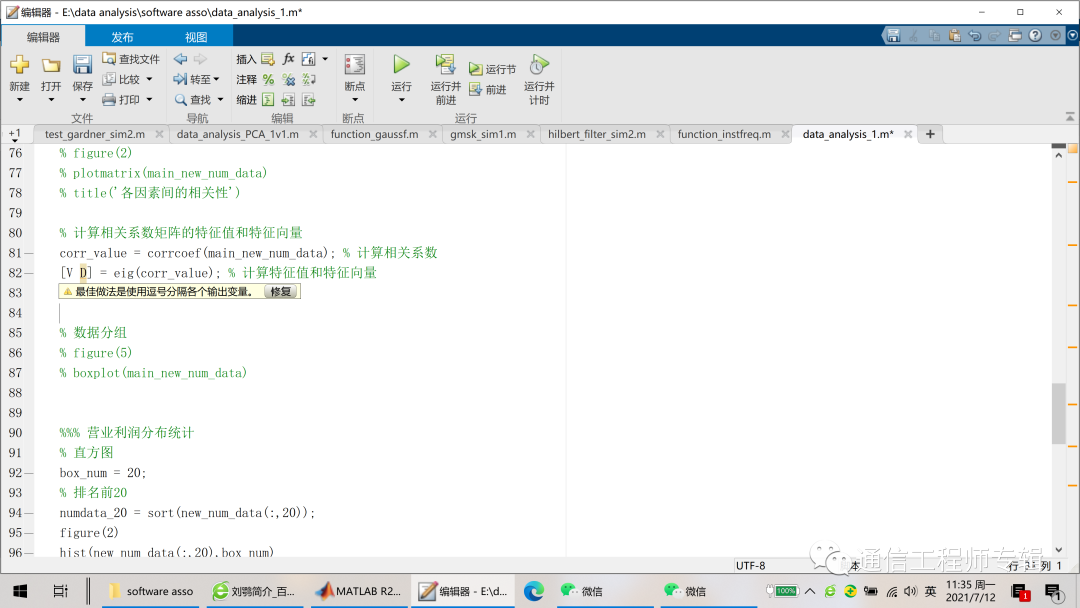

注意代碼書寫規范!

加個逗號吧!2021年7月,又在準備新的課題。不斷努力,更不能懈怠!趁著還有精力,就多寫寫技術文章吧。畢竟這類文章在網上太少了。2021年7月12日,又開始寫數據分析的程序了。2023年6月,本人已經分析了企業運營數據、醫學數據,積累了很多經驗,再次準備錄制視頻課程。

跨學科的人才很稀缺!本人在仿真秀網站上也推出了數據分析的視頻課程。歡迎大家觀看。

繼續講解鎖相環!

來看看讀者寫的鎖相環代碼!

pe = zeros(1,N);

% 鑒相輸出

temp = zeros(1,N);

Uc = zeros(1,N); % 壓控電壓

原文標題:大學畢業設計一席談v2之十六 鎖相環(10)案例分析

-

通信網絡

+關注

關注

22文章

2105瀏覽量

54379

原文標題:大學畢業設計一席談v2之十六 鎖相環(10)?案例分析

文章出處:【微信號:gh_30373fc74387,微信公眾號:通信工程師專輯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Altera公司鎖相環IP核介紹

探索CDC516:高性能3.3V鎖相環時鐘驅動器

CDC2516:高性能鎖相環時鐘驅動器的深度解析

CDC509:高性能3.3V鎖相環時鐘驅動器

CDCVF2505 3.3 - V 時鐘鎖相環時鐘驅動器:設計與應用指南

CDCVF25081:高性能鎖相環時鐘驅動器深度解析

TLC2932A高性能鎖相環芯片詳解:設計與應用指南

探索TLC2933A高性能鎖相環:特性、應用與設計要點

?CDCVF2510 3.3V鎖相環時鐘驅動器技術文檔總結

?CDCVF2509 3.3V鎖相環時鐘驅動器技術文檔總結

?CDCVF25081 3.3-V 鎖相環時鐘驅動器技術文檔總結

?CDCVF2510A 3.3V鎖相環時鐘驅動器技術文檔總結

基于鎖相環的無軸承同步磁阻電機無速度傳感器檢測技術

高壓放大器在鎖相環穩定重復頻率研究中的應用

大學畢業設計一席談v2之十六 鎖相環(10)?案例分析

大學畢業設計一席談v2之十六 鎖相環(10)?案例分析

評論