AD9528:高性能JESD204B/JESD204C時鐘發生器的深度解析

在電子設計領域,時鐘發生器對于系統的穩定運行起著至關重要的作用。今天,我們就來深入探討一款功能強大的時鐘發生器——AD9528,它在高性能無線通信、醫療儀器等眾多領域都有著廣泛的應用。

文件下載:AD9528.pdf

一、AD9528的關鍵特性

1. 輸出配置靈活

AD9528擁有14個輸出通道,這些輸出可靈活配置為HSTL或LVDS電平。其中,6個輸出的最高頻率可達1.25 GHz,另外8個輸出最高頻率可達1 GHz,具體頻率取決于壓控晶體振蕩器(VCXO)的頻率精度,其啟動頻率精度小于100 ppm。

2. 精準的延時控制

每個輸出都配備了專用的8位分頻器,具備粗延時和細延時功能。粗延時有63個步長,為RF VCO分頻器輸出頻率周期的1/2,且不會引入抖動;細延時有15個步長,分辨率為31 ps。典型的輸出間偏斜僅為20 ps,還能對奇數分頻設置進行占空比校正。

3. 低抖動性能

在122.88 MHz、12 kHz至20 MHz的積分范圍內,絕對輸出抖動小于160 fs,能有效滿足對時鐘精度要求極高的應用場景。

4. 豐富的控制與監測功能

具備數字頻率鎖定檢測功能,支持SPI和I2C兼容的串行控制端口,方便工程師進行配置和調試。采用雙PLL架構,PLL1可對參考輸入時鐘進行清理,PLL2則能提供高頻時鐘,實現低積分抖動和低寬帶噪聲。

二、工作原理剖析

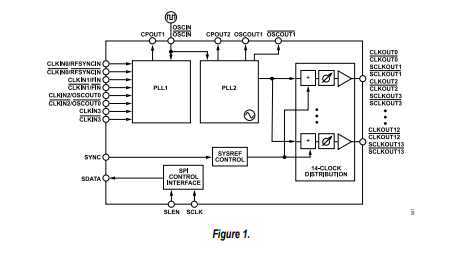

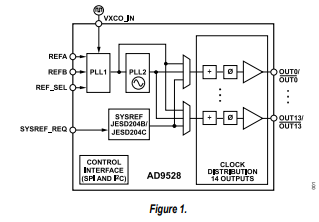

1. 雙PLL架構

- PLL1:由鑒相器(PFD)、電荷泵、外部VCXO和部分外部環路濾波器組成。它能夠以較窄的環路帶寬工作,有效抑制輸入參考信號上的抖動,其低相位噪聲輸出可作為PLL2的參考,也能路由到時鐘分配部分。

- PLL2:包含可選的輸入參考2×乘法器、參考分頻器、PFD、集成模擬環路濾波器、集成壓控振蕩器(VCO)和反饋分頻器。VCO的頻率范圍為3.450 GHz至4.025 GHz,能自動選擇合適的頻段。

2. 時鐘分配

時鐘分配部分由14個獨立通道組成,每個通道的輸入頻率源可選擇PLL1輸出、PLL2輸出或SYSREF。每個通道還包括一個專用的8位分頻器、兩個專用的相位延遲元件和一個輸出驅動器,可實現輸出通道的同步和相位調整。

3. SYSREF操作

AD9528支持JESD204B/JESD204C標準,可提供成對的設備時鐘和SYSREF時鐘信號,用于同步高速轉換器和邏輯設備。SYSREF信號有外部和內部兩種來源,可通過寄存器進行三種模式的配置,滿足不同應用的需求。

三、電氣特性詳解

1. 電源與電流

- 電源電壓:VDDx為3.3 V ± 5%,涵蓋多個VDD引腳。

- 電源電流:不同工作模式下的電源電流有所不同,如雙環模式、單環模式、緩沖模式和芯片掉電模式等。以雙環模式為例,不同VDD引腳的電流典型值在19 mA至71 mA之間。

- 功耗:典型雙環模式下的總功耗約為1675 mW,還給出了不同輸出模式下的增量功耗。

2. 輸入與輸出特性

- 輸入特性:支持差分和單端輸入,輸入頻率范圍、靈敏度、電容等參數都有明確規定。

- 輸出特性:HSTL和LVDS模式下的輸出頻率、上升/下降時間、占空比、差分輸出電壓擺幅等特性各有特點。例如,HSTL模式下輸出頻率最高可達1.25 GHz,LVDS模式下輸出頻率最高可達1 GHz。

3. 抖動與相位噪聲

在不同工作模式和輸出頻率下,時鐘輸出的絕對時間抖動和絕對相位噪聲都有詳細的測試數據。如在雙環模式下,HSTL輸出在122.88 MHz、12 kHz至20 MHz積分范圍內的絕對時間抖動典型值為159 fs。

四、應用案例

1. 無線通信領域

在高性能無線收發器、LTE和多載波GSM基站等設備中,AD9528可提供低抖動、低相位噪聲的時鐘信號,確保信號的準確傳輸和處理。

2. 醫療儀器領域

在醫療儀器中,高精度的時鐘信號對于數據采集和處理至關重要。AD9528的低抖動特性能夠滿足醫療儀器對時鐘精度的嚴格要求,提高設備的性能和可靠性。

五、設計建議

1. 電源設計

由于AD9528的功耗較大,在設計電源時要確保電源的穩定性和足夠的功率輸出。同時,要注意各個VDDx引腳的供電,即使某些部分不使用,也需為所有VDDx引腳供電。

2. 布局布線

合理的布局布線對于減少信號干擾和提高性能至關重要。要將敏感的時鐘信號與其他信號分開,避免相互干擾。同時,要注意外部環路濾波器和去耦電容的布局,確保其靠近芯片引腳。

3. 散熱設計

考慮到AD9528的功耗,散熱設計不容忽視。可根據實際應用情況選擇合適的散熱方式,如使用散熱片、風扇等,確保芯片在安全的溫度范圍內工作。

六、總結

AD9528作為一款高性能的JESD204B/JESD204C時鐘發生器,具有輸出配置靈活、延時控制精準、低抖動性能等諸多優點。通過深入了解其工作原理和電氣特性,工程師可以更好地將其應用于各種電子系統中。在設計過程中,要注意電源、布局布線和散熱等方面的問題,以充分發揮AD9528的性能優勢。希望本文能為電子工程師在使用AD9528進行設計時提供有益的參考。

你在使用AD9528的過程中遇到過哪些問題?或者你對它的應用有什么獨特的見解?歡迎在評論區留言分享。

-

時鐘發生器

+關注

關注

1文章

352瀏覽量

70138 -

電子設計

+關注

關注

42文章

2288瀏覽量

49902 -

ad9528

+關注

關注

1文章

6瀏覽量

2972

發布評論請先 登錄

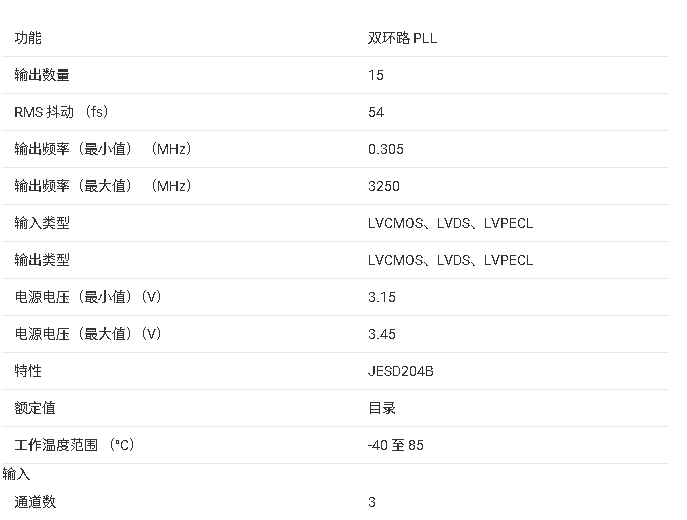

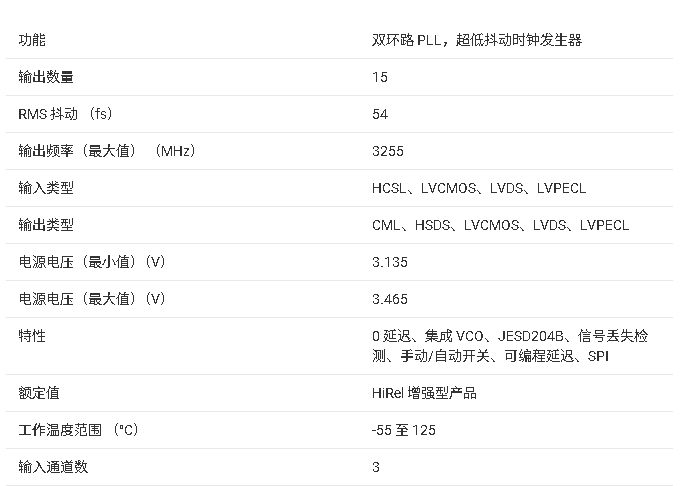

LMK04828 超低噪聲JESD204B兼容時鐘抖動清除器技術手冊

?LMK0482x系列超低噪聲JESD204B兼容時鐘抖動清除器技術文檔總結

LMK04616 超低噪聲低功耗JESD204B兼容時鐘抖動清除器總結

?LMK04828-EP 超低噪聲JESD204B兼容時鐘抖動清除器總結

LMK04832 超低噪聲、3.2 GHz、15 輸出、JESD204B 時鐘抖動清除器技術手冊

?LMK04368-EP 超低噪聲JESD204B/C雙環路時鐘抖動清除器總結

替代HMC7044超低噪高性能時鐘抖動消除器支持JESD204B

LTC6953具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz時鐘分配器技術手冊

HMC7044B支持JESD204B和JESD204C的高性能、3.2GHz、14輸出抖動衰減器技術手冊

AD9680 JESD204B接口的不穩定會導致較大的電流波動,怎么解決?

AD9528提供14路LVDS/HSTL輸出的JESD204B/JESD204C時鐘發生器技術手冊

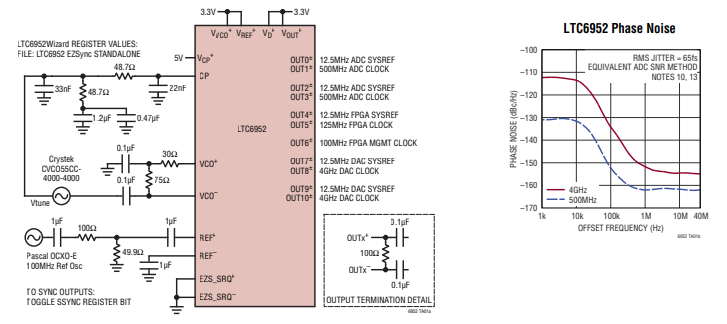

LTC6952具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz PLL技術手冊

AD9528:高性能JESD204B/JESD204C時鐘發生器的深度解析

AD9528:高性能JESD204B/JESD204C時鐘發生器的深度解析

評論