鎖相環的一些概念

1、捕獲、鎖定與跟蹤的概念

捕獲,是指從輸入信號加到鎖相環輸入端開始開始,一直到環路達到鎖定的全過程。

鎖相環的鎖定是指鎖相環的輸出頻率等于輸入頻率,而輸出信號的相位跟隨輸入信號的變化而變化。

跟蹤是指鎖相環鎖定后的狀態,一旦鎖相環進入鎖定狀態,若輸入信號產生了相位的變化,環路就調整壓控振蕩器的控制電壓使得其輸出信號的相位跟隨輸入信號的相位變化,即保持恒定的穩態相位差。這種狀態稱為跟蹤或同步狀態。

2、捕獲時間和穩態相差

捕獲時間是指捕獲過程所需的時間。捕獲時間的大小不僅與環路參數有關,而且與起始狀態有關。

當環路進入同步狀態之后,環內被控振蕩器的振蕩器頻率已經等于輸入信號的頻率,兩者之間只差一個固定的相位。這個相位差稱為穩態相差。反過來說,若穩態相差為一個常數或等于0,則說明環路處于鎖定狀態。

3、相位捕獲和頻率捕獲

“相位捕獲”指在捕獲過程中,相位沒有經過2π的周期跳躍就能進入的鎖定狀態,即捕獲過程小于一個2π周期的捕獲過程稱為相位捕獲,又稱快捕獲。“頻率捕獲”指捕獲經歷一個以上的頻率周期的捕獲過程。即意味著環路的輸入信號頻率與輸出信號頻率在開始捕獲前相差至少一個周期。一般來說,一個鎖相環從捕獲到鎖定都要經歷從頻率捕獲到相位捕獲兩個過程。

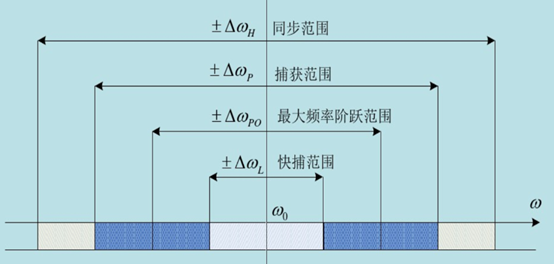

如下圖的快捕范圍就是快捕帶,只有相位捕獲,因此收斂較快,而除快捕范圍的捕獲帶則首先要進行頻率捕獲,然后才是相位捕獲。頻率捕獲相對來說是一個慢的過程,因此收斂較慢。

4、捕獲帶和同步帶

捕獲帶是指保證環路必然進入鎖定的最大固有頻差值。換句話說,就是在保證環路不出現穩定的差拍狀態所允許的最大固有頻差值。

一旦環路進入鎖定狀態,系統就處于跟蹤狀態。隨著輸入信號的頻率和相位的變化,環路應該始終能跟蹤其變化,但一旦輸入信號的頻率與被控壓控振蕩器的自由振蕩器頻率相差太多,環路就會失去跟蹤能力,這種狀態稱為“失鎖”。

同步帶是指系統保持同步的最大固有頻差值

5、最大頻率階躍范圍

描述PLL對于穩定工作狀態的動態限制。環路初始處于鎖定狀態,當輸入信號的頻率發生階躍變化的幅度在失鎖帶的范圍之內,環路能夠保持鎖定。然而,當輸入信號的頻率發生階躍變化的幅度超出失鎖帶的范圍,環路不能保持鎖定,輸出信號無法跟蹤輸入參考信號。當然,通過緩慢的捕獲過程,環路可再次入鎖。

鑒相器

關于鑒頻器介紹一下2種鑒頻器:

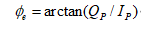

鑒頻器1,二象限反正切函數,

優點:最準確的鑒相方法,實際相位差異位于-90°至+90°的范圍之內時,該鑒相器的工作保持線性,并且其輸出的鑒相結果與信號幅值無關。

缺點:需要進行反正切求值,因而它也是計算量最大的一種。

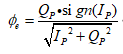

鑒頻器2

優點:計算量小, 適合純邏輯實現

缺點:鑒頻近似準確,鑒相結果與

成正比,并且與信號幅值有關

環路濾波器 和 頻率可變振蕩器 與鎖頻環一樣,不在重復敘述

Matlab 程序

在鎖頻環的程序基礎上添加鎖相環,設定前面500ms是鎖頻環工作,將頻率快速的拉到接近的范圍,然后切換到鎖相環,期間在1s的時候頻率突變10Hz,在2s的時候突變30Hz,在3s的時候突變100Hz,來理解快捕范圍,頻率階躍、捕獲帶等這些概念。為了顯示更加清楚,這里就不加碼元信息了

format long g;

clc;clear all;close all

SampleClk = 4.1e6;

PointNum = SampleClk*5;

IF = 1e6- 240 ;

Carr_cos(1:SampleClk) = cos(2*pi*(IF/SampleClk).*[1:SampleClk] + 0);

Carr_sin(1:SampleClk) = sin(2*pi*(IF/SampleClk).*[1:SampleClk] + 0);

IF = IF + 10;

Carr_cos(1+SampleClk:PointNum) = cos(2*pi*(IF/SampleClk).*[SampleClk+1:PointNum] + 0);

Carr_sin(1+SampleClk:PointNum) = sin(2*pi*(IF/SampleClk).*[SampleClk+1:PointNum] + 0);

IF = IF + 30;

Carr_cos(1+2*SampleClk:PointNum) = cos(2*pi*(IF/SampleClk).*[2*SampleClk+1:PointNum] + 0);

Carr_sin(1+2*SampleClk:PointNum) = sin(2*pi*(IF/SampleClk).*[2*SampleClk+1:PointNum] + 0);

IF = IF + 100;

Carr_cos(1+3*SampleClk:PointNum) = cos(2*pi*(IF/SampleClk).*[3*SampleClk+1:PointNum] + 0);

Carr_sin(1+3*SampleClk:PointNum) = sin(2*pi*(IF/SampleClk).*[3*SampleClk+1:PointNum] + 0);

signal0 = Carr_cos +j*Carr_sin;

data = awgn(signal0,-5,'measured');

n = SampleClk/1000;

num=1000;

a=rand(1,num);

a(a>0.5)=1;

a(a<=0.5)=-1;

% for m = 1 1000

% data(m*n+1:(m + 1)*n) = a(m)*data(m*n+1:(m + 1)*n);

% end

fc = 1e6;

n = SampleClk/1000;

nf = floor(length(data)/n);

FAccCarReg0 = 0;

PAccCarReg0 = 0;

frame = 0;

FLL_BL = 100;

PLL_BL = 20;

tc1 = 1/1000;

k1 = 1;

[d0,d1] = Fil2ndPara(k1,FLL_BL,tc1);

[c0,c1] = Fil2ndPara(k1,PLL_BL,tc1);

df(1:nf) = 0;

df1(1:nf) = 0;

PQaccu = 0;

PIaccu = 0;

fll = 0;

pll = 0;

carr_accu = 0;

counter = 1;

init_carr_freq = fc;

for frame = 1 : nf

% frame

carr_freq = init_carr_freq + fll + pll;

for clk = 0 : n-1

%clk

carr_accu = rem(carr_accu,1);

cosine = cos(2*pi*(carr_accu));

sine = sin(2*pi*(carr_accu));

baseband = (data(((frame-1)*n+clk+1))).*(cosine -j*sine);

PI_clk = real(baseband);

PQ_clk = imag(baseband);

PQaccu = PQaccu + PQ_clk;

PIaccu = PIaccu + PI_clk;

carr_accu = carr_accu + carr_freq/SampleClk;

end

PQ(frame) = PQaccu;

PI(frame) = PIaccu;

if PI(frame) == 0

PI(frame) = 0.0000001;

end

PQaccu = 0;

PIaccu = 0;

if frame <5?

fll = 0;

pll = 0;

elseif(frame <500 )

df(frame) = FrqErr(PI,PQ,frame);

[fll,FAccCarReg0] = Fil2nd(d0,d1,FAccCarReg0,df(frame));

else

df1(frame) = PhaErr(PI,PQ,frame);

[pll,PAccCarReg0] = Fil2nd(c0,c1,PAccCarReg0,df1(frame));

end

fll_frame(frame) = fll + pll;

end

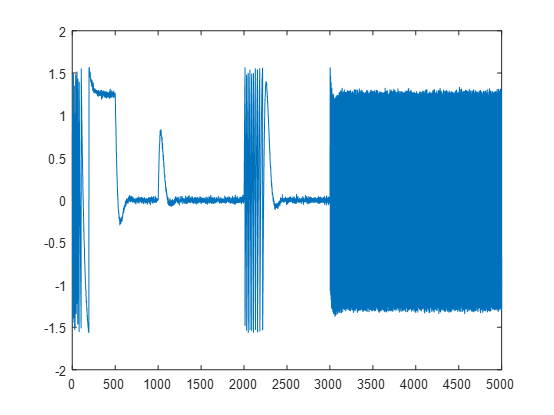

figure(1)

plot(fll_frame);

figure(4)

plot(PI);

hold on

plot(PQ);

hold on

figure(5)

plot(atan(PQ./PI))

從頻率跟蹤圖可以明顯的看出

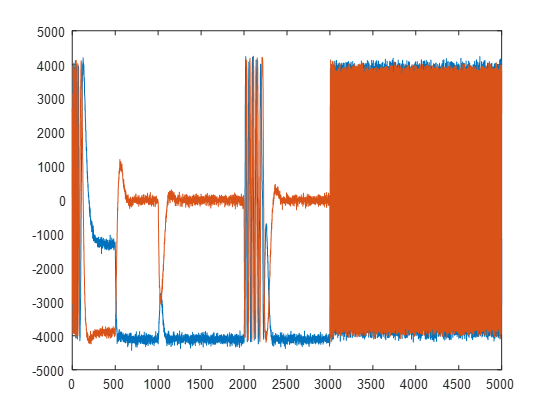

在500ms鎖頻環轉鎖相環的時候,誤差頻率很小,因此處于快捕帶,只需要對相位進行捕獲,收斂很快。在1s的時候,頻率突變10Hz,環路仍然保持鎖定,很快便調整到了正確的頻率,因此10Hz屬于最大階躍范圍內,2s的時候,頻率突變30Hz,很明顯的頻率出現了震蕩,這就是失鎖了,但仍處于捕獲帶內,因此花了一點時間又重新鎖定到正確的頻率上,最后,頻率突變100Hz,則直接跳出了捕獲帶之外,無法重新鎖定了。

從I/Q幅度圖以及鑒相值可以看出

在500ms和1s的時候,相位沒有出現2*pi的翻轉,而在2s的時候出現了多次的2pi的翻轉,這也印證了最開始介紹鎖相環的概念中的 頻率捕獲和相位捕獲的內容。

IQ幅度圖:

鑒相值圖:

原文標題:FPGA學習-數字鎖相環

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

審核編輯:劉清

-

鎖相環

+關注

關注

36文章

635瀏覽量

91123 -

pll

+關注

關注

6文章

982瀏覽量

138182 -

鑒頻器

+關注

關注

1文章

28瀏覽量

33889

發布評論請先 登錄

Altera公司鎖相環IP核介紹

探索CDC516:高性能3.3V鎖相環時鐘驅動器

CDC2516:高性能鎖相環時鐘驅動器的深度解析

CDC509:高性能3.3V鎖相環時鐘驅動器

CDCVF2505 3.3 - V 時鐘鎖相環時鐘驅動器:設計與應用指南

CDCVF25081:高性能鎖相環時鐘驅動器深度解析

TLC2932A高性能鎖相環芯片詳解:設計與應用指南

探索TLC2933A高性能鎖相環:特性、應用與設計要點

TI CDCU877和CDCU877A:高性能1.8V鎖相環時鐘驅動器深度解析

爬壁機器人磁鐵的一些常見問題

?CDCVF2510 3.3V鎖相環時鐘驅動器技術文檔總結

?CDCVF2510A 3.3V鎖相環時鐘驅動器技術文檔總結

基于鎖相環的無軸承同步磁阻電機無速度傳感器檢測技術

高壓放大器在鎖相環穩定重復頻率研究中的應用

小編科普一下關于鎖相環的一些概念

小編科普一下關于鎖相環的一些概念

評論