10nm。研發部門正在努力擴展該技術,并最終將其替換為新的存儲器類型。 但是,到目前為止,還沒有直接的替代方法。并且,在采用新解決方案之前,供應商將繼續擴展DRAM并提高性能,盡管在當前1xnm節點體制下將逐步增加。并且在未來的節點上,部分但不是全部DR

2019-11-25 11:33:18 6943

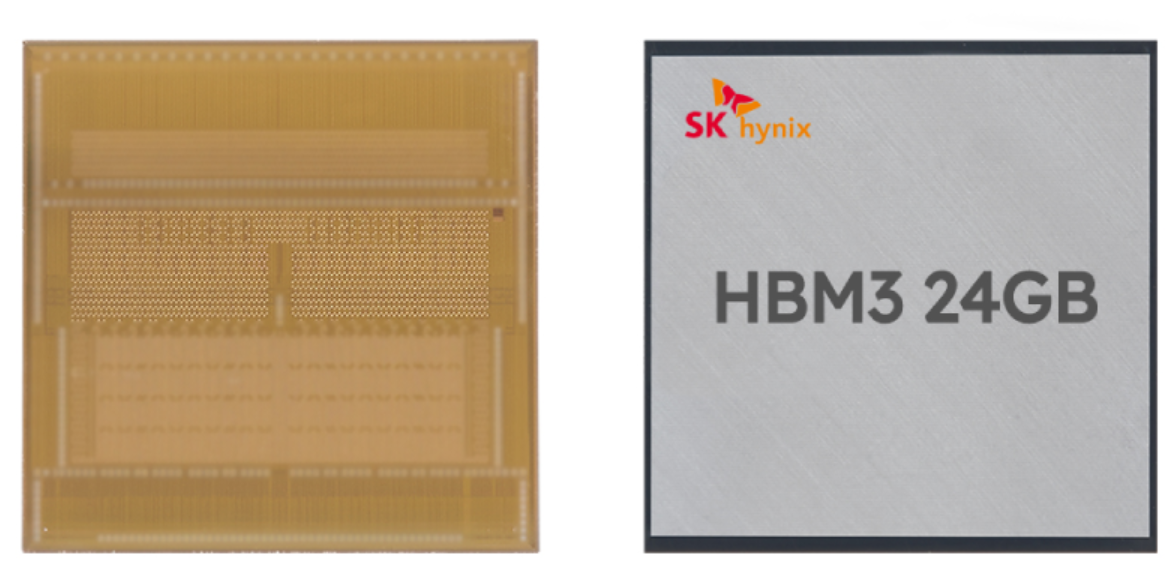

6943 視為堆疊邏輯與內存、3D NAND,甚至可能在高帶寬存儲(HBM)中的多層DRAM堆疊的關鍵技術。垂直堆疊使得芯片制造商能夠將互連間距從35μm的銅微凸點提升到10μm甚至更小。

2025-05-22 11:24:18 1405

1405

DRAM(Dynamic Random Access Memory) 即動態隨機存取存儲器,它和 SRAM(靜態隨機存取存儲器)一樣都是常見的系統內存,也就是說我們個人電腦里的內存條通常都是DRAM

2020-12-01 15:18:29 6409

6409

于所有類型的DRAM,有望顯著降低DRAM成本。 到目前為止,美光已將其DRAM生產的很大一部分轉移到了1Znm節點,該節點既提供高位密度(較低的單位成本)又提供高性能。美光表示,從利潤率和產品組合角度來說,現在的感覺相當好。美光的1α制造工藝預計將比1Z(成熟的成品率)

2021-01-27 15:37:31 3660

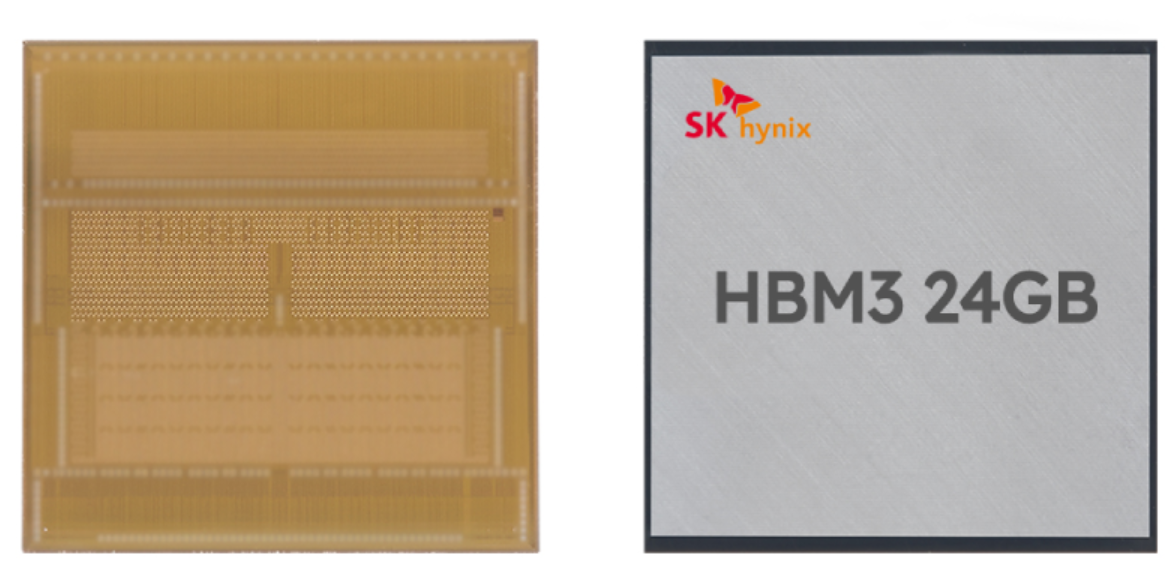

3660 電子發燒友網報道(文/黃晶晶) SK海力士近日發布全球首次實現垂直堆疊12個單品DRAM芯片,成功開發出最高容量24GB的HBM3 DRAM新產品。

2023-04-23 00:01:00 4808

4808

電子發燒友網報道(文/黃晶晶)高帶寬存儲HBM因數據中心、AI訓練而大熱,HBM三強不同程度地受益于這一存儲產品的營收增長,甚至就此改變了DRAM市場的格局。根據CFM閃存市場的分析數據,2025年

2025-05-10 00:58:00 8824

8824 。SRAM內部采用的是雙穩態電路的形式來存儲數據。所以SRAM的電路結構非常復雜。制造相同容量的SRAM比DRAM的成本高的多。正因為如此,才使其發展受到了限制。因此目前SRAM基本上只用于CPU內部

2012-08-15 17:11:45

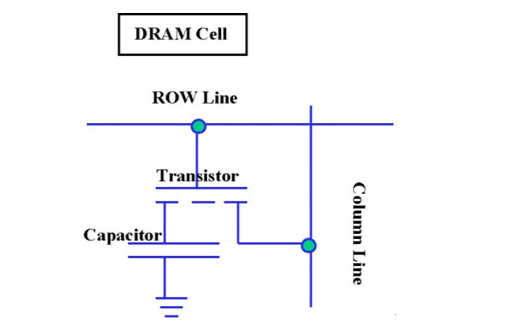

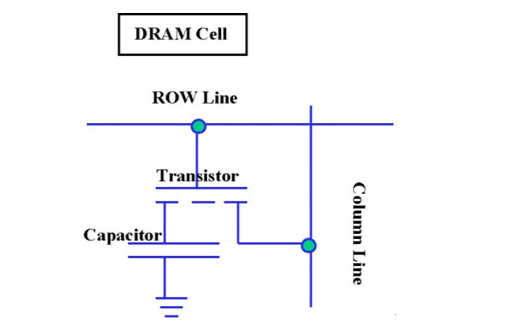

DRAM是一種半導體存儲器,主要的作用原理是利用電容內存儲電荷的多寡來代表一個二進制bit是1還是0。與SRAM相比的DRAM的優勢在于結構簡單,每一個bit的數據都只需一個電容跟一個晶體管來處

2020-12-10 15:49:11

1.(判斷題)DRAM上電時存儲單元的內容是全0,而Flash上電時存儲單元的內容是全1。(4分) A.正確B.錯誤 FLASH可保存 上電后不知道是啥2.(判斷題)眼圖可以用來分析高速信號的碼間

2021-07-22 08:57:49

RAM有哪些分類?特點是什么?DRAM和SRAM對比分析哪個好?

2022-01-20 07:16:10

某16K x 4的存儲體由16個字長為1的 DRAM芯片在位方向和字方向同時擴展而成,DRAM芯片中所有的記憶單元排列成行列相等的存儲矩陣。分析:由題得,16個DRAM芯片需要先在位方向擴展為4位得

2022-03-02 06:18:45

在本文中,我們將介紹一種新型的非易失性DRAM,以及它與當前內存技術的比較。DRAM是計算技術中必不可少的組件,但并非沒有缺陷。在本文中,我們將研究一種新提出的存儲器-非易失性DRAM-以及它與當前

2020-09-25 08:01:20

【作者】:果建民;【來源】:《廣播電視信息》2010年03期【摘要】:在廣電領域,由于存儲規模、投資和需求的不同,各種存儲結構均得到了廣泛的應用,本文重點討論常見的幾種存儲結構,并為選型提供參考意見

2010-04-23 11:47:34

所謂的寄存器、內存等用于存儲信息的復雜結構。存儲器的分類存儲器分為易失性存儲器和非易失性存儲器;所謂易失性存儲器是指設備掉電,存儲的信息自動清除,而非易失性存儲器具有存儲時間長的功能。易失性存儲器主要指

2021-12-10 06:54:11

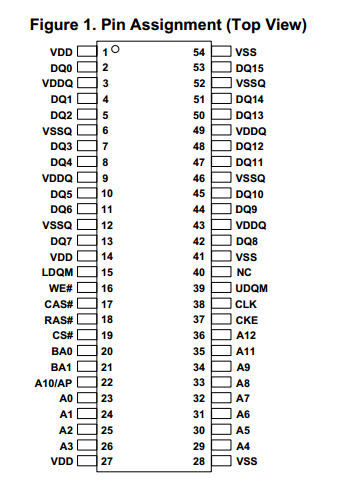

目錄【1】存儲器的層次結構【2】存儲器的分類【3】SRAM基本原理:結構:芯片參數與引腳解讀:CPU與SRAM的連接方式【4】DRAM基本原理:結構芯片引腳解讀:【5】存儲器系統設計【6】存儲器擴展

2021-07-29 06:21:48

存儲管理的磁盤結構分為哪幾部分?磁盤調度算法有哪幾種?分別有何優缺點?

2021-12-23 09:57:35

的L1 Cache存儲管理段式存儲管理頁式存儲管理存儲系統的層次結構技術指標層次結構局部性原理主存儲器讀寫存儲器只讀存儲器存儲器地址譯碼主存空間分配高速緩沖存儲器工作原理地址映射替換算法寫入策略80486的L1 CachePentium的L1 Cache存儲管理段式存儲管理頁式存

2021-07-29 09:47:21

各位大神好,我想用FPGA讀寫DRAM存儲器,求大神指點哪位大佬有代碼分析一份更是感激不盡,好人一生平安。

2018-01-14 15:31:32

STM32F4的存儲結構是由哪些部分組成的?STM32 Flash的主要特性有哪些?

2021-09-27 08:32:06

1、什么是堆疊設計也稱作系統設計,根據產品規劃,產品定義的要求,為實現一定的功能,設計出合理可靠的具備可量產性的PCB及其周邊元器件擺放的一種方案。2、堆疊工程師一般由結構工程師進行堆疊,有些公司

2021-11-12 08:17:17

和DRAM),40μm的芯片堆疊8個總 厚度為1.6 mm,堆疊兩個厚度為0.8 mm。如圖1所示。圖1 元器件內芯片的堆疊 堆疊元器件(Amkor PoP)典型結構如圖2所示: ·底部PSvfBGA

2018-09-07 15:28:20

(FTL,磨損均衡,糾錯等),存在讀寫干擾問題。

結構演進:

平面 NAND:傳統二維結構,工藝微縮遇到瓶頸。

3D NAND:將存儲單元垂直堆疊(幾十層到幾百層),突破密度限制,降低成本,提高

2025-06-24 09:09:39

單片機內部存儲結構分析存儲器的工作原理半導體存儲器的分類

2021-04-02 07:01:26

單片機內部結構分析單片機的基本概念存儲器的工作原理

2021-02-19 06:27:20

哈弗結構是什么意思?加劇CPU和主存之間速度差異的原因有哪些?導致DRAM比SRAM慢的原因有哪些?虛擬存儲器的最大容量是由什么原因決定的?

2021-08-11 08:07:31

(SRAM、DRAM、DDRAM)4.主存儲器(Flash、PROM、EPROM、EEPROM)5.外部存儲器(磁盤、光盤、CF、SD卡)6.遠程二級存儲(分布...

2021-12-22 06:30:43

嵌入式系統(二)嵌入式系統結構硬件層中間層系統軟件層應用軟件層常用開發工具GNU ToolsQTEclipse交叉開發環境交叉調試系統測試內存分析工具性能分析工具覆蓋分析工具嵌入式系統結構硬件層硬件

2021-12-22 08:03:19

處理器的 BIU(總線接口)單元產生存儲器讀請求。對微處理器的存儲器范圍編程后,BIU單元執行刷新周期時,被編程的存儲器范圍片選有效。存儲器是嵌入式計算機系統的重要組成部分之一。通常采用靜態存儲器,但是在

2011-02-24 09:33:15

開放式網絡化數控的基本概念是什么? 開放式網絡化數控平臺的基本結構是由哪些部分組成的?

2021-08-05 07:27:45

包括:DRAM、NAND FLASH、NOR FLASH。DRAM動態隨機存儲器(Dynamic RAM),“動態”二字指沒隔一段時間就會刷新充電一次,不然內部的數據就會消失。這是因為DRAM的基本單元

2019-09-18 09:05:09

存儲器的一般用途是代碼儲存。系統需要一個相對較小進的存儲,大約小2Gb. 這樣 .代碼可以從NOR閃存直接執行,這種存儲器也常用于嵌入式文件系統的存儲器,這些類型的系統中 DRAM 常用便簽式存儲器。在這

2018-05-17 09:45:35

下圖。 硅通孔TSV型堆疊 硅通孔TSV型堆疊一般是指將相同的芯片通過硅通孔TSV進行電氣連接,這種技術對工藝要求較高,需要對芯片內部的電路和結構有充分的了解,因為畢竟要在芯片上打孔,一不小心就會損壞

2020-11-27 16:39:05

器(DRAM)與靜態隨機存儲器(SRAM)兩大類。DRAM 以電容上存儲電荷數的多少來代表所存儲的數據,電路結構十分簡單(采用單管單電容1T-1C的電路形式),因此集成度很高,但是因為電容上的電荷會泄漏,為了能

2022-11-17 16:58:07

頻譜分析儀是常用的電子測量儀器之一,他的功能是分辨輸入信號中各個頻率成分并測量各個頻率成分的頻率和功率。下面看一下傳統頻譜分析儀的原理和現代頻譜分析儀(或稱為信號分析儀)的發展。圖1是傳統的掃頻式頻譜分析儀的結構框圖。圖1傳統掃頻式頻譜分析儀的結構框圖

2019-07-01 06:37:50

過程,通過智能測力識別方式防誤操作撞針,做到無損傷測量。 SJ51系列測長機各部分結構名稱 SJ51系列測長機采用高精度光柵測量系統、超高精密研磨導軌

2022-10-28 17:07:13

基于SRAM 和DRAM 結構的大容量FIFO 的設計與實現作者:楊奇 楊瑩摘要:本文分別針對Hynix 公司的兩款SRAM 和DRAM 器件,介紹了使用CPLD 進行接口連接和編程控制,來構成低成本

2010-02-06 10:41:10 45

45 網絡節點的交換結構在圖1所示的交換結構中,分析FDLs和TWC對交換性能的影響。圖中,1~4分別代表4條光纖輸入和輸出,每條光纖上復用9條波長,其中一條用于發

2009-02-28 11:44:14 1329

1329

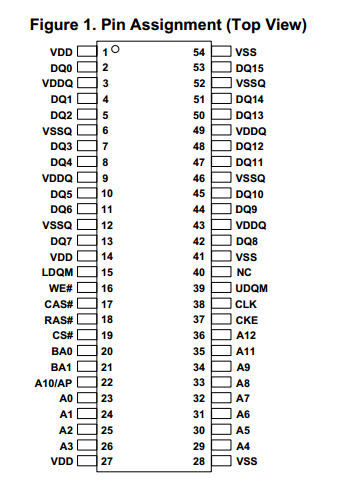

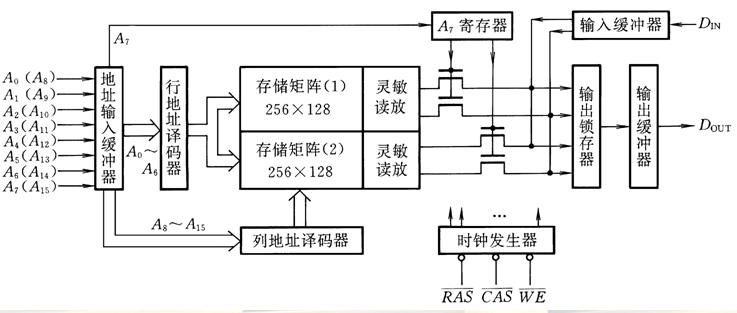

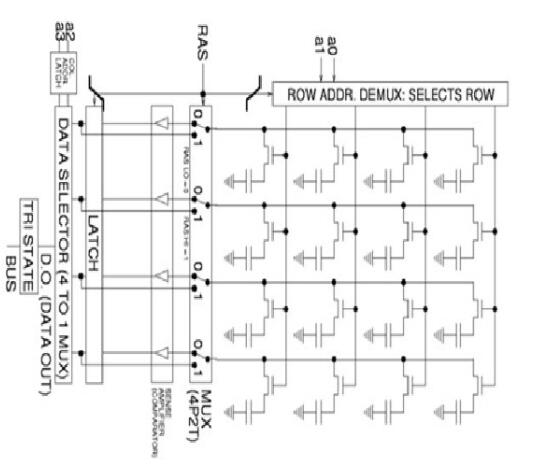

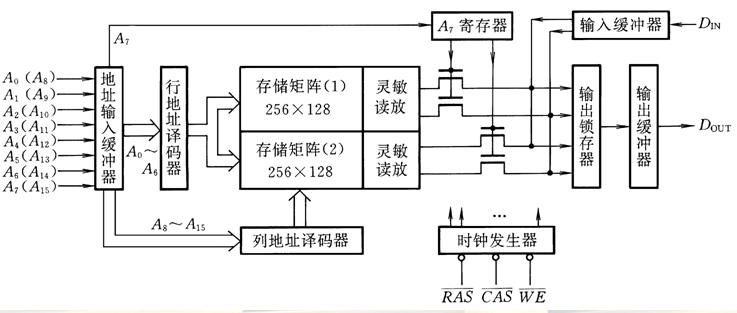

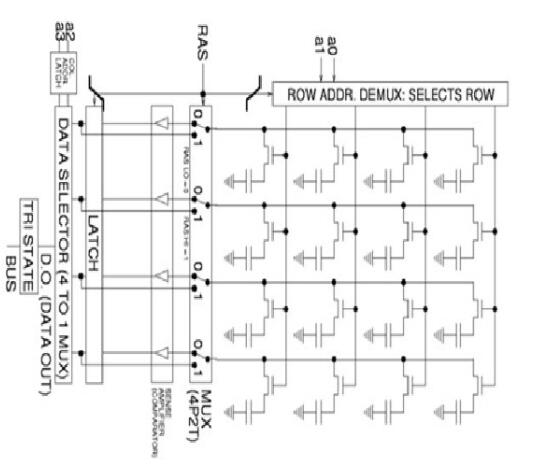

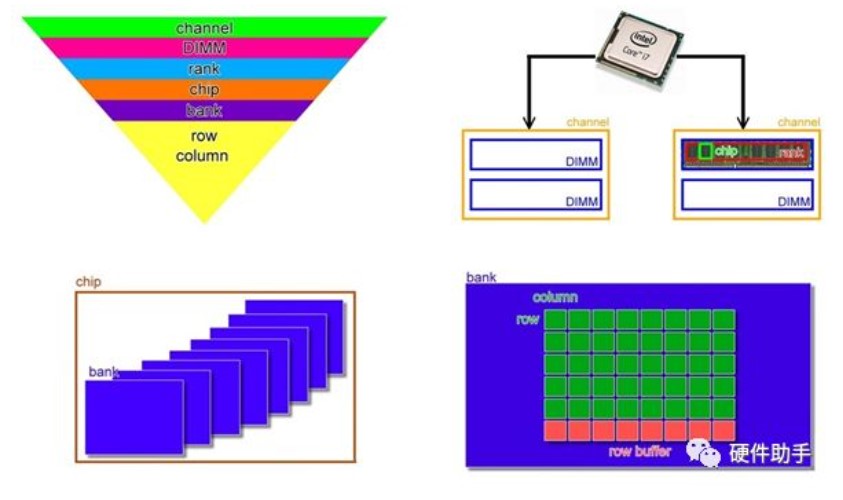

DRAM的總體結構框圖

2009-12-04 17:13:32 3921

3921

基于當代DRAM結構的存儲器控制器設計

1、引言

當代計算機系統越來越受存儲性能的限制。處理器性能每年以60%的速率增長,存儲器芯片每年僅僅增加10%的

2009-12-31 10:57:03 1028

1028

可堆疊式架構分歧

雖然標準組織在使用更新技術代替過時的ISA總線技術方面存在分歧,但經典PC / 104對嵌入式系統設計者仍具吸引力。

要點 * PC/

2010-01-26 09:48:15 859

859 DRAM,DRAM是什么意思

RAM (Random Access Memory隨機存貯器)是指通過指令可以隨機地、個別地對每個存儲單元進行訪問、訪問所需時間基本固定、且

2010-03-24 16:04:33 15009

15009 DRAM模塊,DRAM模塊是什么意思

DRAM 的英文全稱是"Dynamic RAM",翻譯成中文就是"動態隨機存儲器"。。DRAM 只能將數據保持很短的時間。為了保持數據,

2010-03-24 16:17:21 2726

2726 MCP存儲器,MCP存儲器結構原理

當前給定的MCP的概念為:MCP是在一個塑料封裝外殼內,垂直堆疊大小不同的各類存儲器或非存儲器芯片,

2010-03-24 16:31:28 2499

2499 存儲器的層次結構原理圖解分析

學習目錄:

理解多級存儲層次的思想及其作用;

掌

2010-04-13 16:16:12 13395

13395 集線器的堆疊

部分集線器具有堆疊功能。集線器堆疊是通過廠家提供的一條專用連接電纜,從一臺集線器的"UP"堆疊端口直接連接到另一臺集線器的"DOWN"堆疊端口

2010-01-08 10:15:16 1805

1805 超越摩爾定律,賽靈思全球首發堆疊硅片互聯技術,推出突破性的容量、帶寬和功耗 ,引領行業發展。 堆疊硅片互聯技術 每個工藝節點 FPGA 容量提升 2 倍的優勢 Virtex-7 系列的核心部分

2011-03-28 17:06:47 0

0 通過分析Hypertable 的源代碼,描述了CellStore 存儲結構,介紹其讀寫流程,總結了該結構存在的缺陷,并提出了優化思路。優化步驟主要包括:將關鍵字數據進行合并,建立關鍵字到數據

2011-05-12 16:37:28 27

27 從 DRAM 的發展及應用特點出發,針對使用DRAM 構成計算機主存時應解決的主存空間及尋址、多體交叉訪問構成并行主存結構、動態刷新等問題,以采用DRAM控制器W4~6AF構成80386微機主存的

2011-07-25 16:11:28 145

145 芯片堆疊封裝是提高存儲卡類產品存儲容量的主流技術之一,采用不同的芯片堆疊方案,可能會產生不同的堆疊效果。針對三種芯片堆疊的初始設計方案進行了分析,指出了堆疊方案失

2012-01-09 16:14:14 42

42 數據結構-邏輯存儲結構的相關詳細介紹,內容簡單

2015-10-29 15:14:26 2

2 計及節點相關性的含間歇分布式電源配電網概率潮流_劉洪

2017-01-04 16:32:50 1

1 基于FPGA的可堆疊存儲陣列設計與優化

2017-01-07 21:28:58 0

0 電路分析中網孔分析 與 節點分析的步驟方法總結

2017-03-14 16:09:09 0

0 記憶技術不停滯不前。存儲器結構的變化速度更快和更有效的結構的創建和使用在連續幾代人如DRAM SDRAM DDR DDR1、2、3、等。

2017-06-06 14:22:11 5

5 日前,存儲器芯片主要供應商之一美光公司(Micron)在香港舉行了 2014 夏季分析師大會,會上美光的高層管理人員就 DRAM、NAND 和新型存儲器的市場趨勢、技術發展以及 Micron 的公司

2017-10-20 16:08:26 49

49 FPGA中的存儲塊DRAM 某些FPGA終端,包含板載的、可以動態隨機訪問的存儲塊(DRAM),這些存儲塊可以在FPGA VI中直接訪問,速率非常高。 DRAM可以用來緩存大批量的數據,而且速度可以

2017-11-15 15:13:06 3688

3688

分布式存儲概念 與目前常見的集中式存儲技術不同,分布式存儲技術并不是將數據存儲在某個或多個特定的節點上,而是通過網絡使用企業中的每臺機器上的磁盤空間,并將這些分散的存儲資源構成一個虛擬的存儲設備

2017-11-17 09:26:41 24247

24247

自動編碼機算法中;同時,根據傳統dropout算法容易使部分節點長期處于熄火狀態的缺陷,提出了一種動態dropout改進算法,使用動態函數將傳統靜態熄火率修改為隨著迭代次數逐漸減小的動態熄火率;最后,利用動態dropout算法改進堆疊自動編碼機的預訓練模型

2017-12-26 14:37:48 0

0 的局部可修復碼,顯著降低了修復網絡開銷.然而,現有的基于編碼的分布式容錯存儲方案大都假設節點處于星型邏輯網絡結構中,忽略了實際的物理網絡拓撲結構和帶寬信息.為了實現拓撲感知的容錯存儲優化,相關研究在糾刪碼

2017-12-26 19:11:24 1

1 存儲器芯片領域,主要分為兩類:易失性和非易失性。易失性:斷電以后,存儲器內的信息就流失了,例如 DRAM,主要用來做PC機內存(如DDR)和手機內存(如LPDDR),兩者各占三成。非易失性:斷電以后

2018-04-09 15:45:33 113864

113864 Sony的Xperia XZ Premium和Xperia XZ兩款旗艦級智能手機搭載了具有960fps畫面更新率的Motion Eye相機模組。這款三層堆疊的CMOS影像傳感器(CIS)被面對背地安裝在DRAM上,使得DRAM與影像訊號處理器(ISP)面對面接在一起。

2018-04-28 17:54:34 13201

13201 下游需求結構來看,手機、服務器、PC三大應用消耗了絕大部分存儲器芯片。主流存儲器市場以DRAM及NANDFlash為主,立基型存儲器則以EEPROM、小容量DRAM、NorFlash、SLCNAND

2018-07-27 17:17:37 2948

2948 針對延遲容忍網絡(DTN)拓撲結構動態變化和節點存儲空間有限的問題,提出一種具有擁塞控制策略的DTN傳染路由(ERC~2)方法。該方法基于一種動態存儲狀態模型(DSSM),節點可通過感知網絡狀況動態

2019-11-05 16:15:20 4

4 DRAM是Dynamic random access memory 的縮寫,稱為動態隨機存取存儲器。主要運用在對功耗要求不太高、系統緩存要求容量比較大速度要求比較快的系統。

2020-07-16 10:39:17 5876

5876 DRAM模塊是大多電子設備均存在的模塊之一,大家對于DRAM也較為熟悉。但是,大家真的了解DRAM嗎?DRAM的基本單元的結構是什么樣的呢?DRAM的工作原理是什么呢?如果你對DRAM具有興趣,不妨繼續往下閱讀哦。

2020-10-31 11:51:29 46978

46978

的非易失性存儲器類型(PCM和MRAM)將在獨立存儲器中處于領先地位。 傳統存儲芯片到達技術節點 存儲器產業如今形成了DRAM芯片、NADA Flash芯片、特殊存儲器三個相對獨立的市場。 然而,隨著摩爾定律的延伸,技術需求也越來越高,傳統存儲芯片

2020-12-06 06:57:00 4266

4266 DRAM是一種半導體存儲器,主要的作用原理是利用電容內存儲電荷的多寡來代表一個二進制bit是1還是0。與SRAM相比的DRAM的優勢在于結構簡單,每一個bit的數據都只需一個電容跟一個晶體管來處

2020-12-11 15:11:29 4696

4696

最近Techinsights舉辦了一場關于存儲技術的網絡研討會,Jeongdong Choe博士介紹了他對最新的DRAM,NAND,新興和嵌入式存儲器技術的觀察與分析。以下概述了討論的相關主題。DRA

2020-12-24 13:13:46 1607

1607 云存儲中的¢eph分布式文件系統以其開原性和提供統一存儲能力的特點在企業和科研領域得到廣泛關注和應用。 CRUSH算法是eph分布式文件系統中的偽隨機數據分布算法·能實現在異構大規模層級結構化存儲

2021-03-31 10:46:34 13

13 1、什么是堆疊設計也稱作系統設計,根據產品規劃,產品定義的要求,為實現一定的功能,設計出合理可靠的具備可量產性的PCB及其周邊元器件擺放的一種方案。2、堆疊工程師一般由結構工程師進行堆疊,有些公司

2021-11-07 10:36:00 19

19 有限公司,納斯達克股票代碼:MU)今日宣布,其采用全球最先進技術節點的1β DRAM產品已開始向部分智能手機制造商和芯片平臺合作伙伴送樣以進行驗證,并做好了量產準備。美光率先在低功耗LPDDR5X移動內存上采用該新一代制程技術,其最高速率可達每秒8.5Gb。該節點在性能、密度和能效方面都有

2022-11-02 11:31:27 1096

1096

β DRAM 產品已開始向部分智能手機制造商和芯片平臺合作伙伴送樣以進行驗證,并做好了量產準備。美光率先在低功耗 LPDDR5X 移動內存上采用該新一代制程技術,其最高速率可達每秒 8.5Gb。該節點在性能、密度和能效方面都有顯著提升,將為市場帶來巨大收益。除了移動應用,基于 1β 節點的

2022-11-02 11:50:51 1703

1703 β DRAM產品已開始向部分智能手機制造商和芯片平臺合作伙伴送樣以進行驗證,并做好了量產準備。美光率先在低功耗LPDDR5X移動內存上采用該新一代制程技術,其最高速率可達每秒8.5Gb。該節點在性能

2022-11-02 17:27:48 1537

1537 DRAM包括:SDRAM、DDRx、SDR、LPDDRx、LPSDR、GDDR、RLDRAMx(Reduced Latency DRAM)、EDO DRAM、FPM DRAM、Mobile DRAM等等。

2023-01-12 09:12:48 10600

10600

內存與存儲解決方案領先供應商美光科技(Micron Technology Inc.)宣布,其采用全球最先進技術節點的1βDRAM產品已開始向部分智能手機制造商和芯片平臺合作伙伴送樣以進行驗證,并做好了量產準備。

2023-02-01 16:13:05 3032

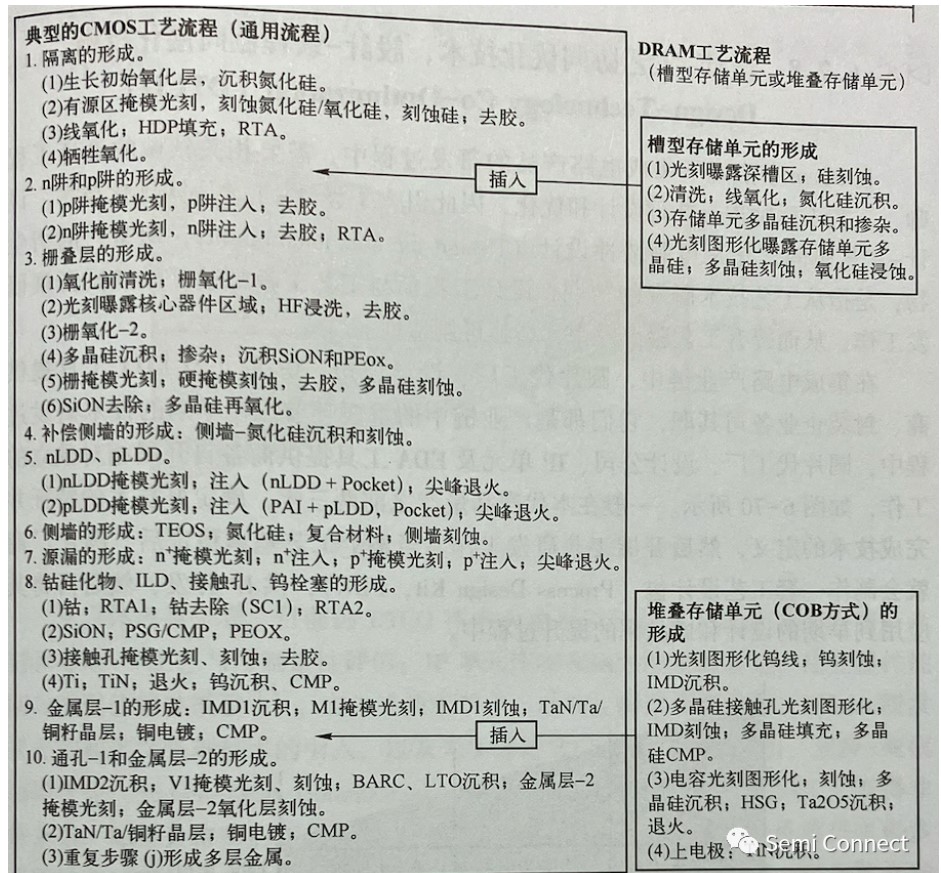

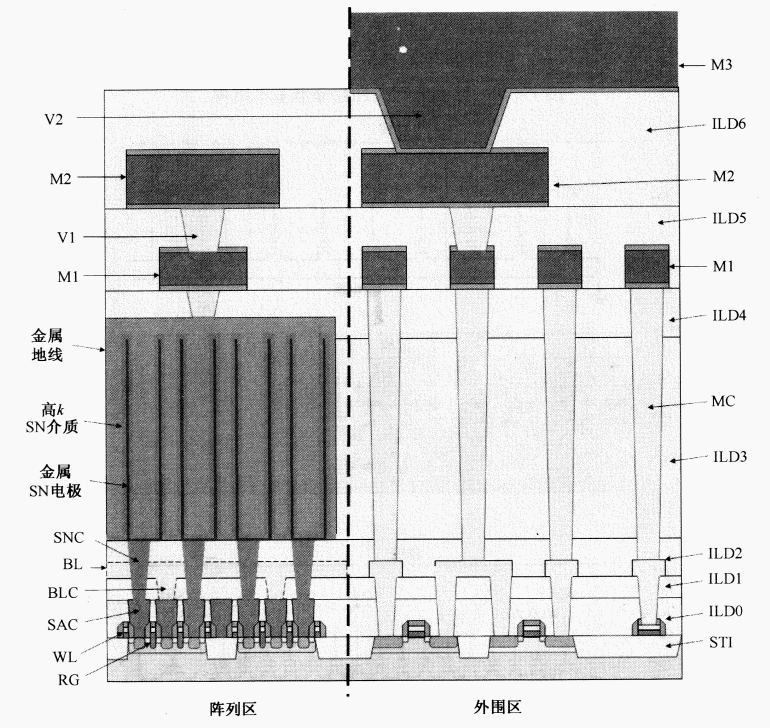

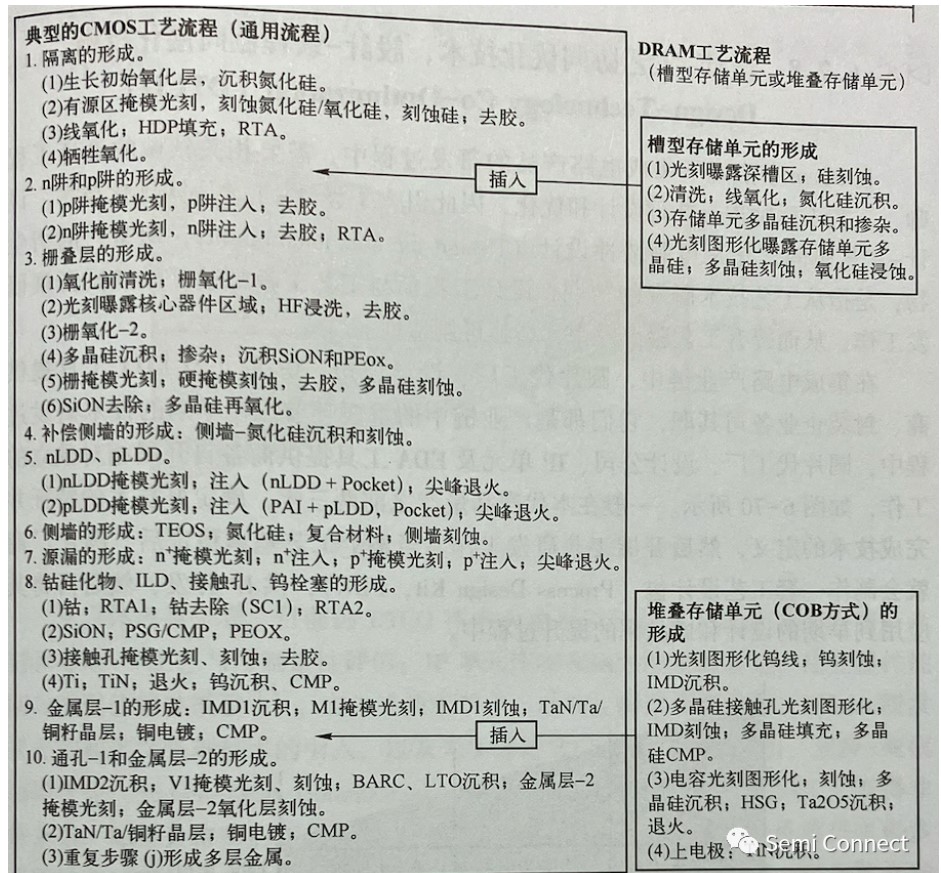

3032 槽(Deep Tench)式存儲單元和堆疊(Slack)式電容存儲單元。 70nm 技術節點后,堆疊式電容存儲單元逐漸成為業界主流。為了使系統向更高速、高密度、低功耗不斷優化,DRAM存儲單元也在不斷微縮(如14nm 工藝節點)。

2023-02-08 10:14:57 12490

12490 在當前計算密集的高性能系統中,動態隨機存儲器(DRAM)和嵌入式動態隨機存取存儲器(embedded-DRAM,eDRAM)是主要的動態快速讀/寫存儲器。

2023-02-08 10:14:39 1354

1354

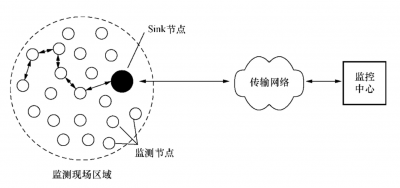

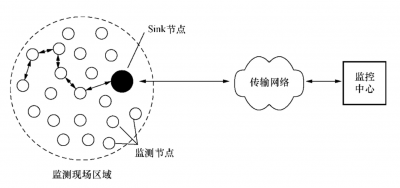

傳感器節點是一種微型嵌入式設備,要求它的價格低、功耗小,這些限制必然導致其攜帶的處理器能力比較弱、存儲器容量比較小。為了完成各種任務,傳感器節點需要完成監測數據的采集和轉換、數據的管理和處理、應答

2023-03-24 11:02:37 1199

1199

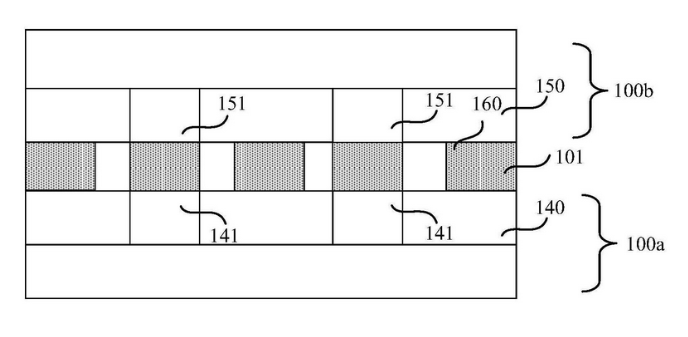

硅基全彩堆疊結構正在成為Micro LED的一條新技術路線。

2023-07-14 14:09:31 1092

1092 DRAM(Dynamic Random Access Memory)存儲器是一種易失性存儲器,意味著當斷電時,存儲在其中的信息會丟失。這是因為DRAM使用電容來存儲數據,電容需要持續地充電來保持數據的有效性。一旦斷電,電容會迅速失去電荷,導致存儲的數據丟失。

2023-07-28 15:02:03 5687

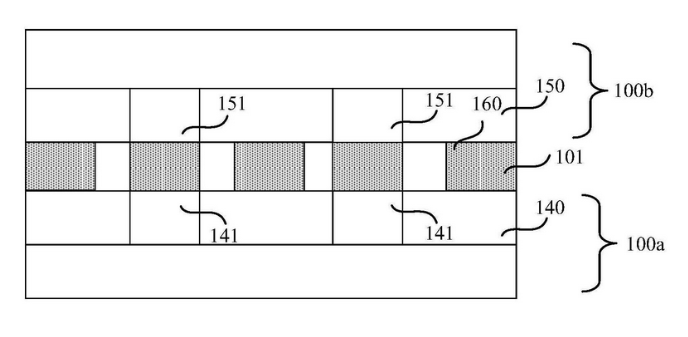

5687 芯片技術領域的應用概要,用于簡化芯片堆疊結構及其形成方法、芯片封裝結構、電子設備、芯片堆棧結構的制造技術。該芯片的堆疊結構至少包括兩個堆疊的芯片,每一個芯片包括電線層,電線層設有電具組。

2023-08-09 10:13:42 2753

2753

DRAM(Dynamic Random Access Memory)存儲器的存儲元是電容器和晶體管的組合。每個存儲單元由一個電容器和一個晶體管組成。電容器存儲位是用于存儲數據的。晶體管用于控制電容器

2023-08-21 14:30:02 3358

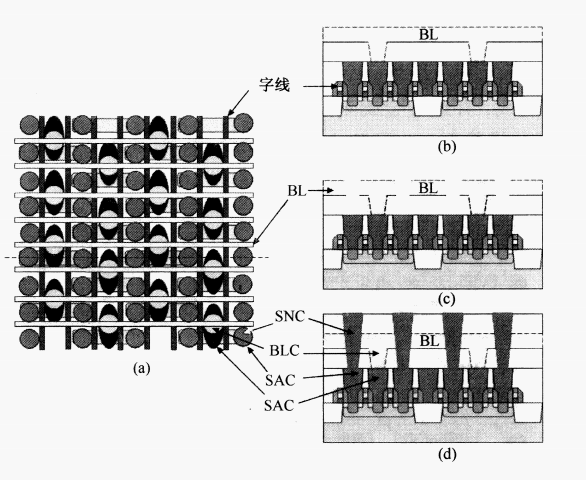

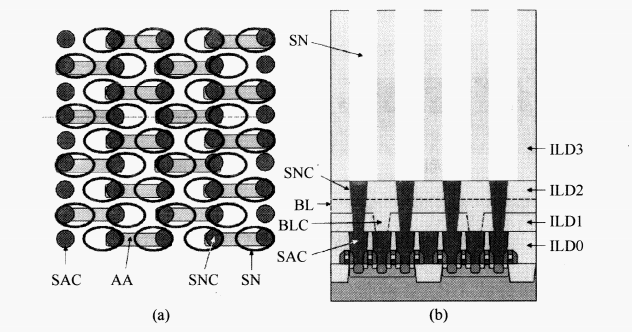

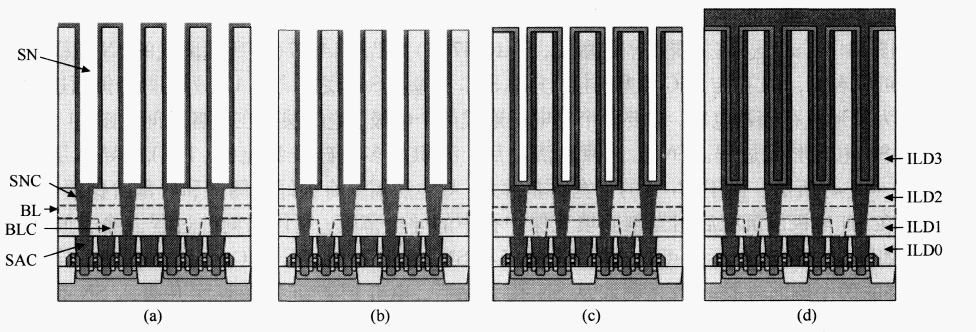

3358 在下面的圖中較為詳細的顯示了堆疊式DRAM單元STI和阱區形成工藝。下圖(a)為AA層版圖,虛線表示橫截面位置。

2023-09-04 09:32:37 6531

6531

本文將介紹芯片設計中動態隨機存取存儲器(DRAM)的相關知識,包括其工作原理、分類以及在現代電子設備中的應用。

2023-10-23 10:07:34 7663

7663 在全球半導體技術的激烈競爭中,SK海力士再次展示了其卓越的研發實力與創新能力。近日,在美國夏威夷舉行的VLSI 2024峰會上,SK海力士宣布了其在3D DRAM技術領域的最新研究成果,其中5層堆疊的3D DRAM良品率已高達56.1%,這一突破性的進展引起了業界的廣泛關注。

2024-06-27 10:50:22 1473

1473 今天我們來聊聊在計算機領域中非常關鍵的技術——DRAM(動態隨機存取存儲器)的內部結構和工作原理。

2024-07-26 11:40:18 4492

4492

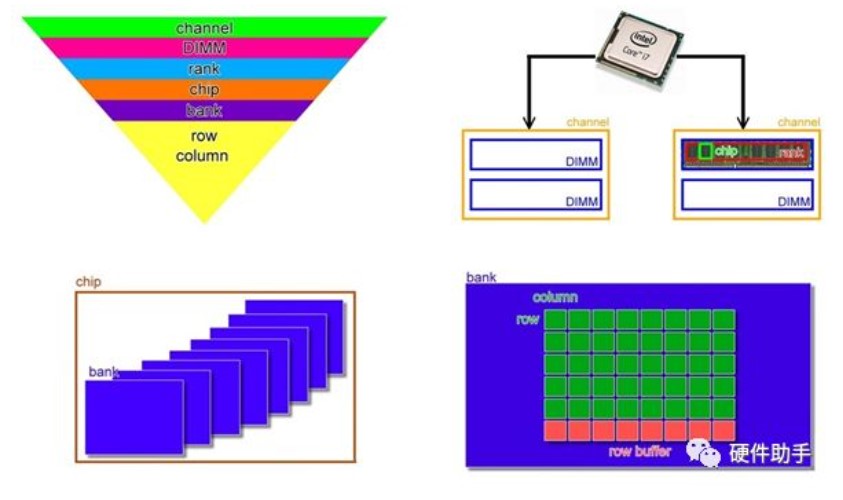

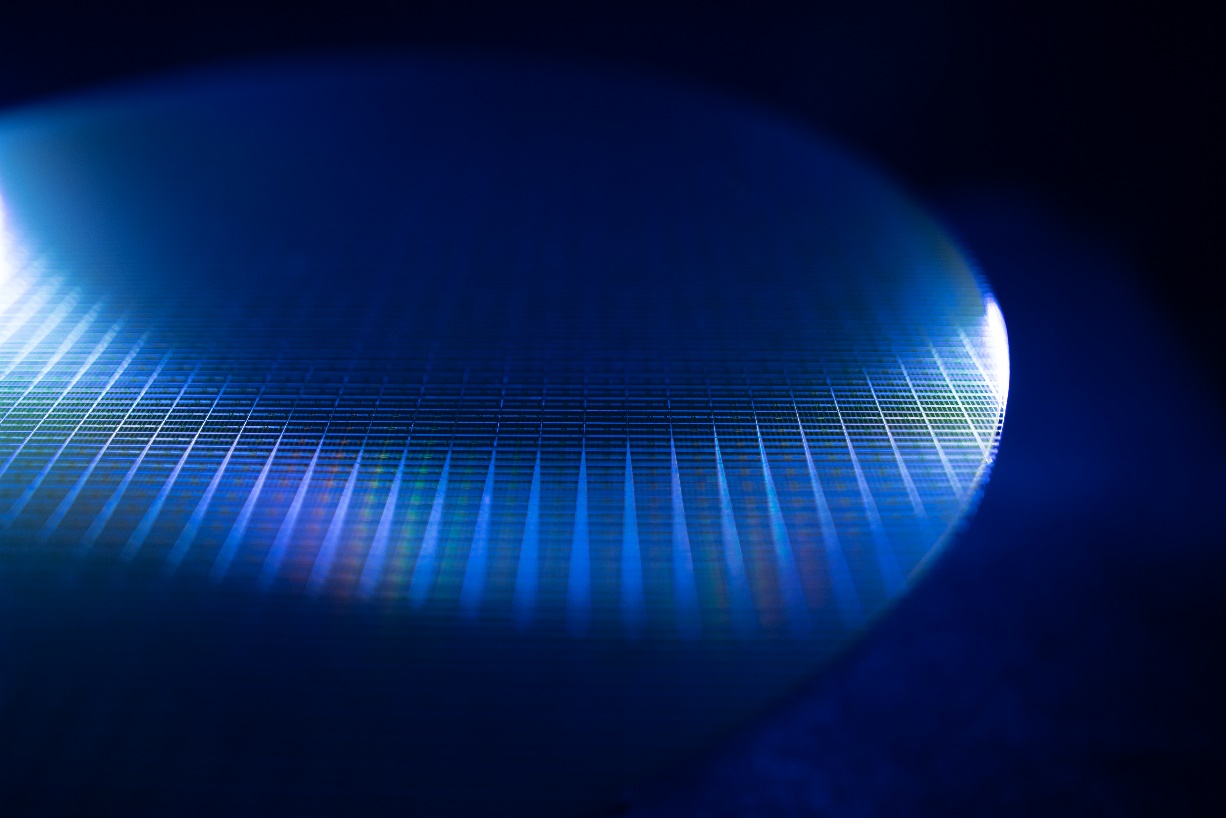

如果內存是一個巨大的矩陣,那么DRAM芯片就是這個矩陣的實體化。如下圖所示,一個DRAM芯片包含了8個array,每個array擁有1024行和256列的存儲單元。

2024-07-26 11:41:30 2710

2710

DRAM(Dynamic Random Access Memory),即動態隨機存取存儲器,是現代計算機系統中不可或缺的內存組件。其基本單元的設計簡潔而高效,主要由一個晶體管(MOSFET)和一個電容組成,這一組合使得DRAM能夠在保持成本效益的同時,實現高速的數據存取。

2024-09-10 14:42:49 3256

3256 DRAM(Dynamic Random Access Memory)即動態隨機存儲器,是一種半導體存儲器,用于計算機系統中的隨機存取存儲。它由許多存儲單元組成,每個存儲單元可以存儲一位或多位數據。DRAM的主要特點是集成度高、成本低,但讀寫速度相對較慢,并且需要定期刷新以保持數據。

2024-10-12 17:06:11 4113

4113 PSRAM(偽靜態隨機存儲器)是一種兼具SRAM接口協議與DRAM內核架構的特殊存儲器。它既保留了SRAM無需復雜刷新控制的易用特性,又繼承了DRAM的高密度低成本優勢。這種獨特的設計使PSRAM在嵌入式系統和移動設備領域獲得了廣泛應用。

2025-11-11 11:39:04 502

502 DRAM 被組織成層次化的陣列,總共由數十億個 DRAM 單元組成,每個單元存儲一位數據。

2025-12-26 15:10:02 690

690

? ? 電子發燒友網報道(文/黃晶晶)邊緣AI需要更快更大容量的存儲,為了突破接口速率、物理距離等因素,適用于AI推理的新型存儲技術受到更多的關注。華邦電子的CUBE、兆易創新的堆疊存儲,以及北京君

2025-09-08 06:05:00 11622

11622

電子發燒友App

電子發燒友App

評論