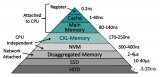

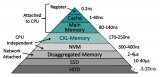

,所有這些元件都連接到越來越大的內存池。 但是,高性能計算(HPC)需要更新以有效連接這些處理元素并共享日益昂貴的內存的能力。參加旨在應對異構計算帶來的挑戰的Compute Express Link(CXL)計劃。它旨在提供高速緩存一致性以及在沒有不必要的成本的情況下

2021-03-19 11:41:14 11189

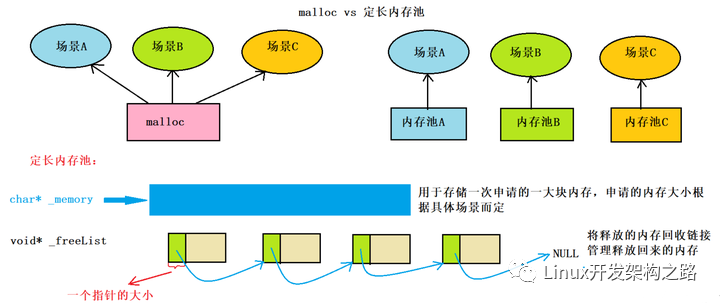

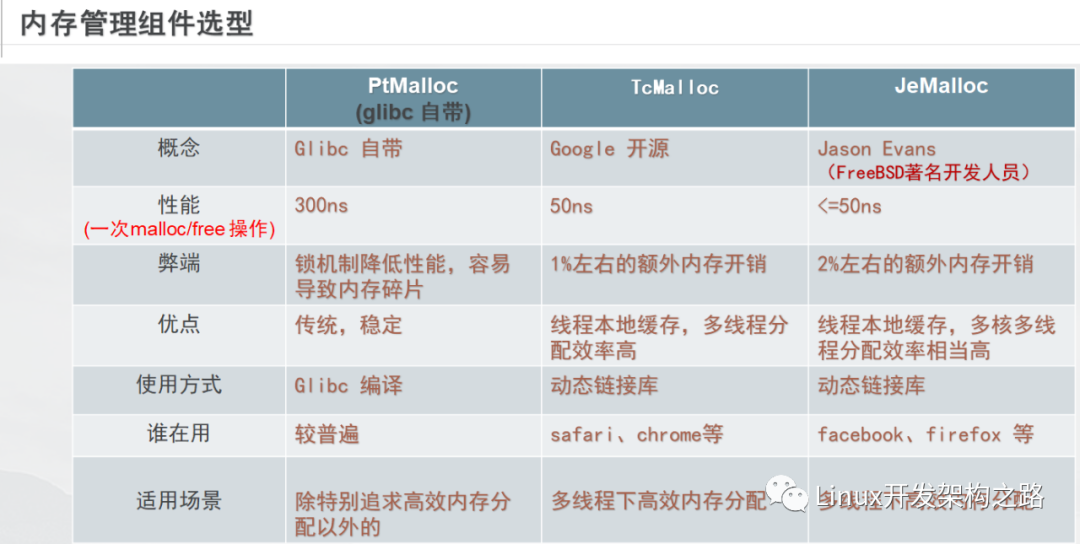

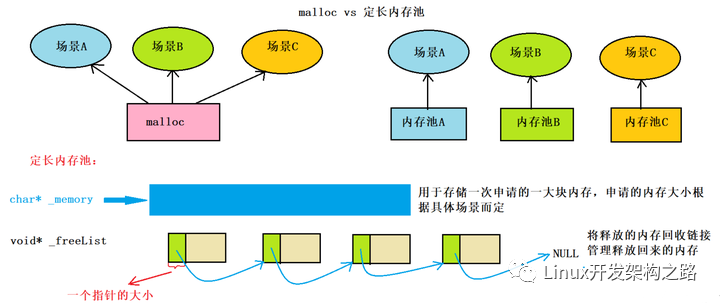

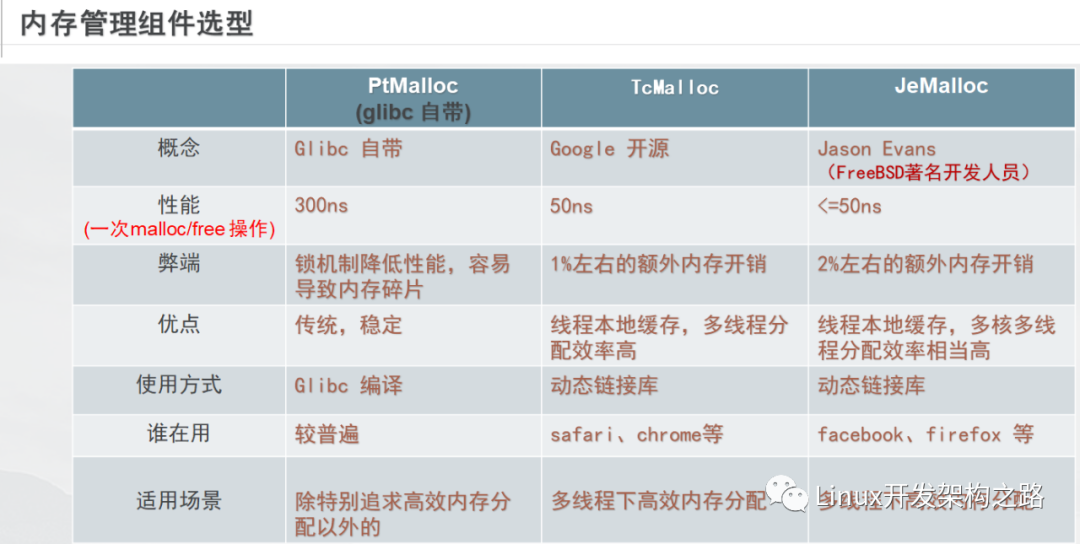

11189 同學可能會有疑問,你不是要聊技術嗎?怎么又說起消費了? 原來技術也有大眾貨以及定制品。 通用 VS 定制 作為程序員(C/C++)我們知道申請內存使用的是malloc,malloc其實就是一個通用的大眾貨,什么場景下都可以用,但是什么場景下

2021-03-02 15:29:34 4355

4355 最近在網上看到了幾篇篇講述內存池技術的文章,有一篇是有IBM中國研發中心的人寫的,寫的不錯~~文章地址在本篇blog最后。原文的講述比我的要清晰很多,我在這只是把我的一些理解和遇到的一些問題和大家分享一下~~

2022-05-20 08:58:59 5409

5409

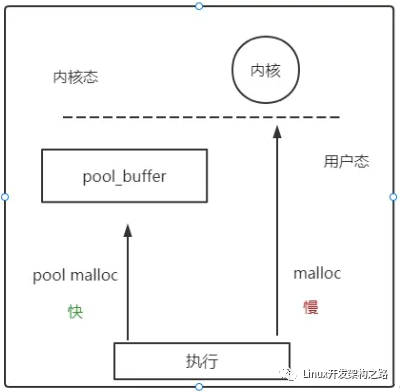

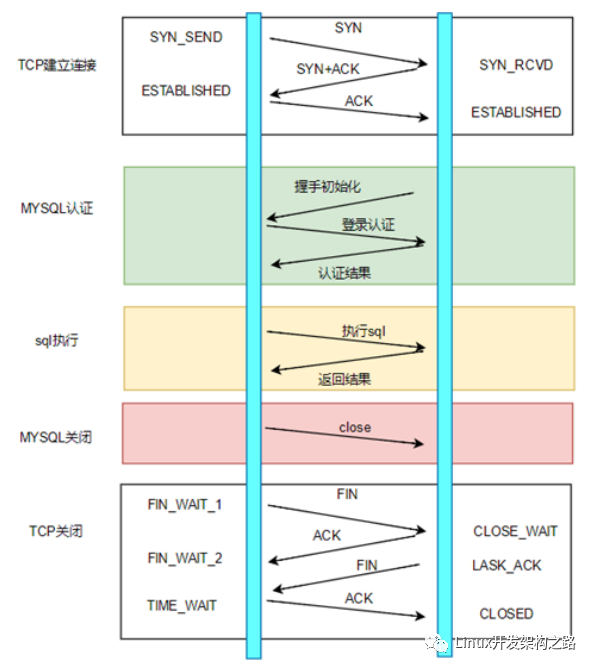

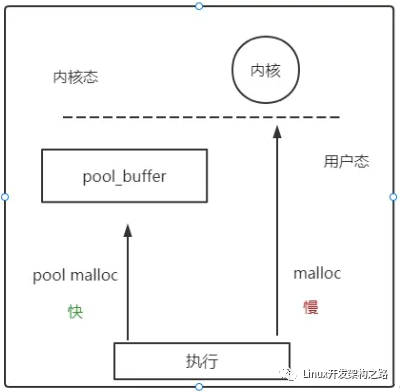

內存池是池化技術中的一種形式。通常我們在編寫程序的時候回使用 new delete 這些關鍵字來向操作系統申請內存,而這樣造成的后果就是每次申請內存和釋放內存的時候,都需要和操作系統的系統調用打交道

2022-09-23 10:22:13 1357

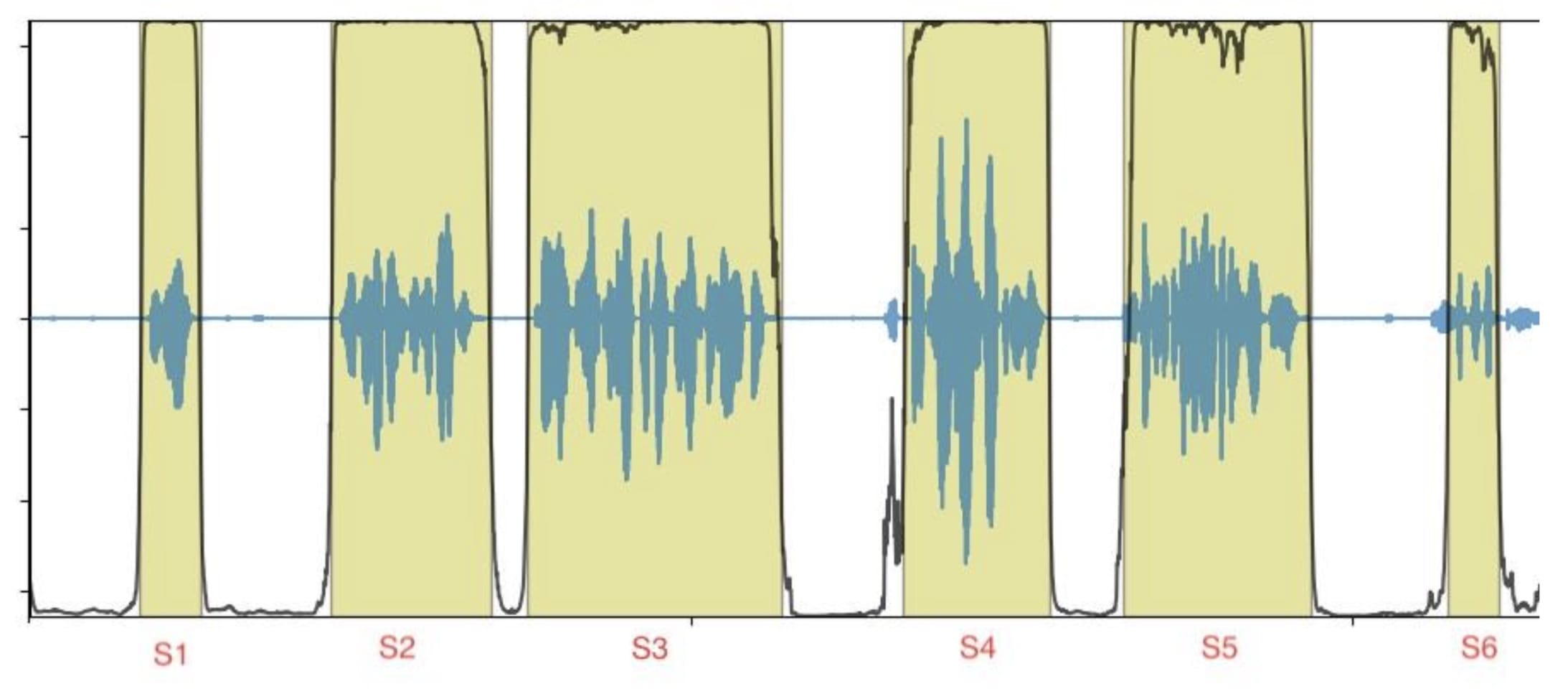

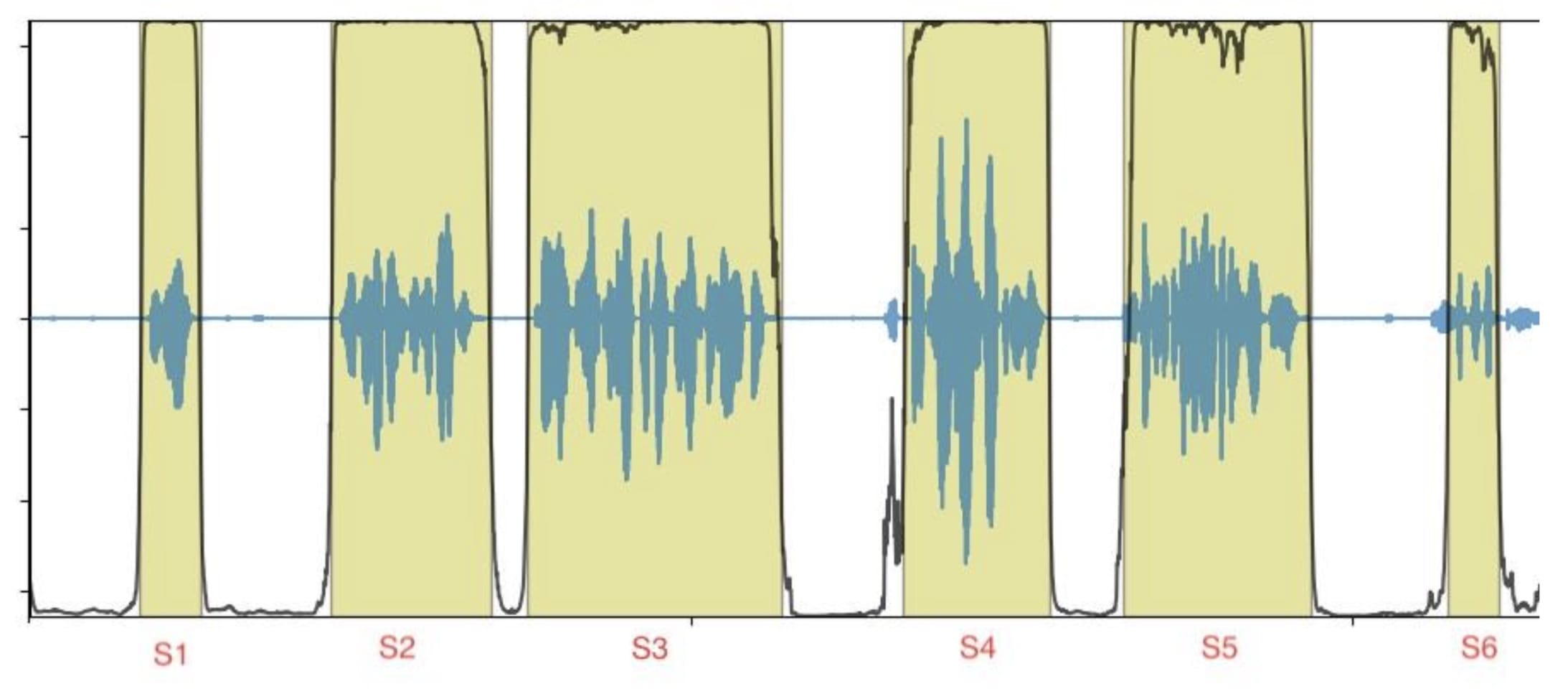

1357 鑒于KAIST的HPC根源,將DirectCXL原型放在一起的研究人員專注于使用遠程直接內存訪問(RDMA)協議將CXL內存池與跨系統直接內存訪問進行比較。

2022-09-23 10:50:26 1845

1845 隨著線程數的增加,在每個方案上運行DLRM推理都是線性的,并且斜率不同。DDR5-R1和CXL存儲器的總體趨勢相似,這與第4.3.2節中的觀察結果一致

2023-04-12 14:07:51 822

822 Compute Express Link(CXL)作為一種先進的互連技術,在當今高性能計算領域引起了廣泛關注

2023-11-29 15:26:33 8996

8996

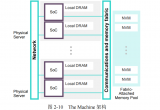

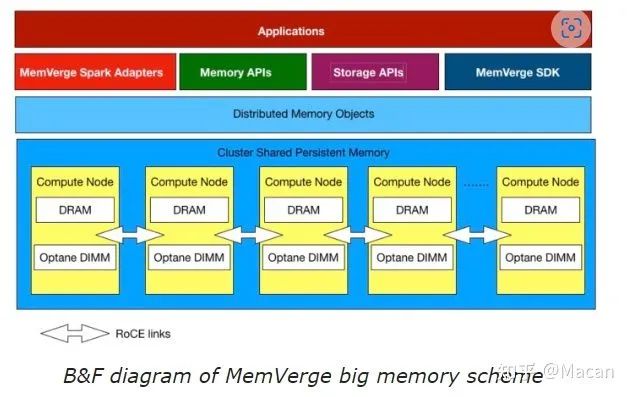

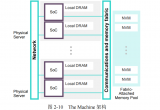

本文提出了一種基于RDMA和CXL的新型低延遲、高可擴展性的內存解耦合系統Rcmp。其顯著特點是通過CXL提高了基于RDMA系統的性能,并利用RDMA克服了CXL的距離限制。

2024-02-29 10:05:40 7471

7471

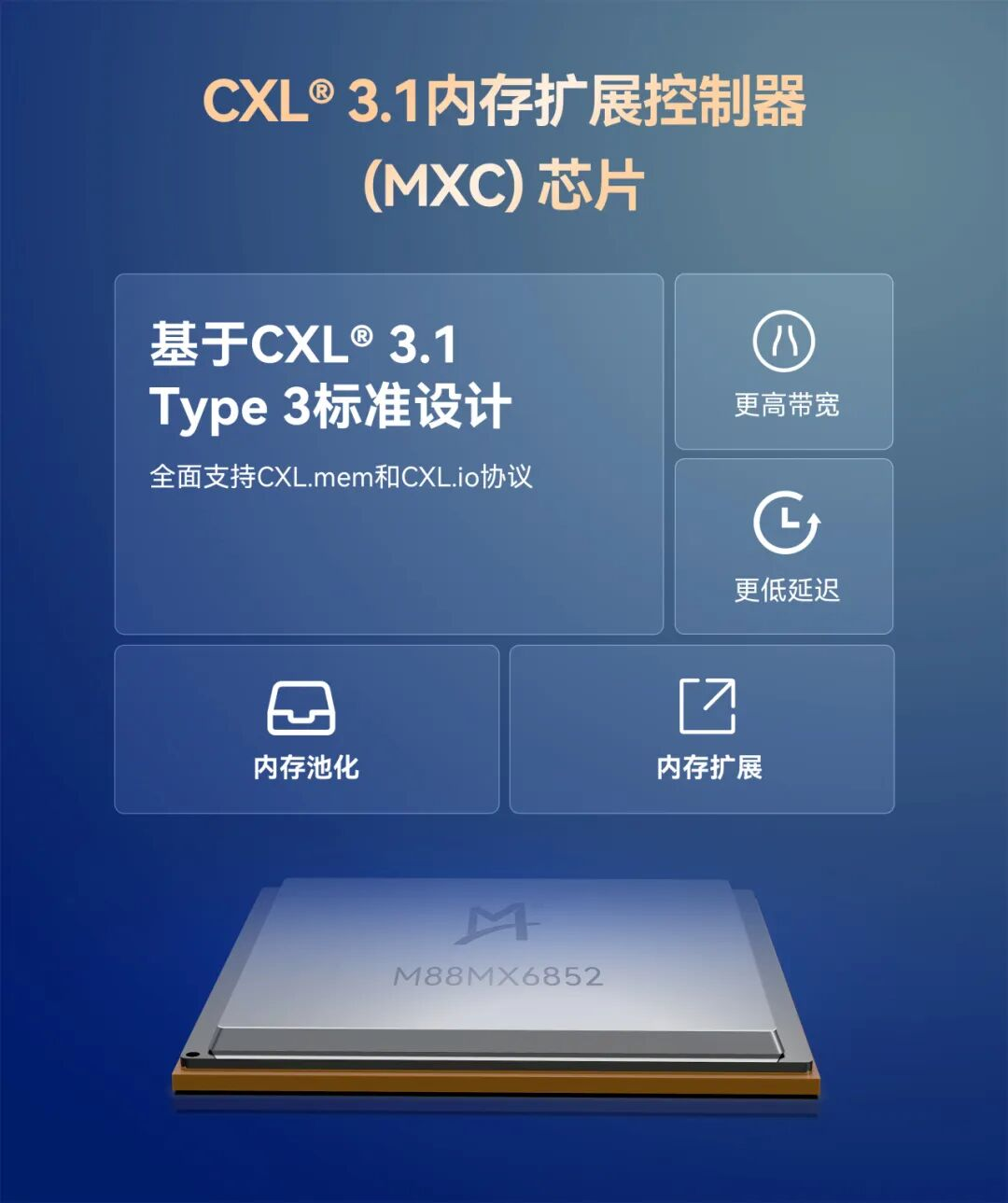

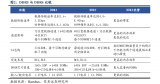

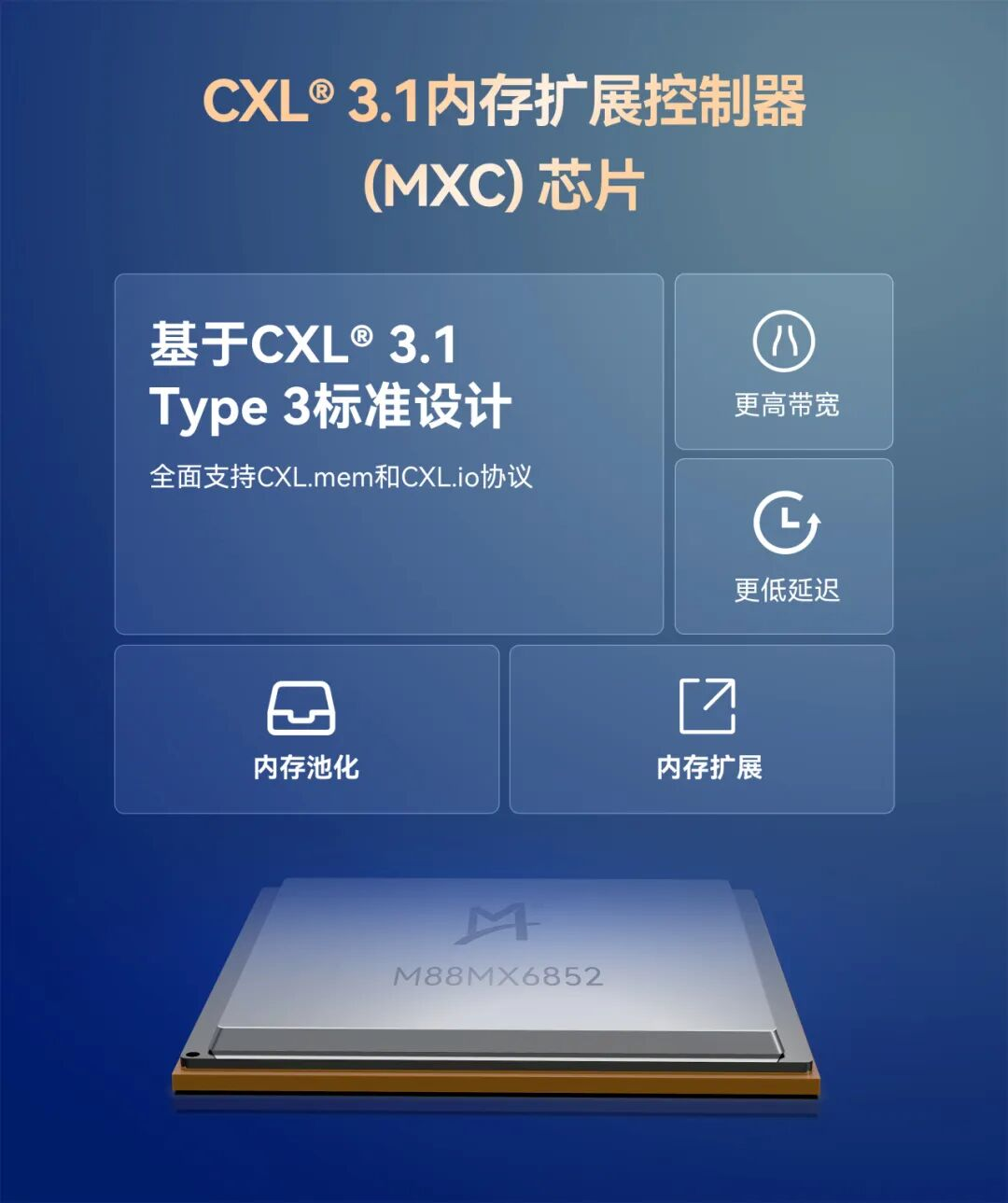

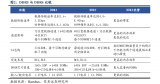

。 ? ? M88MX6852:性能卓越,滿足多元需求 ? M88MX6852芯片全面支持CXL.mem和CXL.io協議,其核心使命是為下一代數據中心服務器打造更高帶寬、更低延遲的內存擴展和池化解決方案。在數據傳輸方面

2025-09-02 09:12:00 2272

2272

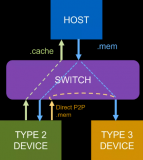

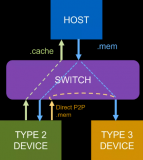

設備掛載內存的設備讀取示例如下圖,包含兩個流程分支。第一個,設備向設備掛載的內存發起讀請求,由于配置成主機偏向(圖中的紫色字體),設備要向主機發送一致性請求。主機在解析完一致性后,在CXL.mem上

2022-11-01 15:08:12

貼圖了。電源管理信用和初始化過程是本地鏈接。設備和主機之間通過CXL.io通道發送的消息類型主要涉及兩種,分別是CREDIT_RTN和AGENT_INFO,其中PM2IP是主機發給設備的電源管理消息,而

2022-10-08 15:21:40

嵌入式–內存池直接上代碼,自己體會。嵌入式設備,一般keil提供的堆很小,一般都不使用。使用內存池,自己可以調節內存大小。頭文件 malloc.h#ifndef __MALLOC_H#define

2021-12-17 07:00:49

{ //一:內存池的概念和實現原理概述//malloc:內存浪費,頻繁分配小塊內存,則浪費更加顯得明顯//“內存池...

2021-12-17 06:44:19

,整個堆有可能被弄得支離破碎,最終導致大量內存浪費。

那么這種情況下,我們解決這類問題的思路,就是創建一個內存池。

內存池,實際上就是我們讓程序創建出來的一塊額外的緩存區域,如果有需要釋放內存,先

2025-12-11 07:57:07

鑒于KAIST的HPC根源,將DirectCXL原型放在一起的研究人員專注于使用遠程直接內存訪問(RDMA)協議將CXL內存池與跨系統直接內存訪問進行比較。他們使用了一個非常老式的Mellanox

2022-11-15 11:14:59

為了更好的支持各種大內存應用,ESM3354正式推出512M(DDR3)內存版本: ESM3354-M512, ESM3354-M512的用戶應用程序可用內存在450MB左右。 ESM3354 512M內存售價請參考成都英創官網。

2016-06-12 14:02:21

,實現硬件互助、資源共享,為用戶提供流暢的全場景體驗。本期,我們通過介紹 OpenHarmony 的硬件資源池化框架,為大家揭曉 OpenHarmony 是如何實現多設備協同的。一、硬件資源訪問的演進

2022-05-23 16:42:09

memory: 5276

msh >

最大內存只能設到 32K,PsoC62 最大內存能設到多少, 如何設置??

2024-02-21 08:03:48

適合它們的高效率的內存分配算法,就將變得復雜化。RT-Thread 操作系統在內存管理上,根據上層應用及系統資源的不同,有針對性地提供了不同的內存分配管理算法。總體上可分為兩類:內存堆管理與內存池管理

2022-10-17 15:06:42

程序運行,創建一個內存池,一個申請內存任務,一個釋放內存任務,u***串口CN3打印內存分配和釋放的信息,串口波特率115200//創建內存池 Sample_mp = rt_mp_create

2022-05-10 14:51:11

本視頻為【每日一練】的第16節學習視頻,注:剛開始學習的童鞋請從第一節視頻開始打卡哦(本節視頻在下面打卡即可)學習任務:1、刪除內存池時,會首先喚醒等待在該內存池對象上的所有線程。(判斷)打卡規則詳見:第二期【每日一練】來啦,16天入門RT-Thread內核,快速上手無壓力!

2021-09-08 09:33:05

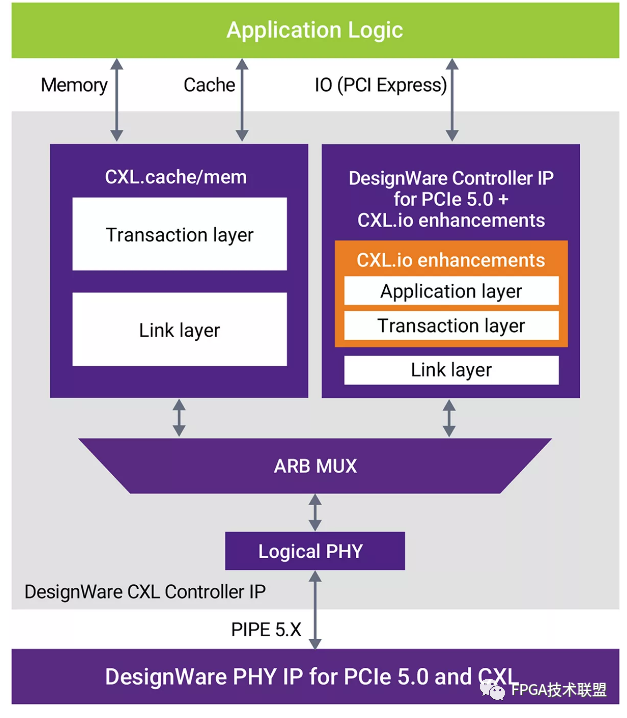

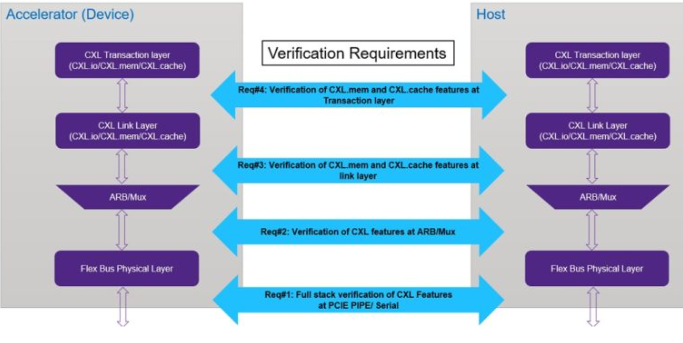

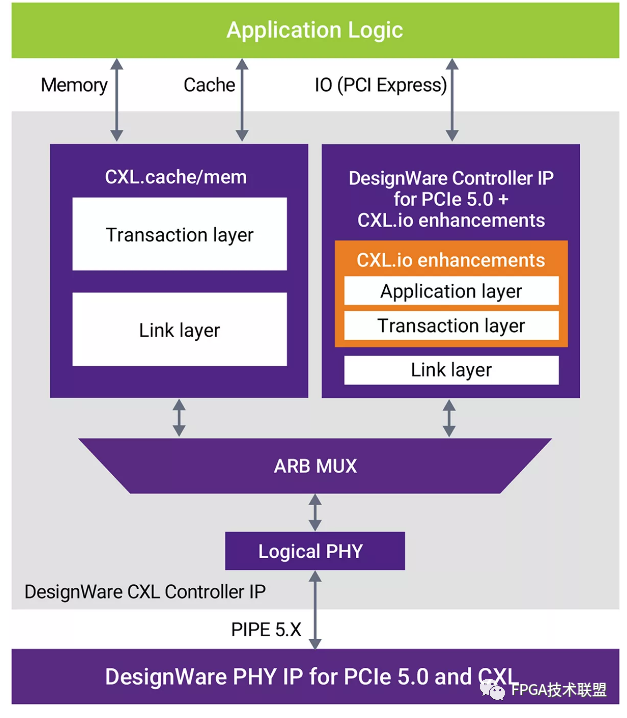

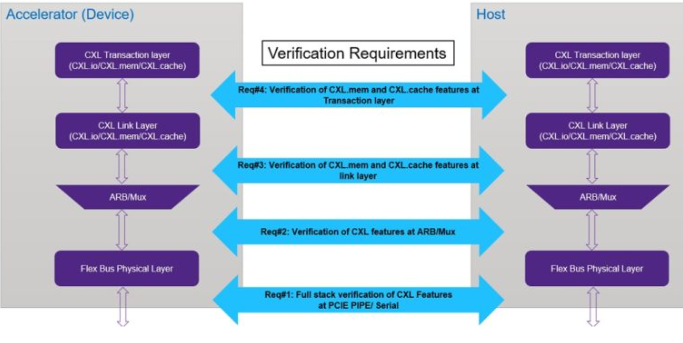

1、CXL系統架構簡析 CXL支持三種設備類型,如下圖。Type 1支持CXL.cache和CXL.io;Type2支持CXL.cache,CXL.mem和CXL.io;Type3支持

2022-09-14 14:24:52

LWIP內存占用與裁剪工具鏈:GCCLWIP版本:2.0.2 默認配置靜態內存總體分布網絡相關內存占用主要分為三個部分,其中LWIP內存池占主要部分DNS解析LWIP內存池RTT相關DNS占用DNS

2022-08-09 10:43:53

初始化完成,CXL.cache/CXL.mem鏈路層只能發送Control-Retry flit,不能發送其它類型的flit。4.2.8 CXL.cache/CXL.mem鏈路層retry當發生傳輸

2023-02-21 14:27:46

技術,主要支持一致性緩存,內存和IO擴展。CXL是基于PCIe 5.0實現的連接技術,復用了很多PCIe協議的東西,這一點上與CCIX比較像,但又不完全一樣。說起CCIX和CXL,難免要相互對比。其實

2022-09-09 15:03:06

需要使用STM32F401的大內存特性,買了1批STM32F401CCU6. QFN48封裝的。隨便翻了一下PDF,第一感覺和F103的48腳封裝差不太多,于是將F103的板子改了個QFN48的封裝

2021-08-12 07:17:26

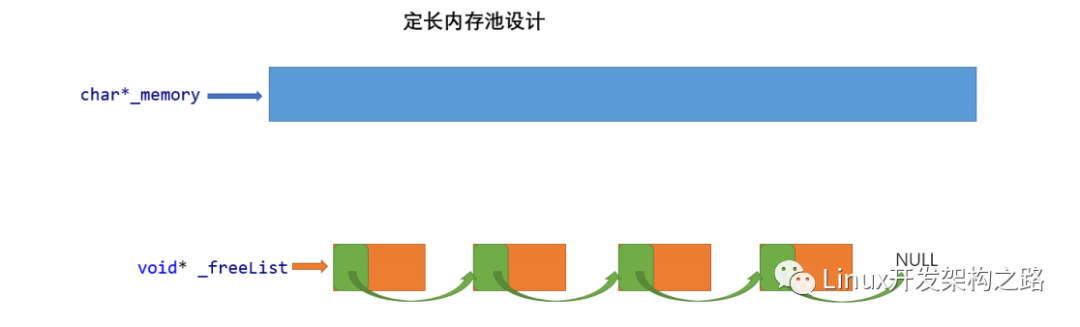

。1. 內存塊工作機制使用內存池需要以下幾個步驟:創建內存池。先向系統申請一塊大的內存。分割大內存塊。將申請成功過的大內存塊,分成多個同樣大小的小內存塊。連接小內存塊。以鏈表的形式,將各個小內存塊

2022-04-06 17:02:59

?rt_mp_detach有實際刪除的作用不?嗯。。。。具體就是,需要的時候,動態申請一塊內存作為靜態內存池,對這塊內存池作相應的初始化,然后不需要時刪除。

2022-11-22 14:42:09

請問i7 10700搭配什么主板比較好?i710700配什么顯卡和多大內存好?

2021-09-23 08:04:41

最大內存容量

2009-12-17 11:30:29 478

478 串口通訊服務器的最大內存容量 最大內存容量是指終端服務器主板能夠最大能夠支持內存的容量。一般

2010-01-07 13:58:23 714

714 遠程訪問服務器的最大內存容量 最大內存容量是指遠程訪問服務器主板能夠最大能夠支持內存的容量。

2010-01-08 14:26:26 813

813 三星將加大內存芯片資本支出并建新生產線

據韓國媒體報道,全球最大內存芯片生產商三星電子今年可能加大對內存芯片的投資,并建立一條新生產線。

2010-01-25 10:03:25 1092

1092 開放互連技術并制定相應規范,促進新興應用模式的性能突破,同時支持面向數據中心加速器和其他高速增強的開放生態系統。 CXL是一種全新突破性的高速CPU到設備和CPU到內存的開放互連技術,可實現CPU與平臺增強功能及工作負載加速器(如GPU、FPGA和其他專用加速器解決方案)之間的高速、高效互連,旨在

2019-03-14 16:38:58 434

434 內存池(Memery Pool)技術是在真正使用內存之前,先申請分配一定數量的、大小相等(一般情況下)的內存塊留作備用。當有新的內存需求時,就從內存池中分出一部分內存塊,若內存塊不夠

2019-04-02 14:32:19 518

518 的互聯技術,可實現在CPU與加速器之間建立高速的互聯生態系統(包括GPU、FPGA與特定加速器解決方案以及內存擴展設備之間的互聯)。該技術基于成熟的PCI Express架構并使用了PCI

2020-12-26 11:04:10 3582

3582 Leo CXL? Memory Accelerator 技術引領新一代服務器分層內存,解決了數據中心和云端的內存容量和帶寬瓶頸。

2021-11-23 14:39:12 2050

2050 瀾起科技今日發布全球首款CXL?(Compute Express Link?)內存擴展控制器芯片(MXC)。該MXC芯片專為內存AIC擴展卡、背板及EDSFF內存模組而設計,可大幅擴展內存容量和帶寬,滿足高性能計算、人工智能等數據密集型應用日益增長的需求。

2022-05-06 10:40:40 2131

2131 MXC芯片是一款CXL DRAM內存控制器,屬于CXL協議所定義的第三種設備類型。該芯片支持JEDEC DDR4和DDR5標準,同時也符合CXL 2.0規范,支持PCIe 5.0的速率。

2022-05-06 10:46:43 3375

3375 今日,作為先進內存技術的廠商,三星宣布開發出三星首款512GB內存擴展器 (CXL,Compute Express Link) DRAM,朝CXL的商業化邁出了重要一步,CXL將在IT系統中實現更高的內存容量且更低的延遲。

2022-05-10 10:16:08 2306

2306 、可靠性以及高性能內存擴展和池化。在對Leo智能內存控制器 (Smart Memory Controllers)與業界先進的CPU/GPU平臺以及DRAM內存模塊在各種實際工作負載上成功進行端

2022-09-01 10:44:58 1134

1134 隸屬SGH (Nasdaq: SGH) 控股集團的全球專業內存與存儲解決方案領導者 SMART Modular世邁科技 (“SMART”)宣布推出全新Compute Express Link

2022-09-01 15:38:06 2017

2017 CXL是英特爾推出的標準。在2019年,英特爾推出了CXL。CXL是高度中央處理器到設備和CPU到內存鏈接的開放標準。其推出的目的在于簡化加速器和內存擴展的互連和可擴展性。

2022-09-05 16:46:06 753

753 內存QoS遙測是內存設備的一種機制,用于在CXL.mem請求的每個響應消息中指示其當前負載級別(DevLoad)。這使主機能夠根據負載級別來衡量對部分設備、單個設備或設備組的CXL.mem請求的速率,從而優化這些內存設備的性能,同時限制結構擁塞。

2022-11-02 09:45:50 3820

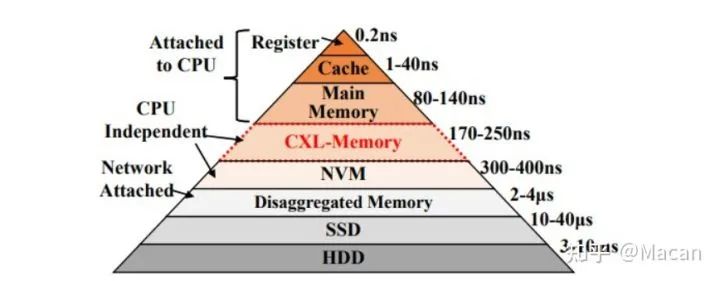

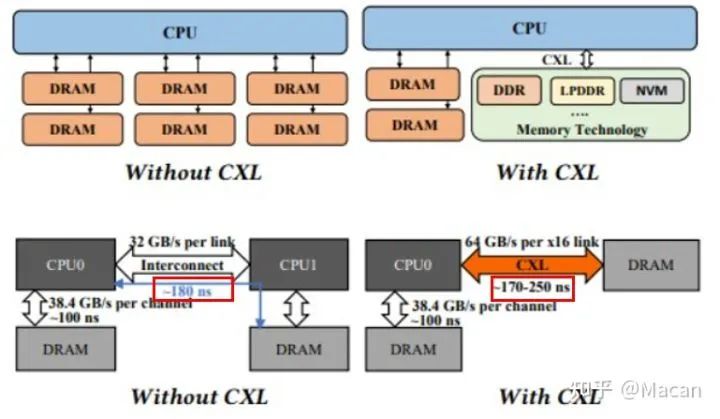

3820 以前的內存擴展嘗試都陷入了妥協,特別是在延遲方面。例如,GigaIO 表示其FabreX 架構已經可以使用 DMA 在 PCI-Express 上進行內存池化,但這樣做需要應用程序能夠容忍 500 納秒到 1.5 微秒的延遲。

2022-12-07 15:44:49 2197

2197 Marvell存儲業務事業部執行副總裁Dan Christman表示:“我們相信CXL將成為實現下一代數據中心最佳資源利用的重大變革者,而收購Tanzanite將提高我們解決客戶最具挑戰性問題的能力。”

2023-02-09 14:17:31 1572

1572 CXL全稱為Compute Express Link,作為一種全新的開放式互聯技術標準,其能夠讓CPU與GPU、FPGA或其他加速器之間實現高速高效的互聯,從而滿足高性能異構計算的要求,并且其維護CPU內存空間和連接設備內存之間的一致性。總體而言,其優勢高度概括在極高兼容性和內存一致性兩方面上

2023-02-21 15:06:54 2719

2719

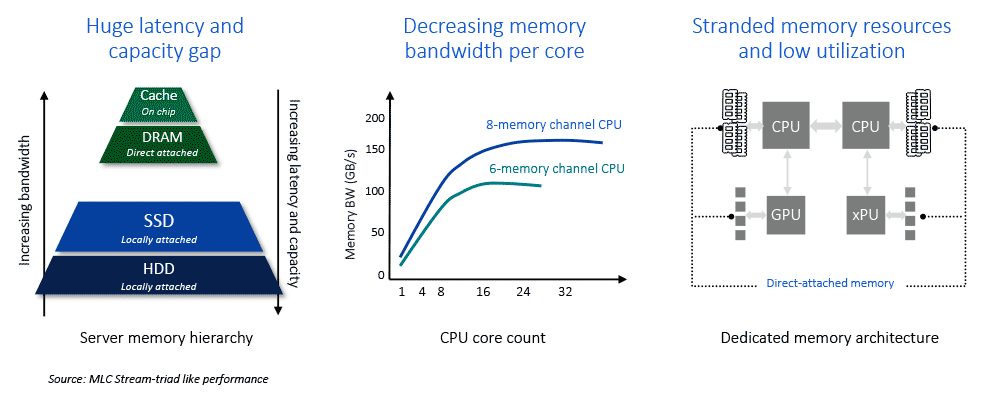

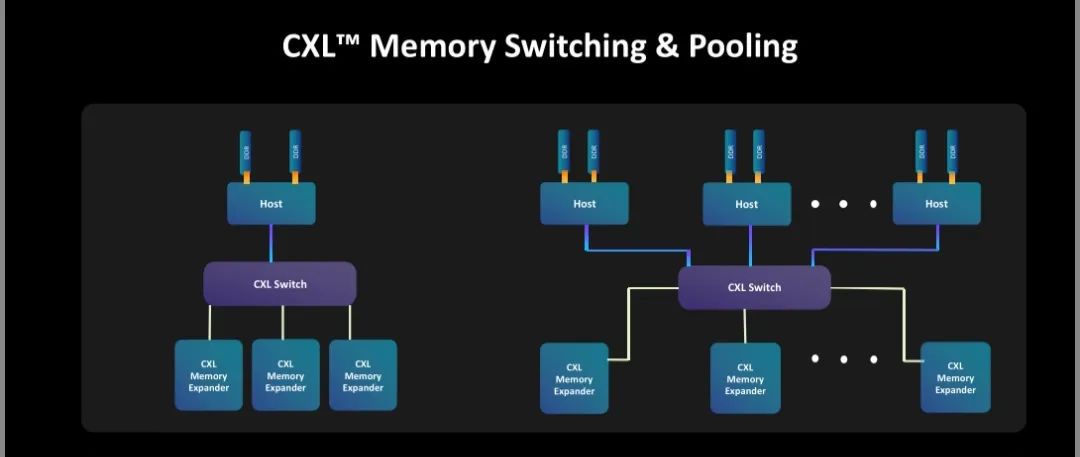

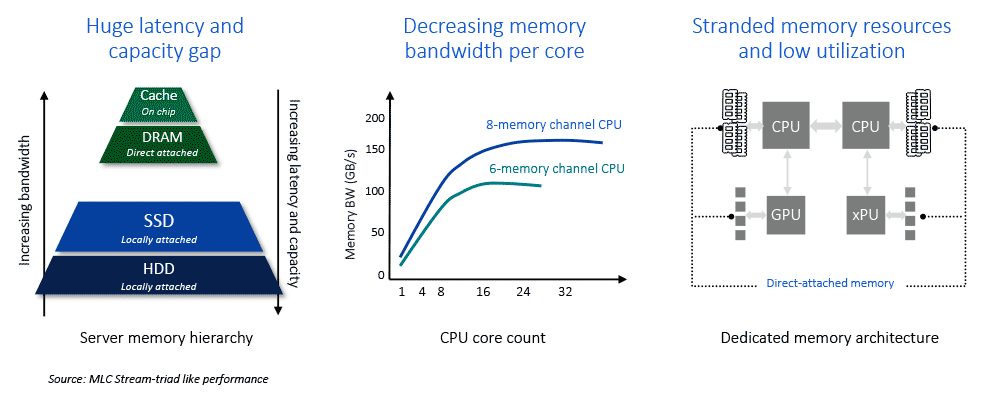

,使得處理器數量及內存頻寬達到瓶頸,舉例來說,盡管 DRAM 占服務器成本的比例高達 50%,卻受限于內存無法連接到多個 CPU 或 GPU 的架構,導致在各個時間段中約有 25% 的內存處于閑置的窘境。 Compute Express Link (CXL) 是一種用于處理器、內存擴展和加速器

2023-03-08 18:10:31 2480

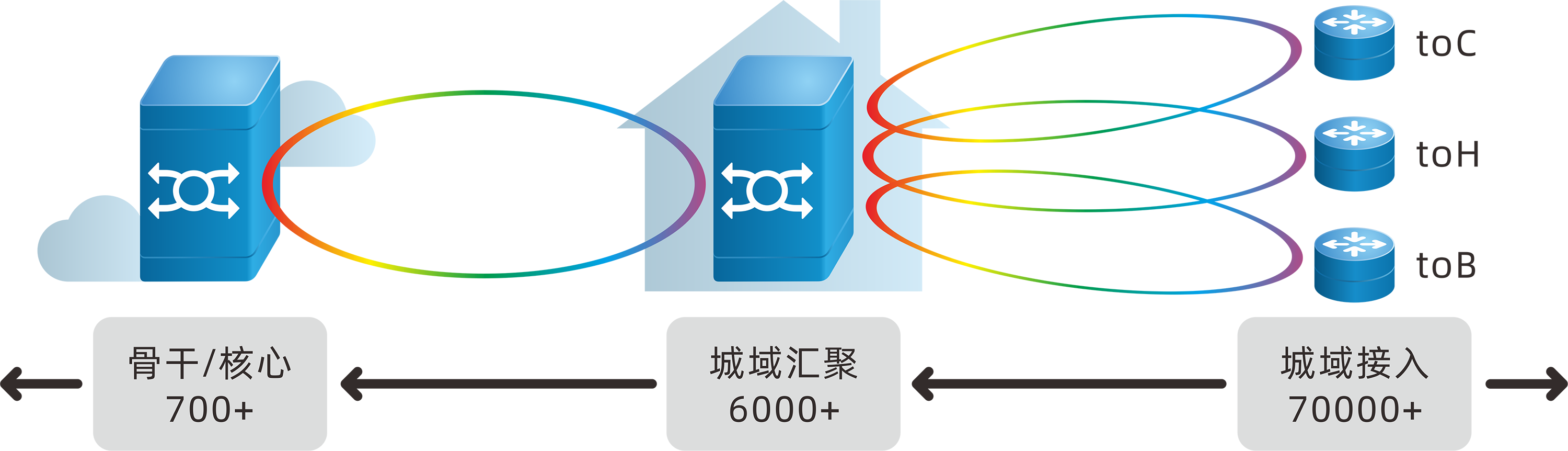

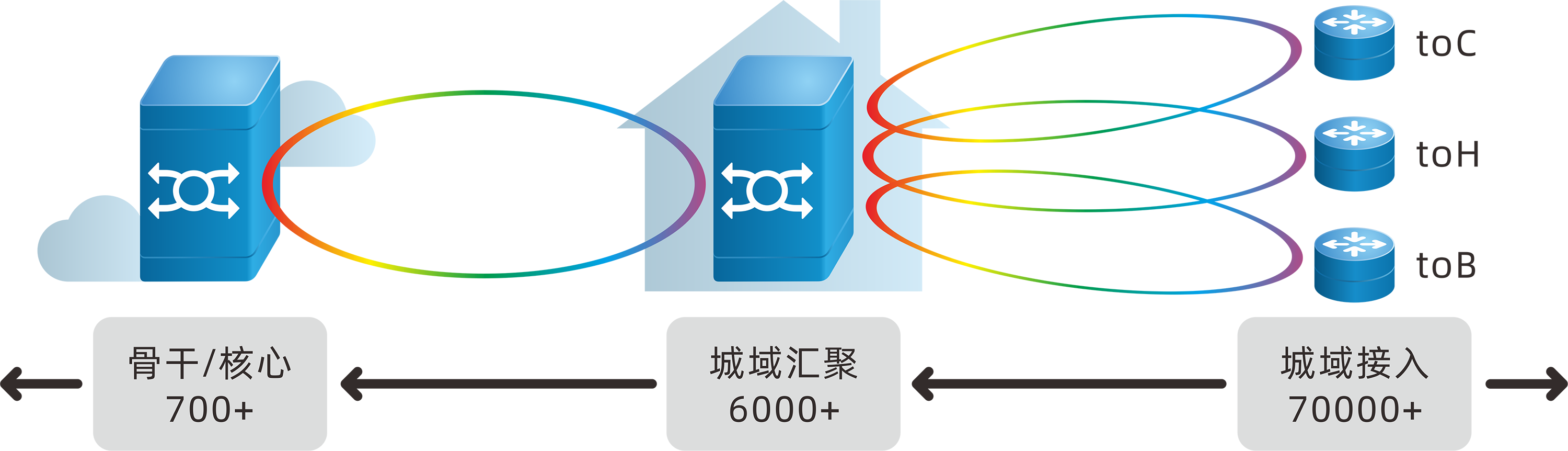

2480 中國聯通頒布了《池化波分打造城域全光底座白皮書》(下文簡稱白皮書)(文末附白皮書下載)。白皮書提出以開創性的城域池化波分解決方案,實現最優的城域ROADM+OTN全光業務網底座。

2023-04-04 16:04:46 1692

1692

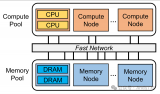

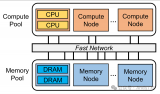

這種新產品允許服務器平臺將多個 CXL 內存組合成一個內存池,多個主機可以根據需要共享每個內存池的內存,從而使得 CXL 內存都可以被充分利用,避免出現區域閑置的情況,從而實現更高效的內存利用率。

2023-05-16 11:31:57 917

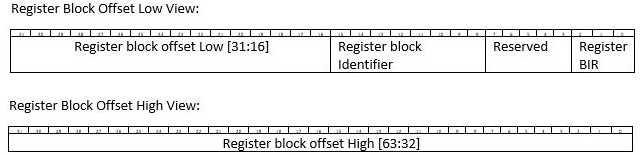

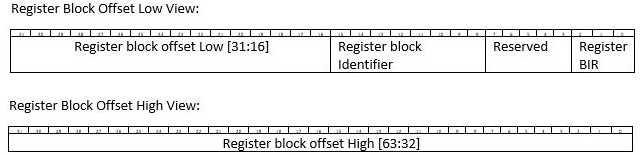

917 計算快速鏈接 (CXL) 1.1 和 CXL 2.0 規范在內存映射寄存器的放置和訪問方式上有所不同。CXL 1.1 規范將內存映射寄存器放置在 RCRB(根復合寄存器塊)中,而 CXL 2.0

2023-05-25 16:56:20 3450

3450

CXL 是一種在主機(通常是 CPU)和設備(通常是附加了內存的加速器)之間實現高帶寬、低延遲鏈接的技術。CXL 堆棧專為低延遲而設計,使用 PCIe 電氣和附加卡的標準 PCIe 外形規格。CXL 使用靈活的處理器端口,可以自動協商到標準 PCIe 事務協議或備用 CXL 事務協議。

2023-05-26 10:33:11 4804

4804

版圖文件很大,需要處理的數據量非常大,但本身的邏輯判斷并不復雜,所以通常不剛需高主頻機型,但要求多核、大內存的機器。CPU與內存的比例通常能達到1:4或1:8,極端情況下這個比例會更高,2T或4T的超大型內存機器都有可能登場。

2023-08-02 15:22:52 1576

1576

近日,瀾起科技的CXL內存擴展控制器(MXC)芯片成功通過了CXL聯盟組織的CXL1.1合規測試,被列入CXL官網的合規供應商清單。瀾起科技是全球首家進入CXL合規供應商清單的MXC芯片廠家

2023-08-18 09:14:38 1899

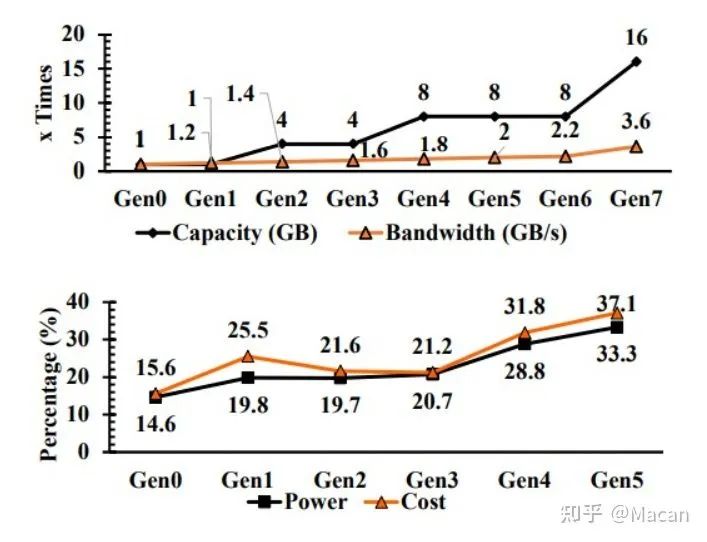

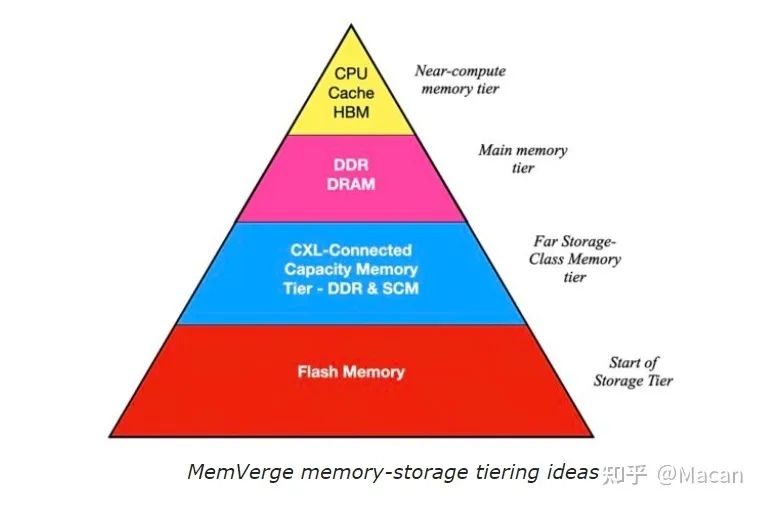

1899 隨著第一代芯片的發布,圍繞CXL的早期炒作逐漸被現實的性能期望所取代。與此同時,關于內存分層的軟件支持正在不斷發展,借鑒了NUMA和持久內存方面的先前工作。最后,運營商已經部署了RDMA以實現存儲分離和高性能工作負載。由于這些進步,主內存分離現在已經成為可能。

2023-08-22 09:33:25 7293

7293

CXL 增加了芯片內部的技術復雜性,這需要集成電路(IC)和復雜的片上系統(SoC)專業知識來設計、開發和執行復雜的 SoC。在 CXL 存儲器解決方案方面處于強勢地位。目前 Rambus 正在銷售 CXL 相關解決方案,有望在 CXL 技術領域拓展營收新增長點。

2023-08-24 09:44:50 1638

1638

LibTorch-based推理引擎優化內存使用和線程池

2023-08-31 14:27:09 2065

2065

CXL – CXL 提供了大幅擴展內存容量和提高帶寬的機會,同時還從處理器中抽象出內存類型。通過這種方式,CXL 為整合新的內存技術提供了一個很好的接口。CXL 內存控制器提供處理器和內存之間的轉換層,允許在本地連接的內存之后插入新的內存層。

2023-09-25 13:00:19 937

937 :CXL技術可以將CPU、GPU、FPGA等計算設備與內存直接連接,避免了傳統的I/O總線帶來的時延,從而實現更低的延遲,提高了計算效率。

2023-09-27 09:26:03 7395

7395

NetDAM 實現的存算資源互聯系統,CPU、DSA、存儲等資源可以通過AXI、CHI或PCIe/CXL等總線直連到NetDAM,不同 NetDAM 之間通過以太網互聯,NetDAM 上的內存資源形成共享池。

2023-10-09 10:18:55 2767

2767

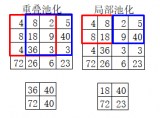

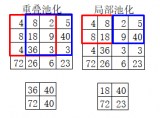

卷積神經網絡的最基本結構有卷積層跟池化層,一般情況下,池化層的作用一般情況下就是下采樣與像素遷移不變性。根據步長區分,池化可以分為重疊池化與區域池化,圖示如下:

2023-10-21 09:42:53 2071

2071

CXL的目標:解決CPU和設備、設備和設備之間的內存鴻溝。服務器有巨大的內存池和數量龐大的基于PCIe運算加速器,每個上面都有很大的內存。內存的分割已經造成巨大的浪費、不便和性能下降。CXL就是為解決這個問題而誕生。

2023-10-30 14:30:31 10270

10270

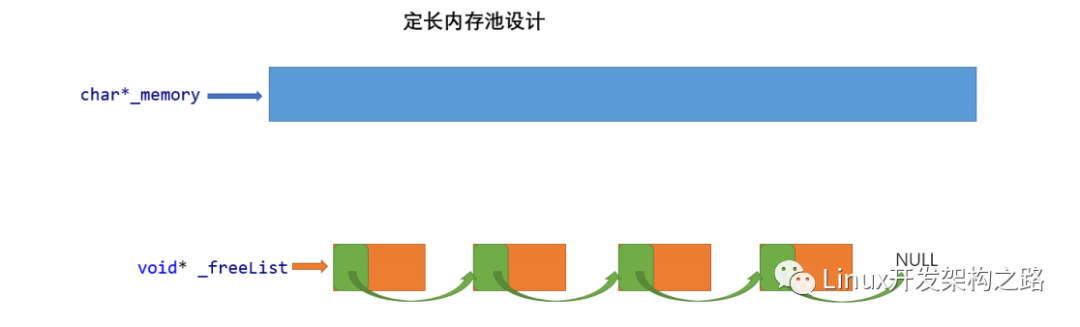

1什么是內存池 1.1池化技術 所謂“池化技術”,就是程序先向系統申請過量的資源,然后自己管理,以備不時之需。之所以要申請過 量的資源,是因為每次申請該資源都有較大的開銷,不如提前申請好了,這樣

2023-11-08 16:26:08 1818

1818

相關知識 1、池化技術 池化技術就是程序先向系統申請過量的資源,并將這些資源管理起來,避免頻繁的申請和釋放資源導致的開銷。 內存池可以使用池化技術來維護可用內存塊的鏈表。當程序需要分配內存時,內存池會從鏈表中分配一個可用的內存塊。

2023-11-09 11:16:57 1379

1379

池化技術 池化技術能夠減少資源對象的創建次數,提?程序的響應性能,特別是在?并發下這種提?更加明顯。使用池化技術緩存的資源對象有如下共同特點: 對象創建時間長; 對象創建需要大量資源; 對象創建后

2023-11-09 14:44:55 2150

2150

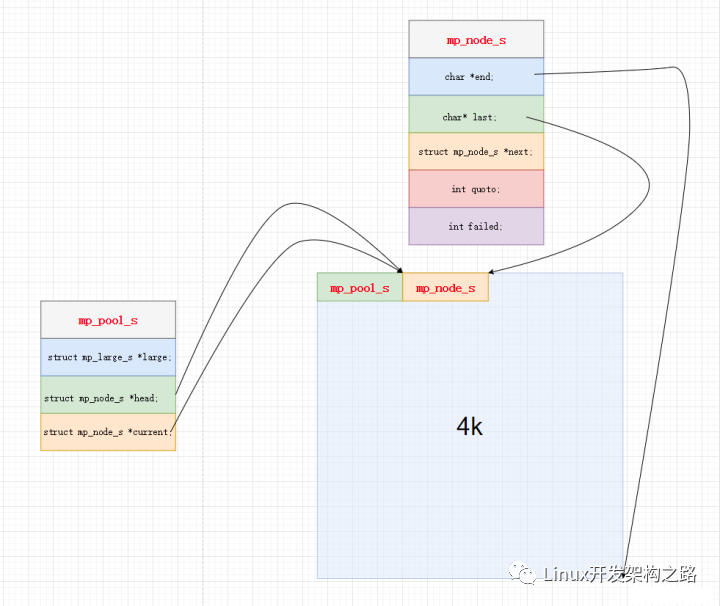

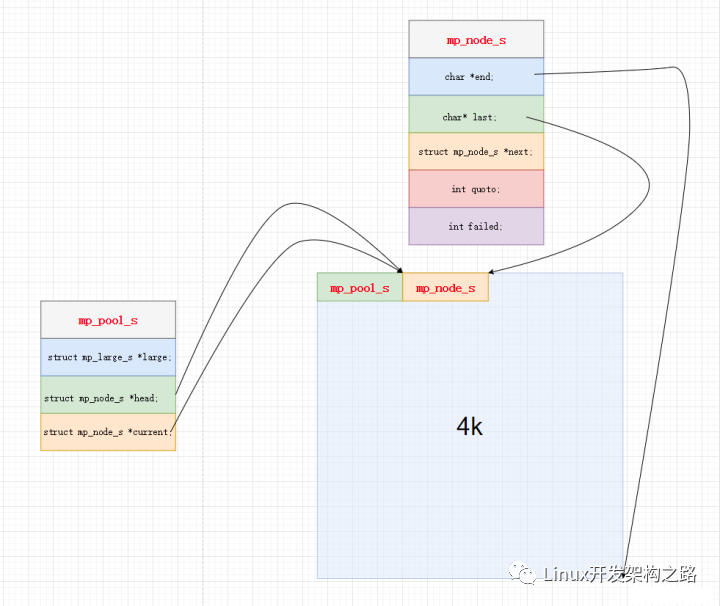

寫在前面 本文的內存池代碼是改編自Nginx的內存池源碼,思路幾乎一樣。由于Nginx源碼的變量命名我不喜歡,又沒有注釋,看得我很難受。想自己寫一版容易理解的代碼。 應用場景 寫內存池的原理之前

2023-11-10 11:11:19 1263

1263

為什么要用內存池 為什么要用內存池?首先,在7 * 24h的服務器中如果不使用內存池,而使用malloc和free,那么就非常容易產生內存碎片,早晚都會申請內存失敗;并且在比較復雜的代碼或者繼承的屎

2023-11-10 17:19:26 1399

1399

造輪子內存池原因引入 作為C/C++程序員, 相較JAVA程序員的一個重大特征是我們可以直接訪問內存, 自己管理內存, 這個可以說是我們的特色, 也是我們的苦楚了. java可以有虛擬機幫助管理內存

2023-11-13 11:51:42 1148

1148

內存池的定義 1.池化技術 池 是在計算機技術中經常使用的一種設計模式,其內涵在于:將程序中需要經常使用的核心資源 先申請出來,放到一個池內,由程序自己管理,這樣可以提高資源的使用效率,也可以保證本

2023-11-13 15:23:11 1533

1533

作為一名Java開發人員,池化技術或多或少在業務代碼中使用。常見的包括線程池、連接池等。也是因為Java語言超級豐富的基建,基本上這些池化能力都有著相對成熟的“工具”。

2023-11-24 10:22:16 1044

1044

作為一名Java開發人員,池化技術或多或少在業務代碼中使用。常見的包括線程池、連接池等。也是因為Java語言超級豐富的基建,基本上這些池化能力都有著相對成熟的“工具”。

2023-11-24 10:22:19 2458

2458

CXL憑借其統一的接口標準,通過PCIe接口連接各類處理器如CPU、GPU及內存設備,有效解決了當前系統在速度、延遲和可擴展性上所面臨的瓶頸。

2023-12-27 10:45:45 949

949 三星與知名開源軟件解決方案供應商紅帽合作,突破性地實現了CXL技術在實際用戶場景中的驗證。此次重大進展將為全球企業客戶提供更強大的算力支持,實現硬件更新,無需大幅調整。讓我們共同期待CXL生態系統以新的速度持續拓展。

2023-12-27 11:22:28 1054

1054 近日,國內知名存儲器制造企業佰維科技股份有限公司(以下簡稱“佰維”)欣然宣告,其在DRAM技術領域取得了重要突破——成功研發并量產了符合CXL 2.0規范的CXL DRAM內存擴展模塊。這不僅對于我國信息技術創新有著重大意義,更是對于全球存儲器市場產生了積極影響。

2023-12-27 11:41:00 1332

1332 三星透露,近期與開源軟件巨頭紅帽達成深度合作,在現實的用戶環境中首次證明了 Compute Express Link ?(CXL)內存技術的可行性,此舉預計會極大拓展三星的 CXL技術生態圈。受益于生成式人工智能、自動駕駛以及內存數據庫(IMDB)等

2023-12-27 15:25:25 1308

1308 近日,三星電子聯合紅帽(Red Hat)共同完成重大技術里程碑——在實際用戶環境中全面驗證CXL( Compute Express Link )內存擴展平臺的運作。此次成功標志著三星CXL生態系統的進一步擴張,也意味著未來有望為廣大數據中心用戶帶來更多便捷和高效服務。

2023-12-27 15:47:47 1229

1229 近日,三星電子與業界領先的操作系統供應商Red Hat共同取得了一項重要突破。雙方已成功有效地驗證了CXL內存擴展技術的互操作性,成功實現了在實際應用場景中的一次重大突破,這不僅有助于推動企業計算領域的蓬勃發展,也將為廣大客戶帶來更多元化的選擇。

2023-12-27 15:49:35 1035

1035 三星電子與開源軟件巨頭紅帽(RedHat)聯手,完成了在實際用戶環境中的CXL(ComputeExpressLink)內存操作;此舉系業內首次,將進一步擴大其 CXL 生態系統。

2023-12-27 15:56:20 1244

1244 三星電子發布公告稱,已與 Red Hat 合作,在真實用戶環境中成功驗證了 CXL (Compute Express Link) 內存操作;此舉系業內首次,將進一步擴大其 CXL 生態系統。

2023-12-28 09:35:27 1326

1326 CXL因具備強大的接口功能,實現了CPU、GPU以及內存之間的快速連接,被廣泛應用于生成式人工智能、自動駕駛及內存數據庫等項目。利用現有的設備體系,CXL可大幅度地提高速度、降低延遲并增強系統的可擴展性。

2024-01-04 11:46:25 870

870 CXL的目標:解決CPU和設備、設備和設備之間的內存鴻溝。服務器有巨大的內存池和數量龐大的基于PCIe運算加速器,每個上面都有很大的內存。內存的分割已經造成巨大的浪費、不便和性能下降。CXL就是為解決這個問題而誕生。

2024-01-11 16:53:38 4096

4096

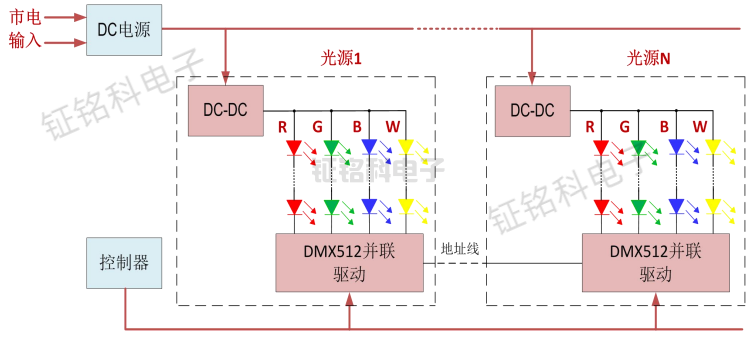

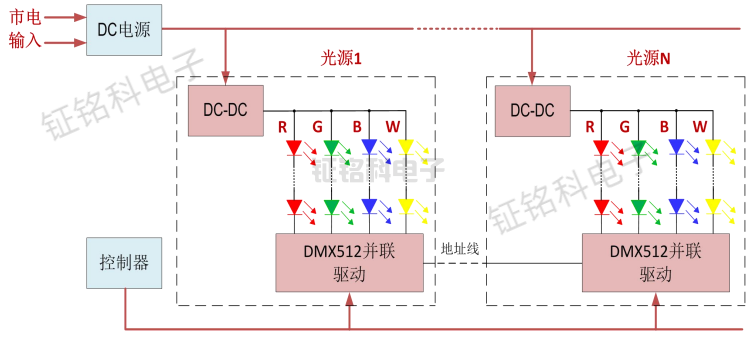

LED樹木燈光亮化方案的設計與控制技術解析

2024-01-24 17:54:50 1539

1539

站群服務器的內存需求取決于網站的數量和流量,以及服務器需要運行的應用和服務。RAKsmart小編為您整理發布站群服務器需要多大內存以及站群服務器內存需求的考慮因素。

2024-03-04 09:48:08 890

890 ,實現大規模量產和交付。隨著AI的快速發展,計算密集型工作負載對存儲的低延遲、高帶寬提出了前所未有的高要求。ComputeExpressLink(CXL)互連技術為

2024-03-28 08:19:20 1567

1567

、大吞吐量的浮點運算。在此背景下,江波龍日前在CFMS2024展出了一款基于Compute Express Link (CXL)技術的創新內存擴展設備——CXL 2.0 AIC內存擴展卡,為計算機系統提供

2024-04-17 14:40:01 1203

1203

。其中,池化層(Pooling Layer)作為CNN的重要組成部分,在降低模型復雜度、提高計算效率以及增強模型的不變性和魯棒性方面發揮著關鍵作用。本文將從多個方面深入探討池化層的作用,力求全面解析其在CNN中的核心地位。

2024-07-03 15:58:02 4631

4631 、內存緩沖區、智能網絡接口卡、持久存儲器和固態驅動器等設備之間的開放式行業標準互連接口。CXL基于PCIe靈活的數據帶寬提供了緩存一致性和存儲語義,同時實現比PCIe低得多的延時。

2024-08-02 14:43:28 1811

1811

今日,領先的高速互聯芯片及方案設計廠商國數集聯發布業界首創的CXL混合資源池(Compute Express Link Hybrid Resource Pool ,以下簡稱“CHRP”)參考設計。該

2024-08-06 14:19:33 893

893

10月15日最新消息,研華科技(Advantech)于昨日正式揭曉了其最新研發的SQRAM CXL 2.0 Type 3 內存模塊——SQR-CX5N。該模塊遵循EDSFF E3.S 2T標準,擁有

2024-10-15 15:28:24 1333

1333 近日,瀾起科技在CXL(Compute Express Link)技術領域取得了又一重要里程碑。其自主研發的CXL?內存擴展控制器(MXC)芯片成功通過了CXL 2.0合規性測試,并被列入CXL聯盟

2025-01-21 14:44:08 1597

1597 商名單。 這一重要里程碑不僅標志著SMART Modular在CXL技術領域的領先地位,更是對其長期以來致力于高質量、高兼容性內存解決方案的肯定。CXL作為一種高性能、低延遲的互連技術,正在逐漸

2025-02-05 15:59:11 750

750 近日,全球領先的整合型內存與儲存解決方案提供商SMART Modular世邁科技(隸屬于Penguin Solutions?集團)宣布,其4-DIMM和8-DIMM CXL?(Compute

2025-02-14 10:15:17 760

760 Compute Express Link(CXL)于2019年首次發布,是處理器與AI加速器、內存緩沖區、智能網絡接口卡、持久性存儲器和固態驅動器等設備之間的開放式行業標準互連技術。作為一種行業標準

2025-03-11 15:07:48 1048

1048

。無論您是高級自適應 SoC 開發人員,還是 CXL 初學者,第二代 Versal Premium 系列都能提供靈活的 CXL 3.1 子系統,非常適合內存擴展、內存池化和內存加速應用。

2025-04-24 14:52:03 1066

1066

下一代數據中心服務器提供更高帶寬、更低延遲的內存擴展和池化解決方案。 瀾起科技CXL 3.1內存擴展控制器采用PCIe? 6.2物理層接口,支持最高64 GT/s的傳輸速率(x8通道),并具備多速率

2025-09-01 10:56:40 648

648 產品方案(產品型號:SCX201D5E2256G3H0156F01/SCX201PME2256G2H0132F01),榮獲“年度CXL產品技術創新獎”。這一榮譽充分體現了業界對公司技術領先性與產品化能力的高度認可。

2025-11-19 17:07:03 1722

1722

AI、科學計算、海量內存處理……這些硬核工作負載正在不斷挑戰系統極限。而 FPGA 異軍突起,成為了實現高效數據傳輸的“關鍵推手”。想知道怎么在不改變整體架構的前提下,讓帶寬和能效實現“雙飛躍”?答案就藏在壓縮 IP 與基于 CXL(Compute Express Link)的解決方案里。

2025-12-19 09:43:20 195

195

.cache和CXL.memory三個子協議,分別處理I/O、緩存一致性和內存訪問。PCIe物理層為CXL高效的數據傳輸提供技術底座,CXL.cache和CXL.mem

2024-08-18 00:02:00 6455

6455

電子發燒友App

電子發燒友App

評論